#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

Design and Practical Implementation

of Efficient Power-Factor-Corrected

Switching Regulators

Based on Reduced Redundant Power

Processing Principle

#### Martin Kin Ho CHEUNG

Department of Electronic and Information Engineering, The Hong Kong Polytechnic University, Hung Hom, Hong Kong.

Thesis Submitted for the Degree of Master of Philosophy

August 2002

To my parents

### Abstract

Abstract of the thesis entitled 'Design and Practical Implementation of Efficient Power-Factor-Corrected Switching Regulators Based on Reduced Redundant Power Processing Principle' submitted by Martin Kin Ho CHEUNG for the degree of Master of Philosophy at The Hong Kong Polytechnic University in August 2002

Power-factor-corrected switching regulators effectively eliminate the current harmonic distortions of the AC mains, associated with large non-linear loads, capacitive loads, and inductive loads from the electric machinery and electronic systems. Switching regulators with power factor correction (PFC) and fast voltage regulation are constructed by two simple converters with an energy storage element. Simple and typical power-factor-corrected switching regulators are connected with their the converters and the storage element serially. The main drawback of this approach is that the efficiency of these arranged switching regulators is inevitably reduced by the two power processing stages, the two simple converters. To solve the efficiency problem, non-cascaded switching regulators are proposed. Unlike the typical power-factor-corrected switching regulators, the non-cascaded power-factor-corrected switching regulators allow part of the input power to be processed by only one power stage, thereby reducing the amount of power redundantly processed by the two constituent power stages. Unfortunately, industry has been slow to appreciate and exploit the considerable advantages of the non-cascaded power-factor-corrected switching regulators. There seem to be the reason for that: the lack of detail, systematic comparison, and practical information on the non-cascaded powerfactor-corrected switching regulators. The objective of this study is to fill this gap by providing a well-organized compendium of useful information for

the switching regulator design engineers who want to understand the practical detail of the non-cascaded power-factor-corrected switching regulators for accomplishing an optimal in their designs. Two non-cascaded power-factor-corrected switching regulators have been constructed and tested for validating the reduced-redundant-power-processing (R<sup>2</sup>P<sup>2</sup>) principle. A rigorous and detail comparison of the switching regulators output power level, circuit complexity, components stress, and control methodological are reported.

## Acknowledgements

I would like to give my sincere thank to Dr. H. L. Chow, my chief supervisor, for his valuable advice, patient guidance and support which made this study possible. His immense enthusiasm on researching is greatly appreciated. I would also like to express my gratitude to Prof. C. K. Tse, my second supervisor, for his support and constructive comments, that will never be forgotten.

I would like to thank Dr. Y. M. Lai for his helpful suggestions and discussions. Also, I wish to thank Mr. C. P. Lee for his kind assistance in performing the experimental tests.

I will be forever grateful to my colleagues who have imparted direct assistance on me during the course of my study. In particular, I would like to convey my heartfelt thanks to Dr. Herbert H. C. Iu, Dr. K. W. Siu, Mr. J. Feng, Mr. T. M. Leung, Mr. D. C. Lu, Mr. V. Pjevalica, and Mr. L. P. Wong for their incessant support and inspiration. It has been a very enjoyable experience working with them.

I gratefully acknowledge the Research Committee of The Hong Kong Polytechnic University for its financial support during the entire period of my candidature.

Last, but not least, I must thank my parents, my sister, my brother, and my friends for their love and care over the years.

## Contents

| Al | bstrac | t        |                                                 | ii |

|----|--------|----------|-------------------------------------------------|----|

| 1  | Intr   | oductio  | n                                               | 1  |

|    | 1.1    | Motiv    | ation and Objectives                            | 1  |

|    | 1.2    | Litera   | ture Review                                     | 2  |

|    | 1.3    | Objec    | tives of the Thesis                             | 5  |

|    | 1.4    | Outlin   | ne of the Thesis                                | 5  |

| 2  | Revi   | iew of F | Power Factor and PFC Circuits and Techniques    | 6  |

|    | 2.1    | Power    | Factor                                          | 6  |

|    |        | 2.1.1    | Time-Domain Interpretation                      | 6  |

|    |        | 2.1.2    | Vector-Algebra Interpretation                   | 7  |

|    |        | 2.1.3    | Power Factor for Sinusoidal Voltage             | 8  |

|    | 2.2    | Input    | Capacitor Filter                                | 10 |

|    | 2.3    | Active   | Power Factor Corrector                          | 11 |

|    | 2.4    | Basic    | Requirements of Active PFC Switching Regulators | 13 |

|    |        | 2.4.1    | Pre-Regulator                                   | 14 |

|    |        |          | 2.4.1.1 Buck Pre-Regulator                      | 14 |

|    |        |          | 2.4.1.2 Boost Pre-Regulator                     | 15 |

|    |        |          | 2.4.1.3 Buck-Boost Pre-regulator                | 16 |

|    |        | 2.4.2    | Voltage Regulator                               | 18 |

|   |      | 2.4.3     | Energy S   | torage Element                                                       | 18 |

|---|------|-----------|------------|----------------------------------------------------------------------|----|

|   | 2.5  | Contro    | l Methods  | s for Pre-Regulator                                                  | 20 |

|   | 2.6  | Non-Ca    | ascaded A  | active PFC Switching Regulators                                      | 24 |

|   | 2.7  | Summa     | ary        |                                                                      | 27 |

| 3 | Inpu | ıt-Side N | Non-Casca  | ded PFC Switching Regulator                                          | 28 |

|   | 3.1  | Report    | ed Non-ca  | ascaded Input-Side Converter: "Zeta Converter"                       | 29 |

|   | 3.2  | Specific  | cations of | ISPFC                                                                | 30 |

|   | 3.3  | Realiza   | tion of IS | PFCs                                                                 | 30 |

|   | 3.4  | Analys    | is of ISPF | °C                                                                   | 32 |

|   |      | 3.4.1     | Gain of E  | Efficiency                                                           | 34 |

|   |      | 3.4.2     | Voltage a  | nd Current Rating of Semiconductor Devices .                         | 37 |

|   | 3.5  | Circuit   | Impleme    | ntation Overview                                                     | 38 |

|   | 3.6  | Design    | Procedure  | es                                                                   | 39 |

|   |      | 3.6.1     | Defining ( | Component Values                                                     | 40 |

|   |      | 3.6.2     | Control le | oop Parameters                                                       | 43 |

|   |      |           | 3.6.2.1    | Current Error Amplifier of Buck-Boost Converter                      | 43 |

|   |      |           | 3.6.2.2    | Voltage Error Amplifier of Buck-Boost Converter                      | 45 |

|   |      |           | 3.6.2.3    | Control of Two-Switch Forward Converter                              | 47 |

|   |      | 3.6.3     | Practical  | Issues for the ISPFC                                                 | 47 |

|   | 3.7  | Results   | for Valida | ating R <sup>2</sup> P <sup>2</sup> Principle and Experimental Wave- |    |

|   |      |           |            |                                                                      | 50 |

|   | 3.8  | Summa     | ry         |                                                                      | 59 |

| 1 | Outp | out-Side  | Non-Case   | caded PFC Switching Regulator                                        | 60 |

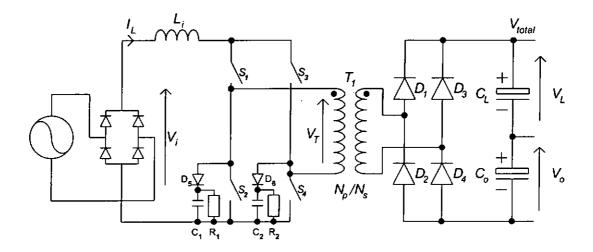

|   | 4.1  | Operati   | on Princi  | ple of OSPFCs                                                        | 61 |

|   | 4.2  | Specific  | ations of  | the Proposed OSPFC                                                   | 63 |

|   | 4.3  | Circuit   | Overview   |                                                                      | 63 |

|     | 4.4     | Connection of Proposed OSPFC                              | 64 |

|-----|---------|-----------------------------------------------------------|----|

|     | 4.5     | Maximum Efficiency Gain                                   | 66 |

|     | 4.6     | Value of the Storage Element                              | 68 |

|     | 4.7     | Pre-Regulator:                                            |    |

|     |         | Isolated-Boost Full-Bridge Converter                      | 69 |

|     | 4.8     | Voltage Regulator: Buck-Boost Converter                   | 73 |

|     | 4.9     | Implementation                                            | 75 |

|     | 4.10    | Experimental Results                                      | 75 |

|     | 4.11    | Summary                                                   | 81 |

| 5   | Feat    | ures of Non-Cascaded PFC Switching Regulators             | 82 |

|     | 5.1     | Summarization of Possible Non-Cascaded PFC Switching Reg- |    |

|     |         | ulators                                                   | 84 |

|     | 5.2     | Comparison of Two Non-Cascaded PFC Switching Regulators . | 85 |

|     |         | 5.2.1 Pre-Regulator Comparisons                           | 86 |

|     |         | 5.2.2 Voltage Regulator Comparisons                       | 89 |

|     | 5.3     | Features of Two Non-Cascaded PFC Switching Regulators     | 90 |

|     |         | 5.3.1 Conventional Cascaded Configuration                 | 91 |

|     |         | 5.3.2 Non-Cascaded ISPFC Configuration                    | 91 |

|     |         | 5.3.3 Non-Cascaded OSPFC Configuration                    | 92 |

|     | 5.4     | Summary                                                   | 93 |

| 6   | Conc    | lusion and Future Research                                | 94 |

|     | 6.1     | Contributions of the Thesis                               | 95 |

|     | 6.2     | Suggestions for Future Improvement                        | 97 |

| Bil | bliogra | aphy                                                      | 98 |

| Pu  | blicat  | ions 1                                                    | 08 |

## List of Figures

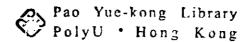

| 1.1  | Classification of power factor correction methods                                                                                                                              | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

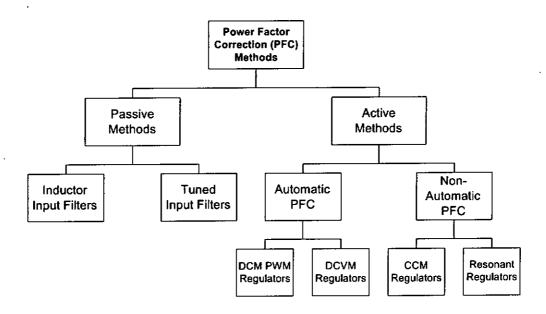

| 2.1  | (a) The phasor diagram of the AC mains connecting with an capacitive load; (b) Power triangle.                                                                                 | 7  |

| 2.2  | A simple input capacitor filter circuit for AC-DC power supply.                                                                                                                | 10 |

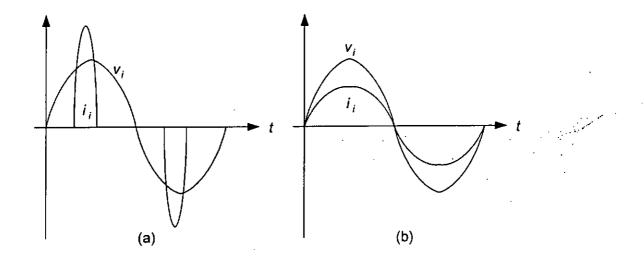

| 2.3  | (a) A simple input capacitor filter circuit line voltage and line current waveforms; (b) The voltage and the current waveforms of the AC mains directly connect to a resistor. | 11 |

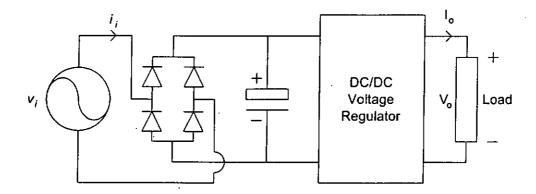

| 2.4  | A typical active power factor corrector with an energy storage element                                                                                                         | 12 |

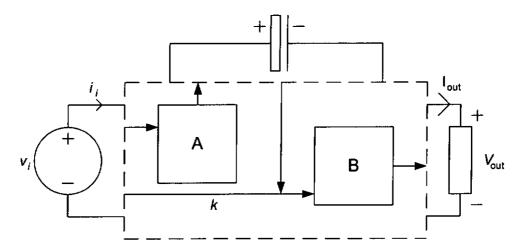

| 2.5  | A block diagram of the common active power-factor-corrected switching regulator connection.                                                                                    | 12 |

| 2.6  | Three-port diagram for active power-factor-corrected switching regulator.                                                                                                      | 13 |

| 2.7  | Buck pre-regulator.                                                                                                                                                            | 14 |

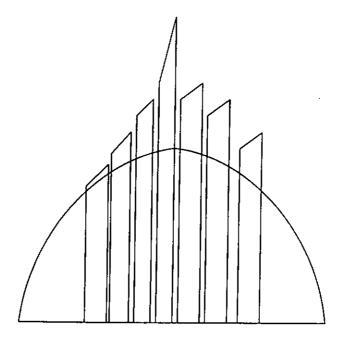

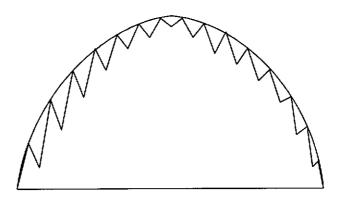

| 2.8  | Switch current in buck pre-regulator                                                                                                                                           | 15 |

| 2.9  | Flyback pre-regulator.                                                                                                                                                         | 16 |

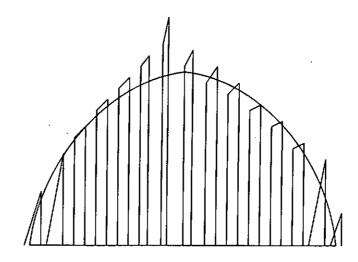

| 2.10 | Switch current in flyback pre-regulator.                                                                                                                                       | 17 |

| 2.11 | Switch current in flyback operated in DCM pre-regulator                                                                                                                        | 17 |

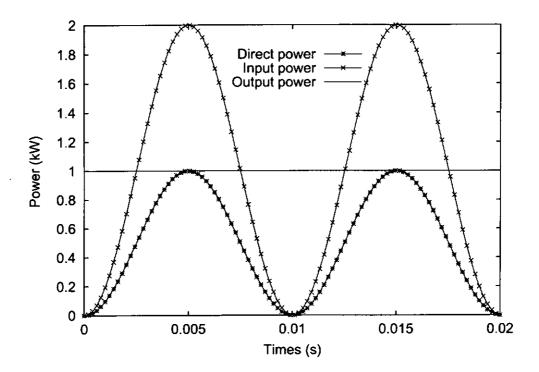

| 2.12 | Power waveforms for ideal active power-factor-corrected switching regulator at line frequency equal 50 Hz                                                                      | 19 |

| 2.13 | CCM boost pre-regulator under current-mode control simplify circuit.                                                                                                           | 20 |

|      |                                                                                                                                                                                |    |

| 2.14 | Boost pre-regulator line current waveform under average current mode control                                                                     |   | 21 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 2.15 | Boost pre-regulator line current waveform applies peak current mode control                                                                      |   | 22 |

| 2.16 | Boost pre-regulator line current waveform using variable hysteretic current mode control.                                                        |   | 23 |

| 2.17 | Boost pre-regulator line current waveform using borderline current mode control.                                                                 |   | 24 |

| 2.18 | Power flow diagram for cascaded active power-factor-corrected switching regulator.                                                               | · | 24 |

| 2.19 | Power flow diagram for input-side non-cascaded power-factor-corrected switching regulator                                                        |   | 25 |

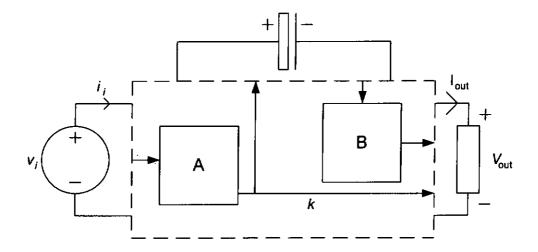

| 2.20 | Power flow diagram for output-side non-cascaded power-factor-corrected switching regulator                                                       | 4 | 26 |

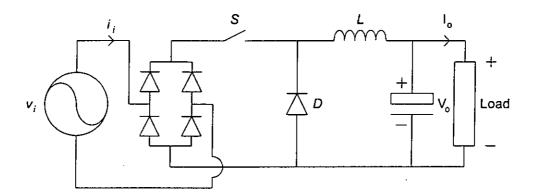

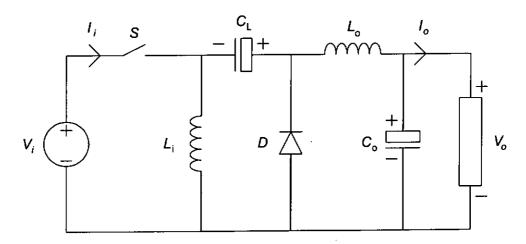

| 3.1  | 'Non-isolated zeta converter'                                                                                                                    | 2 | 29 |

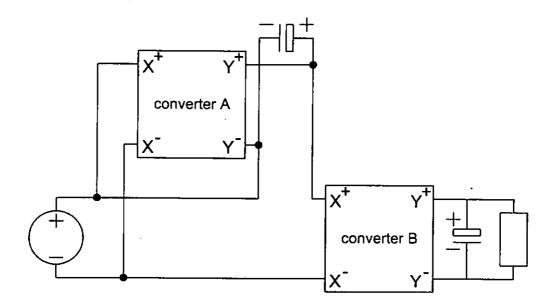

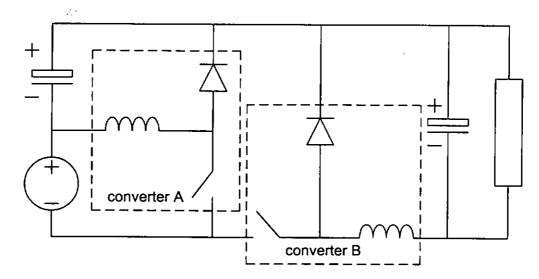

| 3.2  | Equivalent circuit of ISPFC. Rectangular blocks denote converters.                                                                               | ŕ | 31 |

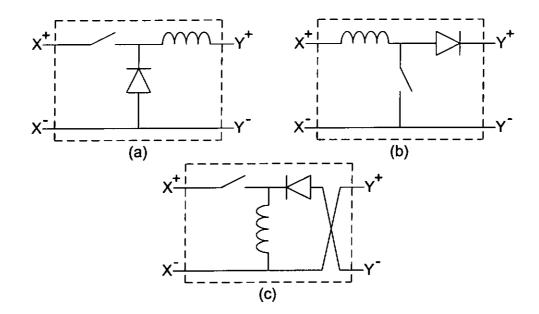

| 3.3  | Basic voltage converter circuits (a) Buck; (b) Boost; (c) Buck-Boost                                                                             |   | 32 |

| 3.4  | A possible solution for non-isolated ISPFC using a buck-boost converter and a buck converter for converter A and converter B.                    | Ş | 33 |

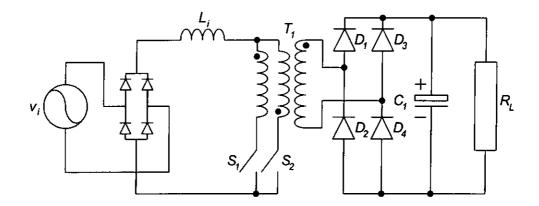

| 3.5  | Isolated ISPFC using a buck-boost converter and a forward converter for converter A and converter B (Core reset arrangement omitted for brevity) | 3 | 4  |

| 3.6  | Average model for pre-regulator of the input-side non-cascaded power-factor-corrected switching regulator                                        | 3 | 5  |

| 3.7  | A schematic representation of the reverse power flow diagram in ISPFC                                                                            | 3 | 6  |

| 3.8  | Simplified schematic circuit of ISPFC.                                                                                                           | 3 | 8  |

| 3.9  | A simplified schematic current error amplifier circuit of the av-                                                                                                                                                                                                      |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | erage current mode control for ISPFC                                                                                                                                                                                                                                   | 43 |

| 3.10 | Buck-boost pre-regulator bode plot                                                                                                                                                                                                                                     | 45 |

| 3.11 | Simplified circuit of voltage error amplifier of the PFC controller                                                                                                                                                                                                    | 46 |

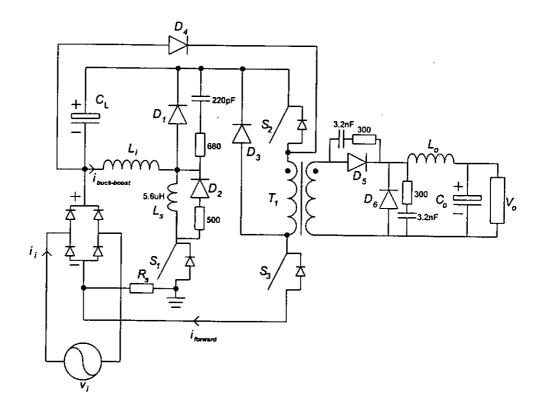

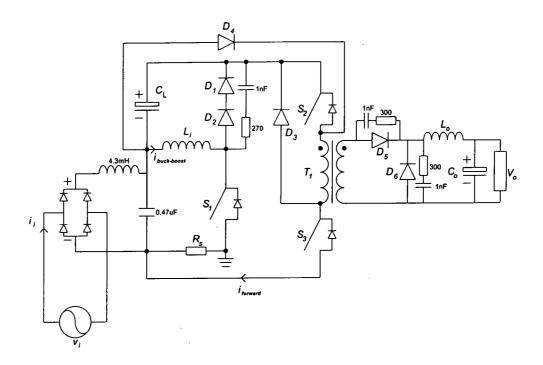

| 3.12 | Completed circuit of ISPFC                                                                                                                                                                                                                                             | 48 |

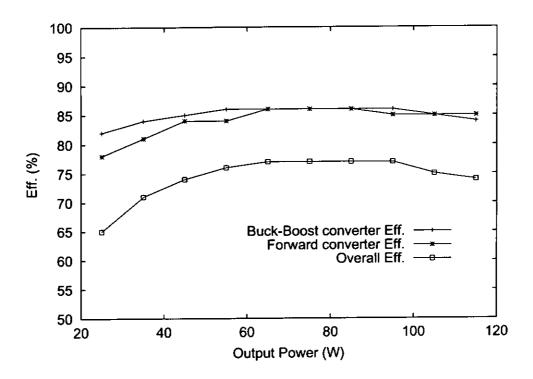

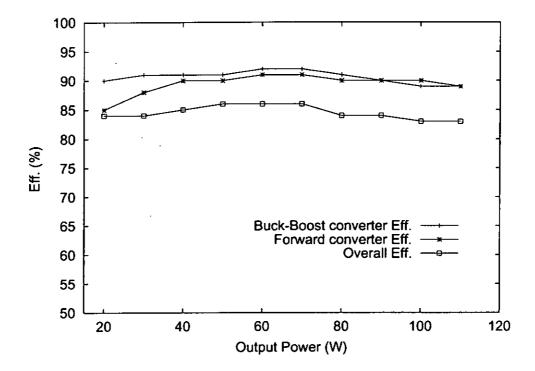

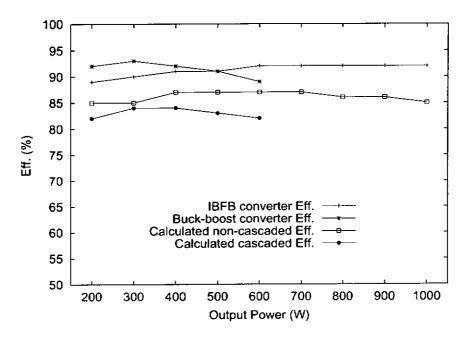

| 3.13 | The efficiency curves for the buck-boost converter, the two-switch forward converter, and ISPFC at 160 V capacitor voltage.                                                                                                                                            | 50 |

| 3.14 | A new rearranged circuit of ISPFC for getting high efficiency .                                                                                                                                                                                                        | 51 |

| 3.15 | The new rearranged circuit efficiency curves for the buck-boost converter, the two-switch forward converter, and ISPFC at 160 V capacitor voltage.                                                                                                                     | 52 |

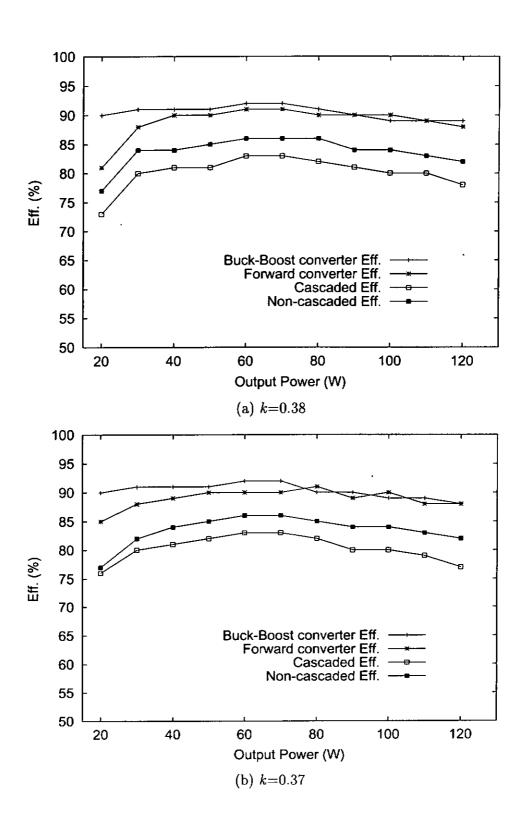

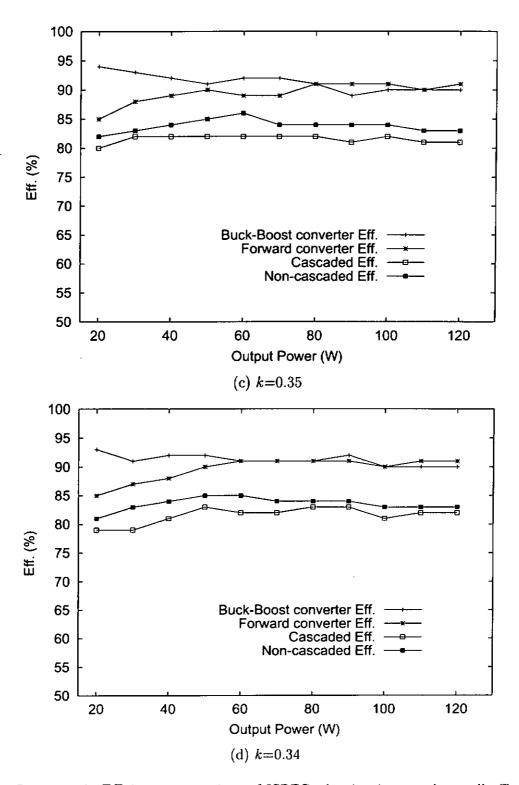

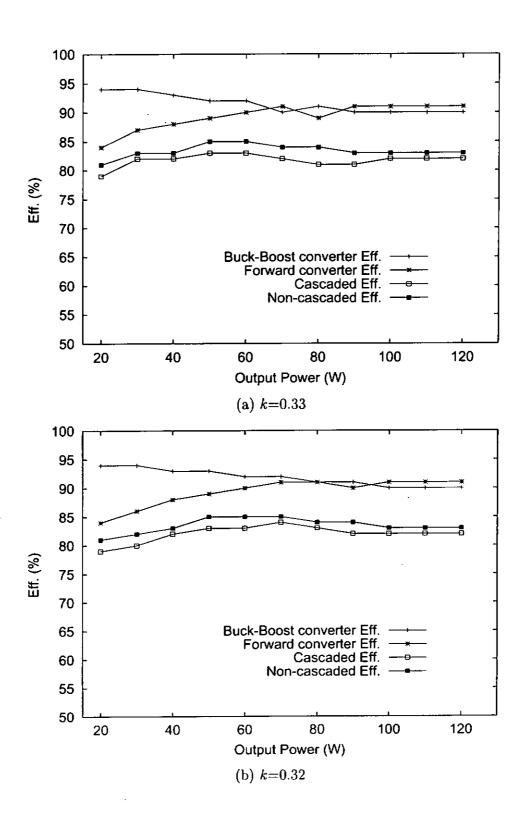

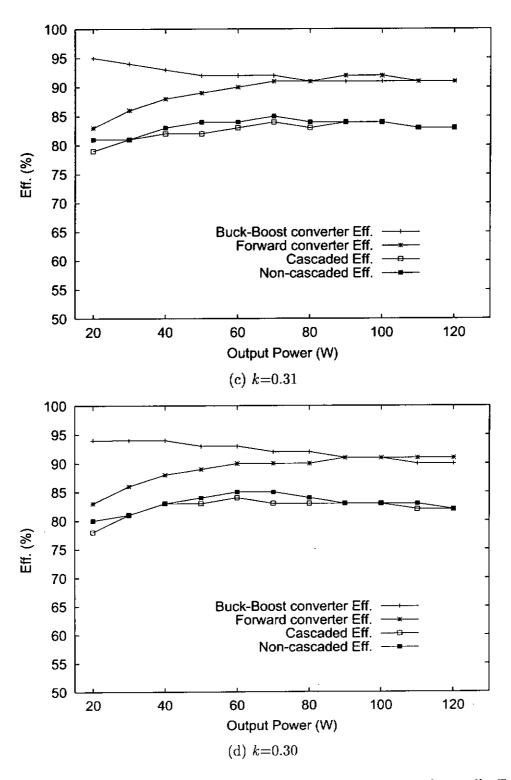

| 3.16 | Efficiency comparison of ISPFC, showing improved overall efficiency over a cascade structure for (a) $V_L$ =160 V; (b) $V_L$ =170 V; (c) $V_L$ =180 V; (d) $V_L$ =190 V                                                                                                | 54 |

| 3.17 | Efficiency comparison of ISPFC, showing improved overall efficiency over a cascade structure for (a) $V_L$ =200 V; (b) $V_L$ =210 V; (c) $V_L$ =220 V; (d) $V_L$ =230 V                                                                                                | 56 |

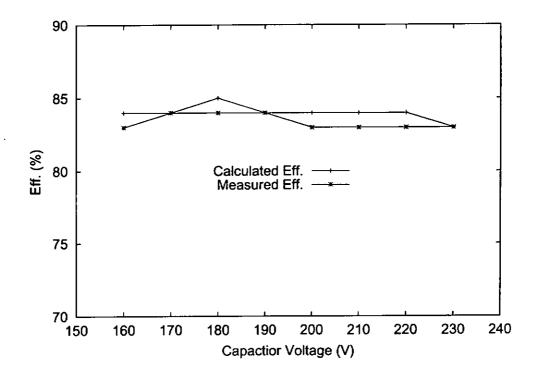

| 3.18 | Efficiency versus $V_{\rm L}$ at 100 W of ISPFC, confirming the efficiency formula; calculated curve is based on efficiency formula and measured values of $\eta_{\rm A}$ and $\eta_{\rm B}$ ; experimental curve is from direct measurement of the overall efficiency | 57 |

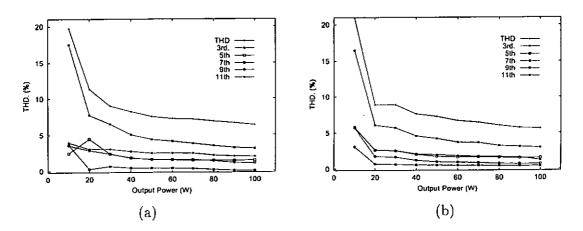

| 3.19 | Measured current harmonic distortions versus output power. (a) $V_L$ =160; (b) $V_L$ =200                                                                                                                                                                              | 57 |

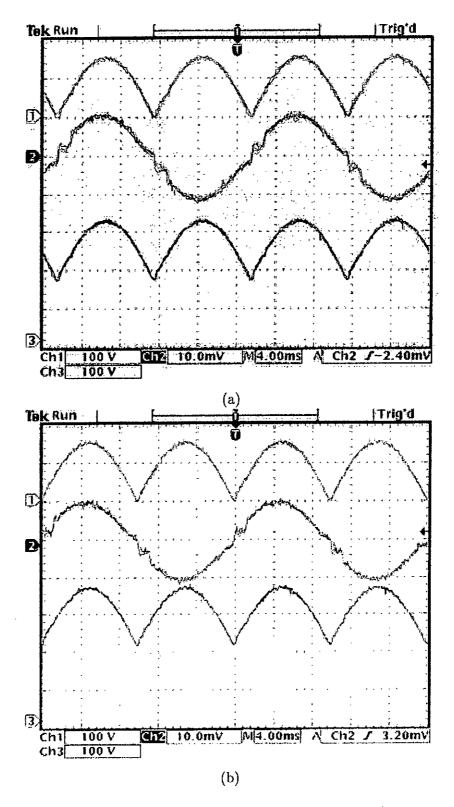

| 3.20 | Measured waveforms of input voltage (upper trace), input current (middle trace), input voltage of the two-switch forward converter (lower trace). (a) $V_L$ =160 V; (b) $V_L$ =200 V. Scale: 100 V/div, 1 A/div and 4 ms/div                                           | 58 |

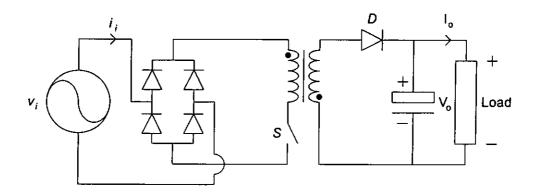

| 4.1  | Boost converter integrated with flyback converter/Energy storage for PEC and voltage regulation                                                                                                                                                                        | 61 |

| 4.2  | cascaded configuration to make an OSPFC                                                                                                                                                                                                                                               | 62 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | Equivalent circuit of the proposed OSPFC. Rectangular blocks denote converters.                                                                                                                                                                                                       | 65 |

| 4.4  | Proposed OSPFC with storage element connection block diagram                                                                                                                                                                                                                          | 65 |

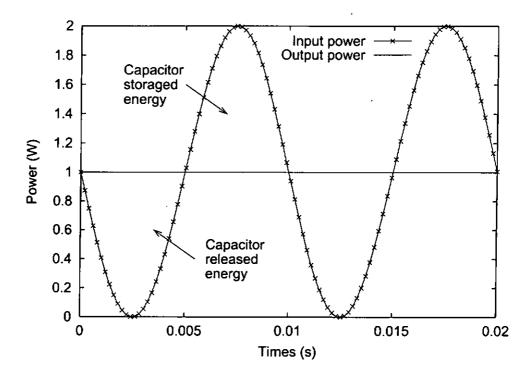

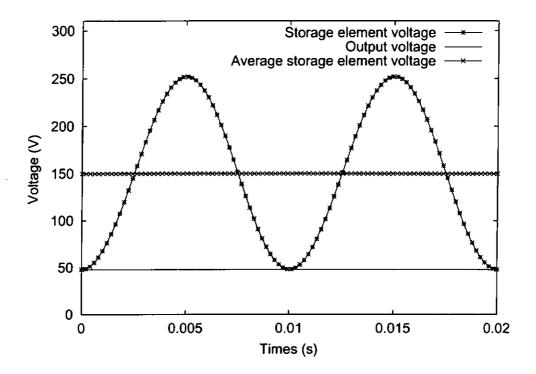

| 4.5  | Ideal power waveforms of the proposed OSPFC                                                                                                                                                                                                                                           | 67 |

| 4.6  | The proposed OSPFC of maximum voltage variation of the capacitor storage element waveforms                                                                                                                                                                                            | 69 |

| 4.7  | A typical isolated-boost half-bridge converter                                                                                                                                                                                                                                        | 70 |

| 4.8  | The isolated-boost full-bridge converter for the proposed OSPFC pre-regulator                                                                                                                                                                                                         | 70 |

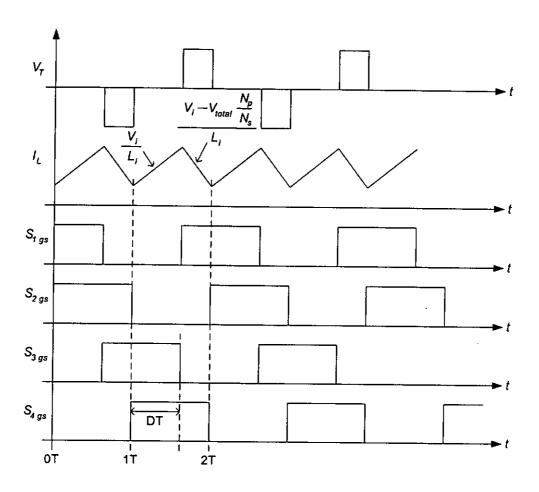

| 4.9  | The ideal gate timing diagrams for the IBFB converter with the corresponding waveforms of the input inductor current and transformer voltage                                                                                                                                          | 71 |

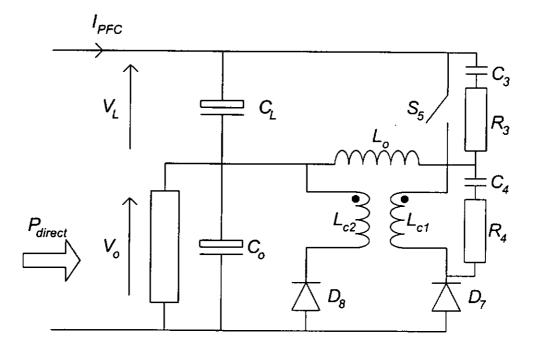

| 4.10 | The buck-boost converter with low-loss turn-on snubber                                                                                                                                                                                                                                | 72 |

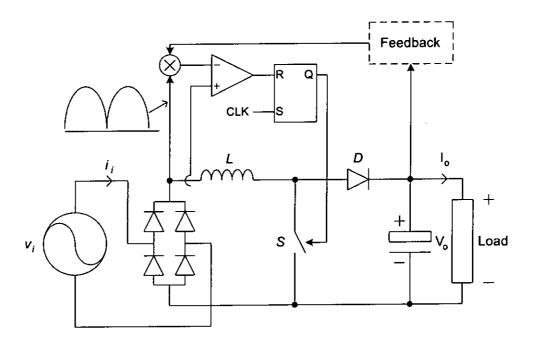

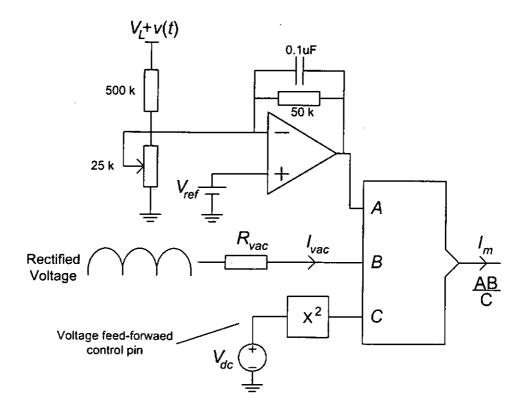

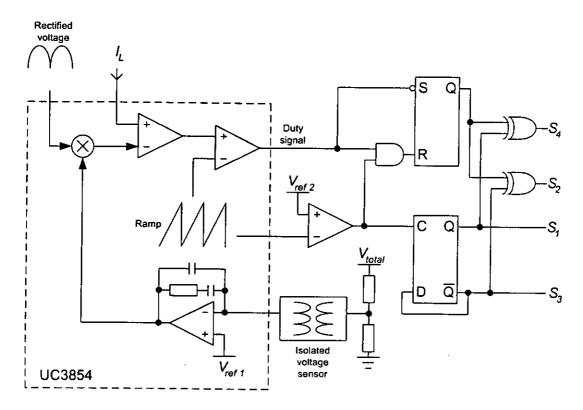

| 4.11 | The simplified schematic circuit of the PFC controller                                                                                                                                                                                                                                | 74 |

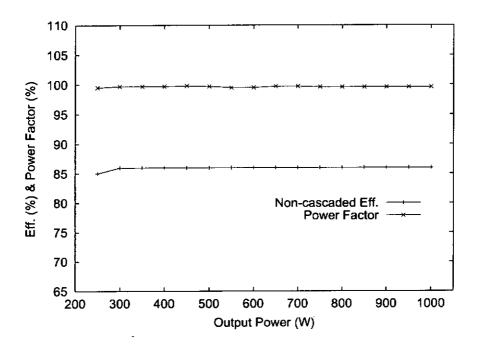

| 4.12 | The measured overall efficiency and power factor for output power level from 250 W to 1 kW                                                                                                                                                                                            | 77 |

| 4.13 | Efficiency comparison of the proposed OSPFC showing improved overall efficiency over a cascaded structure for $k=0.32$                                                                                                                                                                | 77 |

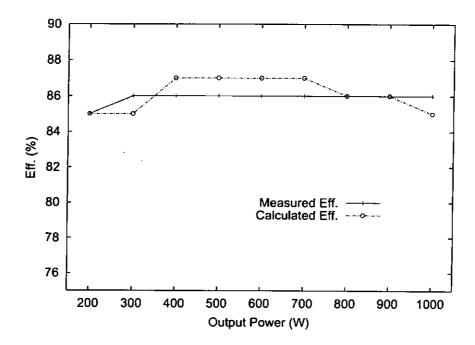

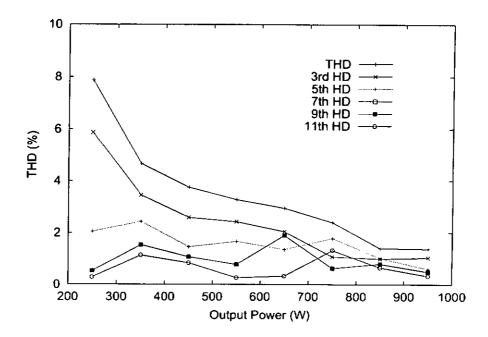

| 4.14 | Confirming the efficiency formulae; calculated curve is based on the efficiency formula and measured efficiencies of the IBFB converter and buck-boost converter at $k=0.32$ ; experimental curve is from direct measurement of the overall efficiency                                | 78 |

| 4.15 | Measured harmonic distortions versus output power at $k=0.32$                                                                                                                                                                                                                         | 78 |

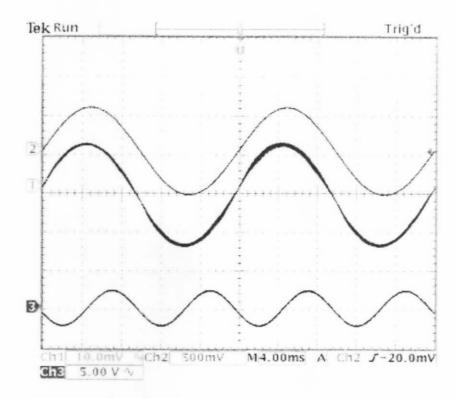

| 4.16 | Measured waveforms of input current (Channel 1), input voltage (Channel 2), output ripple voltage (Channel 3) of the IBFB converter. Input voltage is 200 V RMS with an output power of 1 kW. Scale: Channel 1 5 A/div, Channel 2 250 V/div, Channel 2.5 V/div and time have 4 mg/div | 70 |

|      | 3 5 V/div and time base 4 ms/div                                                                                                                                                                                                                                                      | 79 |

| 4.17 | Photograph of 1 kW isolated-boost full-bridge converter                                                                                                | 79 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.18 | Photograph of 600 W buck-boost converter                                                                                                               | 80 |

| 4.19 | Photograph of the PFC controller                                                                                                                       | 80 |

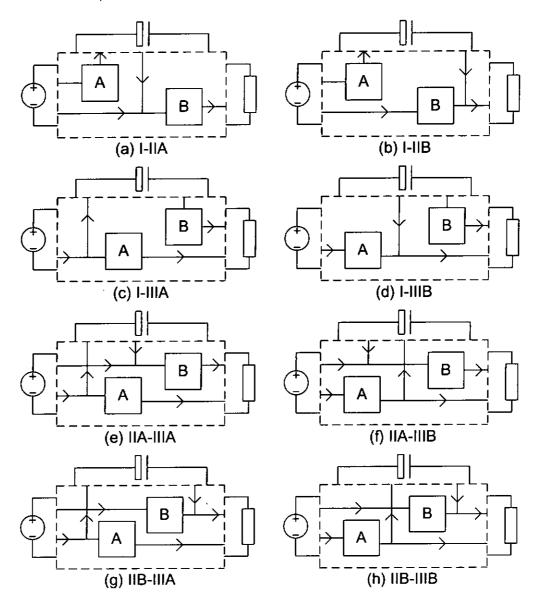

| 5.1  | Configuration block diagrams of the non-cascaded power-factor-corrected switching regulators in terms of power flow paths                              | 83 |

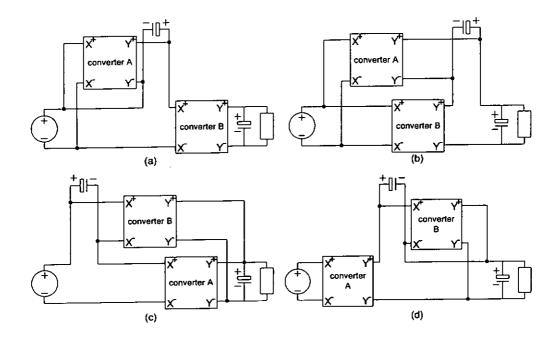

| 5.2  | Equivalent circuits of the simplest reduced redundant power processing (R <sup>2</sup> P <sup>2</sup> ) configurations: (a)I-IIA; (b)I-IIB; (c)I-IIIA; |    |

|      | and (d)I-IIIB                                                                                                                                          | 85 |

## List of Tables

| 3.1 | Specifications of the ISPFC                                                               | 40 |

|-----|-------------------------------------------------------------------------------------------|----|

| 3.2 | Summary for defining component values of ISPFC                                            | 42 |

| 3.3 | Component list and their specifications                                                   | 49 |

| 3.4 | Comparison of semiconductor devices                                                       | 50 |

| 4.1 | Specifications of the proposed OSPFC                                                      | 64 |

| 4.2 | Components and their value/types for the proposed OSPFC pre-                              |    |

|     | regulator                                                                                 | 73 |

| 4.3 | Components and their value/types for the proposed OSPFC                                   |    |

|     | voltage regulator                                                                         | 76 |

| 5.1 | Possible choice of converter for non-isolated R <sup>2</sup> P <sup>2</sup> power-factor- |    |

|     | corrected switching regulator                                                             | 86 |

| 5.2 | Comparisons among conventional boost converter, buck-boost                                |    |

|     | converter (ISPFC), and IBFB converter (OSPFC) for PFC $$ . $$ .                           | 87 |

| 5.3 | Comparisons among conventional forward converter, forward                                 |    |

|     | converter (ISPFC), and buck-boost converter (OSPFC) for volt-                             |    |

|     | age regulation                                                                            | 88 |

| 5.4 | Comments of ISPFC and OSPFC, and compared with the con-                                   |    |

|     | ventional cascaded configuration.                                                         | 90 |

## Chapter 1

### Introduction

#### 1.1 Motivation and Objectives

Huge non-linear loads generate an excessive distortion on the current of the power supplied to consumers through the power distribution system. Due to the rapid proliferation of electric machinery and electronic systems [1], the resulting distortion causes a drastic degradation in power quality of the power distribution system. Reported by Clemmensen [2], poor power quality leads to about \$13.3 billion in damage per year in the United States. Improving the power distribution system power quality and current distortion becomes paramount issue of the switching regulator design engineers.

One of the most common switching regulators is the AC-DC regulator, which supplies a DC load with power drawn from the AC mains. Virtually all electronic systems, including equipment for instrumentation, communication, computer, and household electric appliances, require a DC voltage. In low-power applications, a simple rectifier bridge is usually followed by a DC-DC regulator to smooth and regulate the output voltage. At high-power applications, the phase controlled rectification provides a regulated DC output voltage using rugged semiconductor devices.

All of these methods for generating a DC voltage from the AC mains are simple and cost-effective solutions, however they also have the drawback resulting a poor input-current waveform, which imposes problems as follows:

- 1. Distortion of the line voltage affecting both the offending equipment and other equipment connected to the same power line.

- Conducted and radiated electromagnetic interference resulting from harmonics currents drawn from the power source causing impaired performance of nearby electronic systems.

- 3. Poor utilization of the capacity of power source.

- 4. Higher losses and reactive voltage drops in the power distribution network.

Now several international standards, [3] and [4], require that the harmonics of the line-current of an electronic equipment stay below certain specified levels. The design engineers of a utility fed AC-DC switching regulator must now consider the effects of the regulator not only on the DC load, but also focus on the AC mains. In essence, the design has to consider the quality of the input current as well as the output voltage.

Cascaded power-factor-corrected switching regulators provide the low current harmonics distortion and fast voltage regulation. Inefficient operation is the major drawback in typical cascaded power-factor-corrected switching regulators. In this study, focus is put on the efficient and non-cascaded power-factor-corrected switching regulators, the idea of that regulators have been proposed recently [5]-[8]. However, a rigorous comparison of practical regulators and their design aspects are not yet available in the literature.

#### 1.2 Literature Review

In the last decade, power factor correction have been seriously considered by the industrial and academic communities [9]-[14]. Figure 1.1 summarizes the power factor correction methods, that can be broadly classified as passive methods and active methods. An overview of both passive and active power factor correction circuitries are described by J. Sebastian et al. [15], W. G. Hurley [16], R. Redl [17], P. Jain et al. [18], and O. Garcia et al. [19].

Passive methods, input-inductor filters and tuned filters, give reliable solutions for reducing of harmonic currents. In 1981, Dewan [20] presented a

Figure 1.1: Classification of power factor correction methods.

paper mentioning optimum input-inductor filters design for single-phase rectifier power supplies. In 1989, Kelley and Yadusky [21] reported a quantitative computer-simulation-based analysis of single-phase and three-phase rectifier line-current harmonics and power factor as a function of the output filter inductor. But the bulky and heavy input-inductor filter is an unacceptable solution in modern electronic products. Merit of the tuned input filter compare with the input-inductor filter is that the size of the filter becomes smaller. In 1990 and 1992, Vorperian and Ridley [22], and Ignazio [23] proposed their series resonant filters respectively to achieve a high power factor with a sinusoidal input current. A novel passive method was proposed by Wolfle et al. [24] in 2000, there reported a new swinging inductor to implement adapted harmonic filtering over a wide power change range to overcome limited operating power range of the input-inductor filters and the tuned filters.

Active PFC methods can be classified as automatic PFC and non-automatic PFC. The output power level is a main consideration for using the automatic PFC and the non-automatic PFC [25]. It can be well understood [26]-[29] the basic converters operating in discontinuous conduction mode (DCM) offer automatic PFC due to their inherent resistive input impedance. In 1998, Chow et al. [30] proposed their boost DCM power factor correctors using both pulse

width modulation and frequency modulation for achieving high power factor, low bulk capacitor voltage, and fast voltage regulation. The DCM Cuk converters for power factor correctors was reported by Brkovic et al. [31], and Simonetti et al. [32] in 1992, and 1997 respectively. In 1994, Peres et al. [33] reported a Zeta converter can also be used as an automatic PFC. Discontinuous capacitor voltage mode (DCVM) is that the voltage across a certain capacitor becomes zero for a portion of a switching period. DVCM can also provide automatic PFC that was reported by Tse and Chow [34], and Lin and Lee [35].

Non-automatic power factor correctors are based on the control of the input inductor current of converters for achieving high power factor. In 1987, Schlecht and Miwa [36] proposed their active power correction for switching power supplies applying boost converter with clamping circuit. An interesting comparison was reported by Drobnik [37] that a push-pull converter cascaded-connected with front-end boost converter for PFC is more efficient than that push-pull converter without PFC. A new PFC circuit using a buck converter and a boost converter characteristics is proposed by Jiang and Lee [38]. A low output power PFC circuit applying flyback converter is introduced by Tang et al. [39]. A 1-kW battery charger with front-end hard-switched boost converter for PFC is given by Canales et al. [40]. Resonant converters are also proposed as non-automatic PFC [41]-[44], however, the design and the circuits operation are more complicated when compared to any non-resonant PFC converters.

The above-mentioned literature of the non-automatic power factor correctors presented unregulated or cascaded power-factor-corrected switching regulators. Non-cascaded or parallel power-factor-corrected switching regulators, provide PFC and fast voltage regulation, concept was proposed at 1993 by Jiang et al. [45]. In 1994, Jiang and Lee [46] presented a practical parallel power factor corrected switching regulator. Simulation results for the two-transformer PFC switching regulator with parallel power processing were discussed by Srinivasan and Oruganti [47]. A systematical method for generating non-cascaded power factor switching regulators is discussed by [6]-[8].

#### 1.3 Objectives of the Thesis

The primary objective of this thesis is, based on the reduced-redundant-power-processing (R<sup>2</sup>P<sup>2</sup>) principle, to design and implementation non-cascaded power-factor-corrected switching regulators that can achieve in high power factor, fast output voltage regulation, and their high efficiency are compared in terms of their features and specifications. The designed and implemented regulators can be used for providing a systematical record for switching regulator design engineers.

#### 1.4 Outline of the Thesis

Chapter 2 briefly reviews the definition of power factor. Basic PFC principles and some techniques used for power-factor-corrected switching regulator are described. Then an introduction for cascaded power-factor-corrected switching regulators are provided. Finally, it discusses the benefits of the non-cascaded switching regulators and outlines two particular non-cascaded switching regulators.

Chapter 3 discusses an Input-Side Non-Cascaded Power-Factor-Corrected Switching-Regulator for low power applications. Design aspects of this switching regulator such as power transformer, voltage stress and current rating of switches and diodes, and controllers are given. Experimental results and waveforms are reported. Comparison with the theoretical results are made to verify the R<sup>2</sup>P<sup>2</sup> function of this switching regulator.

Chapter 4 describes an Output-Side Non-Cascaded Power-Factor-Corrected Switching-Regulator for high power applications. Analysis of this particular switching regulator is given. Experimental results and waveforms are reported that are compared with the theoretical results to verify the principle of R<sup>2</sup>P<sup>2</sup>.

Chapter 5 gives a detailed comparison of these two particular switching regulators. Features and specification of the switching regulators are discussed. Issue related to output power levels, circuit complexity, components stress, and ease of control are elaborated.

Conclusions and further improvements are given in Chapter 6.

## Chapter 2

## Review of Power Factor and PFC Circuits and Techniques

This chapter reviews the definition of power factor and the existing control methods in terms of the non-automatic power-factor-corrected switching regulators. The basic requirements of the power-factor-corrected switching regulators with PFC and fast voltage regulation are discussed in detail. The outline of two non-cascaded power-factor-corrected switching regulators will be shown.

#### 2.1 Power Factor

The term power factor is borrowed from elementary AC circuit theory. Power factor is one of the common measures of the line current quality. It is connecting both voltage and current components. In this section, power factor is analyzed from different avenues and important observation are made.

#### 2.1.1 Time-Domain Interpretation

Consider a load drawing a current  $i_l$  from the AC mains with voltage  $v_l$ . Both  $i_l$  and  $v_l$  are sinusoidal waveforms with period  $T_l$ . The load draws the average power that is given by:

$$P_{\text{ave}} = \frac{1}{T_l} \int_0^{T_l} v_l i_l dt \tag{2.1}$$

Figure 2.1: (a) The phasor diagram of the AC mains connecting with an capacitive load; (b) Power triangle.

where  $\int_0^{T_l}$  represents the integral over any continuous interval of time length  $T_l$ . The power factor is defined by:

Power Factor =

$$\frac{P_{ave}}{V_{lrms} \times I_{lrms}}$$

(2.2)

where  $V_{lrms}$  and  $I_{lrms}$  are presented by the R.M.S. line-voltage and line-current, are given by:

$$V_{\rm lrms} = \sqrt{\frac{1}{T_l} \int_0^{T_l} v_l^2 dt}$$

(2.3)

$$I_{lrms} = \sqrt{\frac{1}{T_l} \int_0^{T_l} i_l^2 dt}$$

(2.4)

A set of afore-described equations is based on time-domain to represent power factor.

#### 2.1.2 Vector-Algebra Interpretation

Figure 2.1 (a) and (b) show a phasor diagram and a power triangle of the AC mains. The phasor diagram shows that the AC mains connected to a capacitive load, because the current vector,  $i_l$ , is leading the voltage vector,  $v_l$ . From Figure 2.1(a),  $||v_l||$  and  $||i_l||$  are represented the fundamental components of the voltage and current. Also  $||v_l||$  and  $||i_l||$  denote respectively the length of the vector  $v_l$  and  $i_l$ . For example,  $||v_l||$  is the hypotenuse of the triangle of

$v_l$ OQ.  $\theta$  indicates the phase difference between  $v_l$  and  $i_l$ . Figure 2.1 (a) shows that:

$$\cos\theta = \cos(\theta_{\rm i} - \theta_{\rm v}) \tag{2.5}$$

$$= \cos \theta_{\rm i} \cos \theta_{\rm v} + \sin \theta_{\rm i} \sin \theta_{\rm v} \tag{2.6}$$

$$= \cos \theta_{i} \cos \theta_{v} + \sin \theta_{i} \sin \theta_{v}$$

$$= \frac{v_{l_{1}} i_{l_{1}} + v_{l_{2}} i_{l_{2}}}{\|v_{l}\| \|i_{l}\|}$$

(2.6)

The power triangle shown in Figure 2.1 (b) indicates an information of the phasor diagram. The OA of Figure 2.1 (b), which is projection OP of  $i_l$  onto vector  $v_1$  in Figure 2.1 (a), is used to denote a real power of that capacitive load. A product of  $||v_1||$  and  $||i_1||$  is apparent power, OB, of the capacitive load.  $\theta$  can be expressed by the power triangle as shown below:

$$\cos \theta = \frac{OA}{OB}$$

(2.8)

=  $\frac{\text{Real Power}}{\text{Apparent Power}}$

$$= \frac{\text{Real Power}}{\text{Apparent Power}} \tag{2.9}$$

From the mathematic point of view, the phasor diagram and power triangle also provide important information, that: the length of OA will be zero when  $||i_1||$  is orthogonal with  $||v_1||$ , the maximum length of OA must be small or equal the length of the power triangle hypotenuse, OB. Furthermore, from the linear circuit theory, these observations give power factor  $=\cos\theta \leq 1$ , its means power factor can never be greater than unity. Power factor is the ratio of the real power to the apparent power ( $||v_l|| ||i_l|| = V_{lrms} I_{lrms} VA$ ). The apparent power will be equal to the real power, if power factor is unity.

#### Power Factor for Sinusoidal Voltage 2.1.3

Power factor for sinusoidal voltage contains two parameters and they are called the displacement factor and the distortion factor. The displacement factor can be interpreted by vector-algebra easily, however, the distortion factor relates to the frequency-domain problem. A periodic distorted current signal,  $i_l$ , is represented by Fourier series with a fundamental angular frequency of  $\omega$ as shown below:

$$i_l = I_l + \sum_{n=1}^{\infty} a_n \cos \omega nt + b_n \sin \omega nt$$

(2.10)

where  $a_n$ ,  $b_n$ , and  $I_l$  are expressed below:

$$a_n = \frac{1}{\pi} \int_0^{2\pi} i_l \cos \omega n t dt \tag{2.11}$$

$$b_n = \frac{1}{\pi} \int_0^{2\pi} i_l \sin \omega n t dt \qquad (2.12)$$

$$I_{l} = \frac{1}{2\pi} \int_{0}^{2\pi} i_{l} dt \tag{2.13}$$

When the current signal only contains the even function or the odd function,  $a_n$  is zero, the series becomes,

$$i_l = I_l + I_1 \sin \omega t + I_2 \sin 2\omega t + \dots$$

(2.14)

where  $I_l$  is the DC component of the series and  $I_1$  is the fundamental component of  $i_l$ . Because only the fundamental current can contribute to average power, according the definition of power factor from 2.2 and 2.9, an equation of power factor for sinusoidal voltage will be reconstructed to follow

Power Factor =

$$\cos \theta \frac{I_1}{i_l}$$

(2.15)

where the  $\frac{I_1}{i_l}$  is called the distortion factor. If  $i_l$  contains no a DC component, then the distortion factor can be written by

$$\frac{I_1}{i_l} = \frac{1}{\sqrt{1 + (\text{THD})^2}} \tag{2.16}$$

where THD denotes Total Harmonic Distortion, is defined by

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_n^2}}{I_1}$$

(2.17)

THD provides only the harmonic content but without provides the phase information. The displacement factor only contains the phase information of the fundamental components of the current and voltage.

In the case of the pure linear load, the line current contains only a fundamental component and power factor is solely determined by the displacement factor. On the other hand, the load is reactive, and nonlinear the input current can be both displaced, phase shift, and distorted. Fragmenting the power factor into two different factors is useful because these two problems require entirely different solutions. For example, if a power system is heavily loaded

Figure 2.2: A simple input capacitor filter circuit for AC-DC power supply.

with an inductive load, it will be compensated by installing suitable parallel a capacitor to reduce the phase angle between the line voltage and the line current. However, a non-linear load requires a different solution as this becomes clear in Section 2.3.

#### 2.2 Input Capacitor Filter

For low to medium power applications, the most common method to generating DC power from the AC mains uses an input capacitor filter circuit as shown in Figure 2.2. The circuit is a bridge rectifier followed by a filter capacitor for smoothing the rectified voltage. The filter capacitor voltage of the circuit should have a small ripple, which depends on the capacitor capacitance. The input capacitor filter is a cost-effective, simple, and rugged system which is often used with a post-regulator. The voltage regulation is provided by DC-DC converter for the well-regulated output voltage.

Unfortunately, the input capacitor filter suffers from a poor line current waveform. Since the output capacitor has large capacitance for maintaining a nearly constant voltage, the diode bridge turns on only for a narrow duration when the input voltage is close to its peak resulting in peaky input current pulses of the narrow duration as shown in Figure 2.3 (a). Although both Figures 2.3 (a) and (b) represent the same consumption of average power for any given resistance, the line current shown in Figure 2.3 (b) is smaller than that shown in Figure 2.3 (a). Compared to the pure resistive case, the input

Figure 2.3: (a) A simple input capacitor filter circuit line voltage and line current waveforms; (b) The voltage and the current waveforms of the AC mains directly connect to a resistor.

capacitor filter circuit case shown in Figure 2.3 (a) demands a higher peak current and severe current harmonic distortion that impose a higher demand on the power generators, transformers, circuit breakers, and power transmission lines in order to supply the same amount of average power for the same loading. Hence, all the elements of a power distribution system should be designed for a higher rating, resulting in greater size, weight, and cost.

#### 2.3 Active Power Factor Corrector

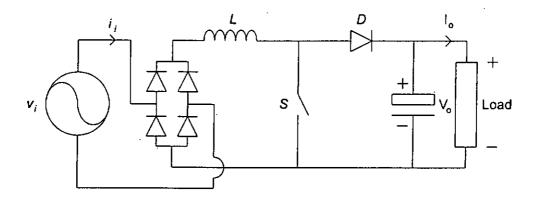

A typical active power factor corrector with an energy storage element is shown in Figure 2.4. This is a method for generating DC voltage from the AC mains. The corrector is constructed by a diode, a switch, and an inductor. The diode, D, is an ultra-fast diode, that is called a passive switch because the turn-on and turn-off time of that switch depends on the corrector switch. The switch, S, is an active switch, that should be operated at a high frequency, switching frequency, higher than the line frequency. In this particular power factor corrector, the input current is equal the inductor current, which is controlled by the active switch. A capacitor, C, is the energy storage element of the power factor corrector, its function will be discussed in next Section. The

Figure 2.4: A typical active power factor corrector with an energy storage element.

output voltage of the power factor corrector should contain a ripple voltage and the ripple voltage frequency is twice of the line frequency, so the output terminal of power factor corrector always connects a DC-DC converter for providing the tightly regulated output voltage and the fast load transient response. Therefore all power factor correctors regardless of their employed circuit topology are also known as PFC pre-regulators.

Figure 2.5: A block diagram of the common active power-factor-corrected switching regulator connection.

# 2.4 Basic Requirements of Active PFC Switching Regulators

Three basic stages, pre-regulator, voltage regulator, and energy storage element are essential components of the active power-factor-corrected switching regulators. A block diagram of the most of common active power-factor-corrected switching regulator is shown in Figure 2.5. A bridge rectifier is followed by a pre-regulator, then the pre-regulator output is connected to a capacitor which acts an energy storage element. The final stage of the switching regulator is voltage regulator.

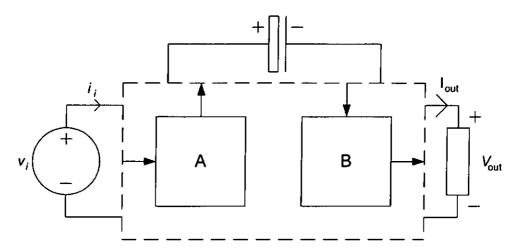

Figure 2.6: Three-port diagram for active power-factor-corrected switching regulator.

A three-port diagram is reported by [6], [7], and [48] as shown in Figure 2.6. The diagram presents the basic requirement of the active power-factor-corrected switching regulators. The input of the three-port diagram is a resistive load simulator. The simulator makes that the line current waveform is proportional to the line voltage. In the switching regulator, this property should be obtained by active control. An internal energy storage element is necessary to absorb and supply the difference between the instantaneous input

power and the constant output power. The internal energy storage element is also necessary to hold-up power for providing the output load during short-duration. For those reasons the internal energy storage element should have capability for storing the low frequency energy, therefore, a single electrolytic capacitor is invariably used to meet the requirements. A wide bandwidth regulated voltage source is provided by a switching converter for servicing the output load, because the simulator can be only provide unregulated voltage, which contain second harmonic ripple voltage. The regulated output voltage must not contain the second harmonic ripple voltage. Hence the voltage regulator is required and controlled by a feedback loop with wide bandwidth much greater than the second harmonic frequency.

#### 2.4.1 Pre-Regulator

#### 2.4.1.1 Buck Pre-Regulator

Figure 2.7: Buck pre-regulator.

Figure 2.7 and Figure 2.8 show a buck pre-regulator circuit and the typical line current waveform of the buck pre-regulator together with the AC mains voltage. A forward converter, an isolated buck converter, is discussed by Pereira et al. [49] and Nagao [50] for providing PFC. The line current becomes zero when the instantaneous line voltage is below than the output voltage. That leads a significant distortion of the line current. Furthermore, the buck pre-regulator input current is pulsating, an additional L-C filter is needed for smoothing the pulsating input current. The active switch driver is

an isolated gate drive circuit. Because the buck pre-regulator has about draw-backs, the buck converter are seldomly used for acting to PFC pre-regulator.

Figure 2.8: Switch current in buck pre-regulator.

#### 2.4.1.2 Boost Pre-Regulator

The continuous conduction mode (CCM) boost converter is the most common topology for PFC pre-regulator applications [51]–[53]. The boost pre-regulator offers the best utilization of the active switch [54] such as lower average and peak current rating, and can be applied a non-isolated gate drive circuit for the active switch. However, the output voltage of the boost pre-regulator is always higher than the AC mains peak voltage, that is an inevitable drawback of the boost pre-regulator.

There are many boost variations pre-regulator [55, 56], depending on the number of the switches and the location of the inductor. However the most significant classification is based on the operating mode of the inductor current, because the operation mode dictates the method of control and their PFC performance.

For high power applications, boost pre-regulators always operate in CCM. That makes a reasonable current rating of that pre-regulators semiconductor

devices. However, the problem of the CCM boost pre-regulators is slow reverse recovery time of the power diode. This effect leads the serious power loss of the CCM boost pre-regulator and reduces reliability of that pre-regulator. Apart from employing the ultra-fast diode [57], the passive snubber circuit [58, 59], and the active clamping and soft switching [60]–[64] techniques can also be applied to reduce the associated power losses.

The discontinuous conduction mode (DCM) boost converter is popular topology for PFC pre-regulators producing a high power factor but with a substantial amount of harmonic distortion on the line current. Under constant-duty-cycle operation, the amount of line-current harmonics can be reduced at the expense of high conversion ratio [26]. The DCM boost pre-regulators are free from the problem of slow reverse recovery time at the power diode, but the DCM boost pre-regulator active switch suffers the high peak and R.M.S. current rating for a given output power level compared with CCM boost pre-regulator.

#### 2.4.1.3 Buck-Boost Pre-regulator

Figure 2.9: Flyback pre-regulator.

Figure 2.9 shows an isolated version buck-boost converter, flyback converter. The buck-boost pre-regulator has an output voltage step down and up capability, it can provide a wide input line voltage range for maintaining a low line-current distortion. This feature overcomes the buck and the boost pre-regulators drawbacks. Figure 2.10 shows the line current waveform together with the line voltage for the flyback PFC pre-regulator operated at CCM.

Figure 2.10: Switch current in flyback pre-regulator.

Figure 2.11: Switch current in flyback operated in DCM pre-regulator.

The flyback topology is usually furnishes for low power PFC pre-regulator applications, because it suffers serious voltage overshoot occurred at the active switch due to the energy stored in the leakage inductance of the isolating transformer. The voltage overshoot problem is solved by an effective clamping, which discusses in [65, 66].

The flyback converter can automatically simulates a resistor to get unity power factor without the harmonic current, when the converter is operated in DCM under constant duty-cycle and switching frequency operation [28]. This property can be easily understand because the averaged input line current is proportional to the line voltage along with the line period as shown in Figure

2.11. This feature leads that the DCM flyback converter provides a good solution for PFC at low power and cost applications.

#### 2.4.2 Voltage Regulator

Voltage regulators provide fast voltage regulation to an output load. In a front-end boost power-factor-corrected switching regulator, the voltage regulator is providing the stepped-down voltage function and galvanic isolation. However, in the front-end flyback power-factor-corrected switching regulator, the voltage regulator is only providing voltage regulation. In essence any DC-DC converters can be voltage regulators.

#### 2.4.3 Energy Storage Element

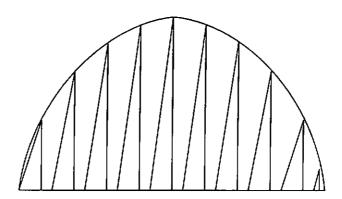

An energy storage element plays an important role in active power-factor-corrected switching regulators. Figure 2.12 shows power waveforms of the active power-factor-corrected switching regulator with unity power factor and perfect voltage regulation. For a constant load with the output power of  $P_{\text{out}}$ , the power drawn from the AC mains has a value of  $P_{\text{out}}(1-\sin 2\omega t)$  for an ideal active power factor corrector. The minimum stored energy necessary for unity-power-factor operation is the difference between the energy consumed by the constant-power load and the energy delivered by the AC mains during one-quarter of its period  $\frac{\pi}{2\omega}$  starting with zero energy.

The energy consumed by the load,  $E_{\rm dc}$ , during  $0 < t < \frac{\pi}{2\omega}$  is

$$E_{\rm dc} = P_{\rm out} \frac{\pi}{2\omega} \tag{2.18}$$

The energy delivered by the line,  $E_{\rm dc}$ , during  $0 < t < \frac{\pi}{2\omega}$  is

$$E_{\rm ac} = \int_0^{\frac{\pi}{2\omega}} P_{\rm out} (1 - \sin 2\omega t) dt$$

$$= P_{\rm out} (\frac{\pi}{2\omega} - \frac{1}{\omega}) \tag{2.19}$$

The minimum stored energy is the difference between the two energies as given

$$E_{\min} = E_{dc} - E_{ac}$$

$$= \frac{P_{out}}{\omega}$$

(2.20)

Figure 2.12: Power waveforms for ideal active power-factor-corrected switching regulator at line frequency equal 50 Hz.

If the storage elements is a capacitor  $C_s$ , the energy stored in the capacitor is

$$E_{C_s} = \frac{1}{2} C_s (v_{C_{s_{max}}}^2 - v_{C_{s_{min}}}^2)$$

or =  $C_s V_{C_s} |\Delta v_{C_s}|$  (2.21)

$$or = C_s V_{C_s} |\Delta v_{C_s}| \qquad (2.22)$$

where  $E_{\mathrm{C_s}}$  is the static value of  $v_{\mathrm{C_s}}$ , and  $|\Delta v_{\mathrm{C_s}}|$  is the peak-to-peak variation of the  $v_{C_n}$ . Using equations (2.20) and (2.22)

$$|\Delta v_{\rm C_s}| = \frac{P_{\rm out}}{\omega C_{\rm s} V_{\rm C_s}} \tag{2.23}$$

Therefore, the amount of ripple voltage can be increased by adding an output load and can be reduced by a large capacitor under a high static stress.

In the case of a typical power-factor-corrected switching regulators, for maintaining the unity-power factor operation, the minimum capacitance can be obtained if the capacitor voltage is allowed to vary from zero to its peak value during each half of the AC mains period, such that  $|\Delta v_{C_s}| = 2V_{C_s}$ . The calculating minimum capacitance is

$$C_{\rm S_{min}} = \frac{2P_{\rm out}}{\omega |\Delta v_{C_{\rm s}}|^2} \tag{2.24}$$

#### 2.5 Control Methods for Pre-Regulator

Figure 2.13 shows the simplify circuit diagram of a boost pre-regulator with active control of the line current and output voltage. Virtually the control circuit takes a rectified sinewave reference, synchronized to the line voltage, which provides a template for the line current controlling loop. The template level is multiplied by output feedback signal, the level of the output feedback signal depends on output voltage of the boost pre-regulator, via the electronic multiplier. Therefore the output voltage of the boost pre-regulator stays constant when the line voltage or load current varies.

Figure 2.13: CCM boost pre-regulator under current-mode control simplify circuit.

The slow response time to a load change is major problem of the PFC pre-regulator. As mentioned in Section 2.4.3 due to the large line frequency ripple in output voltage, the crossover frequency of the voltage control loop of the pre-regulator must be kept below about half of the AC mains frequency. Excessive third-harmonic distortion is occurred by higher crossover frequency of the voltage control loop [67].

Feedforward of the line voltage can be used for reducing the response

times in the PFC pre-regulator without increasing the bandwidth of the loop gain. An example applies line voltage feedforward control for pre-regulator is shown in [68]. The result is that the output voltage is kept narrow variation based on the concept of the constant output power.

Several current-control methods are available for active control of the line current. Mahdavi et al. [69], gives consideration of their performances in terms of electromagnetic interference (EMI).

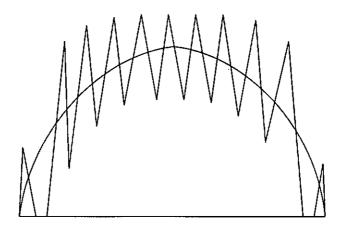

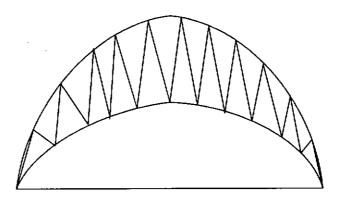

Average Current mode Control—The small line current distortion can achieved by an average current mode control. It is the most common method of the pre-regulators control. In essence, the average current mode control can be applied in any pre-regulator with different topological arrangement [70]. In a few switching cycle, inductor current of the pre-regulator is averaged for controlling the line current, so the average current tracks the line voltage with a high degree of accuracy. The additional advantage of this method is that the switching noise sensed by current sampling circuit can be effectively reduced by the effect of averaging. Figure 2.14 shows the boost pre-regulator line current waveform using average current mode control.

Figure 2.14: Boost pre-regulator line current waveform under average current mode control.

Peak Current mode Control-The simplest implementation is peak current

mode control [71] which has a cost-effective circuit. For the peak current mode control, the reference template plays an important role, that determines the line current shape and value. The active switch is turned off when the inductor current reaches the value governed by the controlled reference template, it is turned on again with constant frequency clock pulses. Figure 2.15 shows the line current waveform using peak current mode control applied at the boost pre-regulator. In the boost pre-regulator, the peak current mode control provides a very nice and low distortion input line current, because the peak inductor current value is as close as the averaged inductor current. However, in the buck-boost converter, the inductor current is not the input current, therefore the wrong current is controlled and leads distortion of the line current. Poor noise immunity is a disadvantage compared with average current mode control.

Figure 2.15: Boost pre-regulator line current waveform applies peak current mode control.

Hysteretic current mode control—Two reference templates, an upper reference and a lower reference, are determined the line current of the boost pre-regulator [72] as shown in Figure 2.16. The switch of the boost pre-regulator is turned off when the peak inductor current reaches the upper reference, on the other hand, the switch is turned on when the peak inductor current reaches the lower reference. The distortion of the boost pre-regulator line current depends on these two references. Without control loop, which reduces the control circuit

complexity, but the disadvantage of the hysteretic current mode control is that the switching frequency varies over the line period.

Figure 2.16: Boost pre-regulator line current waveform using variable hysteretic current mode control.

Borderline current mode control-Lower reference becomes the ground level, that is major difference between the borderline current mode control and the hysteretic current mode control. The boost pre-regulator operated in borderline current mode control is illustrated by Zhang et al. [73]. The boost pre-regulator enjoyably operates at borderline current mode control, because that inherent soft-switched property eliminates the losses associated with the power diode reverse recovery time and a borderline current mode control boost pre-regulator can serve for the front-end PFC pre-regulator for distributed power system. The main drawbacks of borderline current control are variable switching frequency and high differential mode EMI. However, the EMI problem can be solved by interleaving two boost pre-regulators with special switching sequence. Figure 2.17 shows line current waveform using borderline current mode control.

Figure 2.17: Boost pre-regulator line current waveform using borderline current mode control.

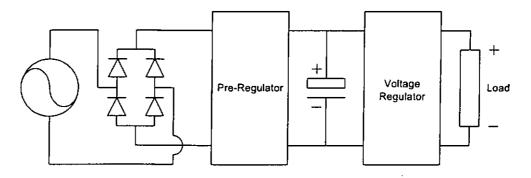

Figure 2.18: Power flow diagram for cascaded active power-factor-corrected switching regulator.

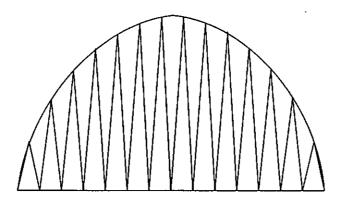

### 2.6 Non-Cascaded Active PFC Switching Regulators

Three port diagram, mentioned at Section 2.4, illustrates the switching regulators which must contain a pre-regulator, a voltage regulator, and an energy storage element for achieving the PFC and fast voltage regulation. The most straightforward way to design of an active power-factor-corrected switching regulator is to connect the regulators and the energy storage element serially. Efficiency is limited in this cascaded connection. For example, if the efficiency of pre-regulator is 80% and the voltage regulator also is 80%, the overall efficiency is 64% as shown in Figure 2.18. Non-cascaded active

power-factor-corrected switching regulators are allowed apart of input energy only processed by one power stage and this arrangement can increase overall efficiency of the PFC switching regulators.

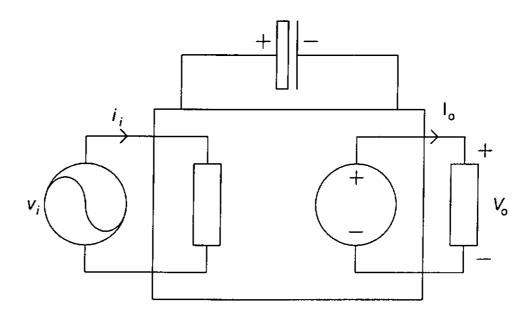

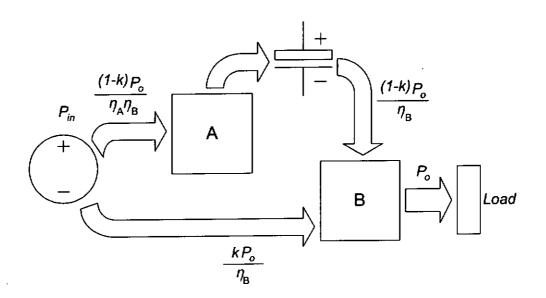

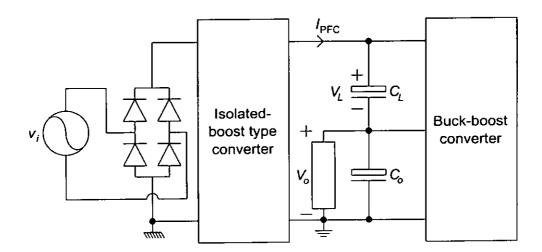

Fifteen configurations of the non-cascaded active power-factor-corrected switching regulators are developed by [6]–[8]. In this fifteen configurations, the two particular configurations' power flow diagrams are shown in Figure 2.19 and Figure 2.20. They are named by Input-Side Non-Cascaded Power-Factor-Corrected Switching Regulator (ISPFC) and Output-Side Non-Cascaded Power-Factor-Corrected Switching Regulator (OSPFC).

Figure 2.19: Power flow diagram for input-side non-cascaded power-factor-corrected switching regulator.

Theoretical efficiency of three switching regulators are shown below:

For the cascaded switching regulator shown in Figure 2.18, the efficiencies of the two converters are  $\eta_A$  and  $\eta_B$ , the overall efficiency is given by

$$\eta_{\text{cascaded}} = \eta_{\text{A}} \eta_{\text{B}}$$

(2.25)

For ISPFC shown in Figure 2.19, the efficiency equation is shown as follow

$$\eta_{\text{ISPFC}} = (1 - k)\eta_{\text{A}}\eta_{\text{B}} + k\eta_{\text{B}}$$

$$= \eta_{\text{A}}\eta_{\text{B}} + k\eta_{\text{B}}(1 - \eta_{\text{A}})$$

$$> \eta_{\text{A}}\eta_{\text{B}} \text{ for all } 0 < k < 1 \tag{2.26}$$

where k is the ratio of the input power that is split between converter A and

Figure 2.20: Power flow diagram for output-side non-cascaded power-factor-corrected switching regulator.

converter B, and  $\eta_A$  and  $\eta_B$  are the efficiency of the converter A and converter B, respectively.

For OSPFC shown in Figure 2.20, the efficiency equation is shown as follow

$$\eta_{\text{OSPFC}} = (1 - k)\eta_{\text{A}}\eta_{\text{B}} + k\eta_{\text{A}}$$

$$= \eta_{\text{A}}\eta_{\text{B}} + k\eta_{\text{A}}(1 - \eta_{\text{B}})$$

$$> \eta_{\text{A}}\eta_{\text{B}} \text{ for all } 0 < k < 1 \tag{2.27}$$

where k is the ratio at which amount of input power is split at the output converter A to the output load.

As an observation of these equations, from Equation 2.26 and Equation 2.27, it is clear that ISPFC and OSPFC can achieve higher efficiency than the cascaded one. The efficiency gain of ISPFC and OSPFC are same, if the constituted converters have same efficiency.

#### 2.7 Summary

This chapter gives detail definitions at time-domain interpretation and vector-algebra interpretation to explain power factor. A brief introduction describes the active power factor corrector. Basic requirements of active powerfactor-corrected regulators is illustrated. In general, there are three basic components, a pre-regulator, a voltage regulator, and an energy storage element. Three-port diagram is used to explain the function of each component, such as the pre-regulator is a resistive load simulator, the voltage regulator provides a wide bandwidth regulated voltage source, and the energy storage element is a buffer for absorbing the difference between the instantaneous input power and the constant output power. The advantages and drawbacks of buck pre-regulators, boost pre-regulators, and buck-boost pre-regulators are described. The reasons why these pre-regulators cannot provide tight output voltage regulation and fast load transient response are also explained based on energy balance consideration. The existing control methods, average current mode control, peak current mode control, hysteretic current mode control, and borderline current mode control, for power-factor-corrector are shown and illustrated with their merits and disadvantages. Finally, this chapter explains the benefits, efficiency gain, of the non-cascaded active power-factor-corrected switching regulators.

# Chapter 3

# Input-Side Non-Cascaded PFC Switching Regulator

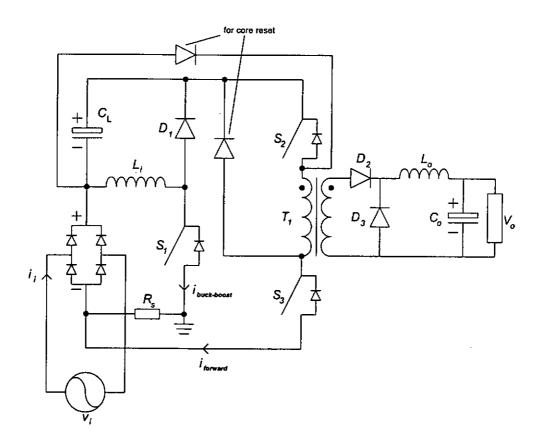

For off-line low-power applications, power-factor-corrected switching regulators are usually operated in DCM. It always uses a DCM flyback converter for automatic PFC and galvanic isolation, then the DCM flyback converter is followed by a DC-DC converter for voltage regulation. However, this approach leads that the semiconductor devices, active switch and power diode, of the DCM flyback converter suffer high voltage and current stress rating, which causes the inefficient cascaded power-factor-corrected switching regulators to become even more inefficient. While a number of non-cascaded DCM switching regulators with PFC capability are already being proposed for low power applications. Therefore, a new off-line input-side non-cascaded power-factorcorrected switching regulator for low power applications studies in this chapter. Especially the switching regulator is constructed by a CCM buck-boost and a CCM two-switch forward converter, that using non-cascaded arrangement provides more efficient operation. In essence, the switching regulator has potential to serve medium (below 500W) power applications. A completed design procedure for that particular switching regulator is discussed. An outline of this switching regulator specifications are described, and using the block diagram, as mentioned at Figure 2.19, realizes that practical non-cascaded switching regulator.

The original contribution of this chapter is to develop a completed proce-

dure and an analysis of this particular switching regulator. A discussion is included to show voltage and current rating of the active switch and power diode and practical issue such as power transformer, core reset path, and snubber circuit related the switching regulator. The measured results and experimental waveforms validate the switching regulator, which achieves PFC and fast voltage regulation, and high efficiency are also provided.

# 3.1 Reported Non-cascaded Input-Side Converter: "Zeta Converter"

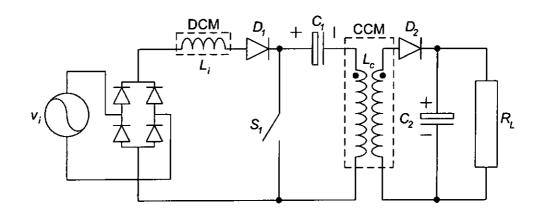

From the power flow diagram point of view, zeta converter is a non-cascaded input-side converter. Zeta converter merges a buck-boost converter and a buck converter to share same switch for operation. Zeta converter for PFC is introduced by [33, 74]. Figure 3.1 is shown a non-isolated zeta converter, which is constructed by two inductors and capacitors, a power diode and an active switch.

Figure 3.1: 'Non-isolated zeta converter'

The operation of zeta converter is split by two stages, switch turned-on and switch turned-off stages. When the active switch, S, is conducting, the input voltage source supplies energy to the input inductor,  $L_i$ . The energy available in the output inductor,  $L_o$ , comes from the line source and the capacitor,  $C_{\rm L}$ . S is turned off and the diode, D, starts to conduct the energy

from  $L_i$  and  $L_o$  is transferred to  $C_L$  and the output capacitor,  $C_o$ , respectively. Zeta converter is named by input-side non-cascaded converter because it can allow part of the input voltage source energy directly transferred to load at the switch turned-on stage.

# 3.2 Specifications of ISPFC

The first step is that defines the specifications of input-side non-cascaded power-factor-corrected switching regulator (ISPFC) and according the specifications to implement a practical switching regulator. In the following discussion, the switching regulator provides output power at low power level, and the pre-regulator, buck-boost converter, and voltage regulator, two-switched forward converter, are operated in CCM. The output power range of the switching regulator is 25 W to 110 W. The input voltage is 110 V RMS and the output voltage is 24 V DC, and the storage element, capacitor, voltage level should be lower than 250 V. The switching regulator must provide galvanic isolation between the input port and the output port. The switching frequency of two converters are 100 kHz that optimizes the size and switching loss of the converters. For the simple circuitries reason, two converters should be operated at hard-switching. The power factor of the switching regulator should be able to meet international standard, IEC 61000-3-2 [3].

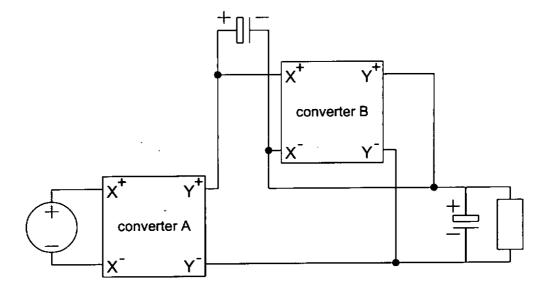

#### 3.3 Realization of ISPFCs

As the name implies, the input-side non-cascaded power-factor-corrected switching regulator, that the switching regulator allows the AC mains power directly flowing to voltage regulator. The block diagram of ISPFC is shown in Figure 2.19. The square boxes denote a simple converter and the arrows denote power flow path and their direction. The next logical step for realization is to place a simple converter to the square boxes. Figure 3.2 is shown the equivalent circuit of ISPFC. The terminals X<sup>+</sup> and X<sup>-</sup>, and Y<sup>+</sup> and Y<sup>-</sup> represent the input port, and the output port of the simple converter respectively. The simple converter circuits are shown in Figure 3.3, which illustrates a short

Figure 3.2: Equivalent circuit of ISPFC. Rectangular blocks denote converters.

circuit path of each converter. When places the simple converter into the square boxes, the care should be made to ensure that the short-circuit path imposed by the simple converters do not affect the intended connections.

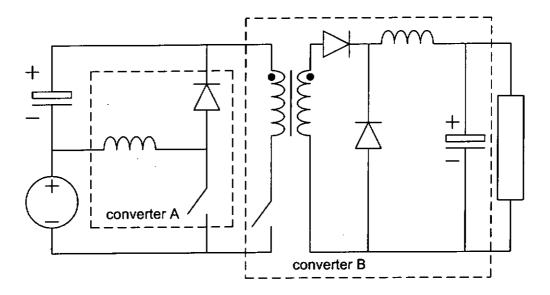

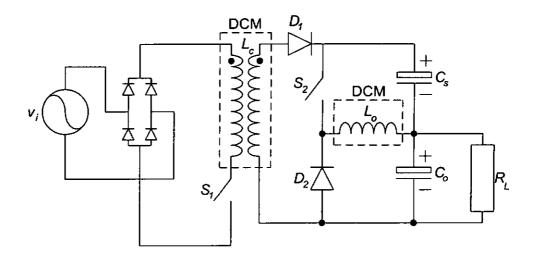

For example, from Figure 3.2 at the converter A the negative input terminal, X<sup>-</sup>, and the negative output terminal, Y<sup>-</sup>, must be without connected path in normal operation of this switching regulator. Because if these two terminals provide a short-circuit path, it means that makes a short circuit path occurred in the AC mains. Therefore the converter A should be a buckboost converter, but at the converter B it can be any simple converter. A possible solution for a non-isolated ISPFC using a buck-boost converter and a buck converter for converter A and converter B is shown in Figure 3.4. Using a buck converter places to converter B, because buck converter provides step down function for lower output voltage, which meets the specification discussed with previous section. Isolation is a compulsory requirement of the switching regulator. The next step is that changes the non-isolated ISPFC to become an isolated version. Because the AC mains has connected directly with the buck converter, the galvanic isolation transformer should be put on the converter B. buck converter. The isolated ISPFC is shown in Figure 3.5, the buck converter is replaced by forward converter for providing galvanic isolation.

Figure 3.3: Basic voltage converter circuits (a) Buck; (b) Boost; (c) Buck-Boost.

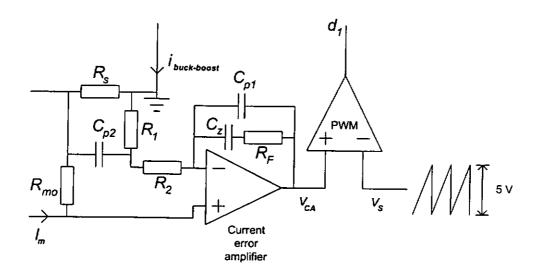

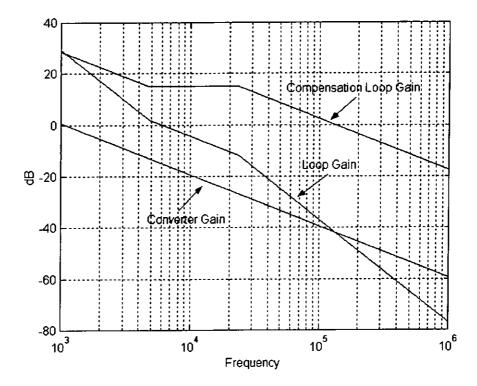

### 3.4 Analysis of ISPFC

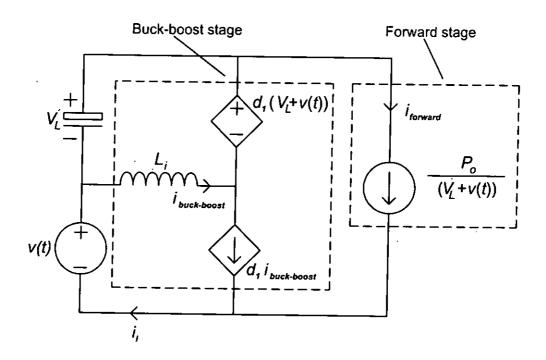

A detail numerical analysis is reported by Chow et al. [7]. Here describes the important aspects of this particular non-cascaded power-factor-corrected switching regulator in terms of circuit operation and control requirement. Figure 3.6 shows the average model of ISPFC, buck-boost converter and forward converter. It assumes that the storage element,  $C_{\rm L}$ , voltage is constant, and the input of buck-boost converter is connected to a rectified sinusoidal voltage:

$$v(t) = \hat{v}|\sin \omega_{\rm m} t| \tag{3.1}$$

The input to the forward converter is therefore given by

$$v_{\text{forward}} = V_{\text{L}} + \hat{v}|\sin \omega_{\text{m}} t| \tag{3.2}$$

where  $V_{\rm L}$  is the capacitor voltage,  $\omega_{\rm m}$  is the AC mains frequency. Suppose that the output voltage is well regulated by the forward converter. In the steady state, assume that the forward converter efficiency is unity, therefore the input current of the forward converter is given by

$$i_{\text{forward}} = \frac{P_{\text{o}}}{V_{\text{L}} + \hat{v}|\sin \omega_{\text{m}} t|}$$

(3.3)

Figure 3.4: A possible solution for non-isolated ISPFC using a buck-boost converter and a buck converter for converter A and converter B.

where  $P_0$  is the output power drawn by the output load. Referring to Figure 3.6, the input current can be expressed as the sum of  $d_1i_{\text{buck-boost}}$ , where  $d_1$  is the duty cycle of the buck-boost converter, and the current drawn by the forward converter

$$i_i = d_1 i_{\text{buck-boost}} + i_{\text{forward}} \tag{3.4}$$

Assumed that the switching regulator can achieve unity power factor,  $i_i$  is proportional to the input voltage waveform,  $i_i$  is expressed by

$$i_i = \hat{i}_i |\sin \omega_{\rm m} t| = \frac{2P_0}{\hat{v}} |\sin \omega_{\rm m} t| \tag{3.5}$$

As an observation from Equation 3.4,  $d_1i_{buck-boost}$  should be contain negative value when  $i_i$  is close to zero-crossing of the AC mains line cycle. The negative value can be reduced by increasing the storage element voltage level. Thus, this illustrates that the power factor of this particular switching regulator is below unity and it has a bit high total harmonic distortion when  $i_{\text{forward}}$  is increased, because  $i_i$  contains the DC current component.