### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

# A Study of Fault Detection Problems in Self-Checking Circuits

by

PANG Cho-Wai, Joseph, BEng(Hons)

A thesis submitted for the Degree of Master of Philosophy in the Department of Electronic Engineering of The Hong Kong Polytechnic University

> Department of Electronic Engineering The Hong Kong Polytechnic University

> > October 1997

### **Abstract**

The problems of self-checking circuits under different fault models such as multiple fault, open and bridging fault models were thoroughly examined and addressed. Various test generation and design-for-testability methods were investigated in order to find efficient solutions to tackle the problems. In particular, the following were achieved:

- The multiple stuck-at fault coverage problem was addressed. Off-line multiple stuck-at fault detection method was studied. In this study, a multiple stuck-at fault detection algorithm was developed for two-rail and parity checkers. The algorithm has been proved to achieve 100% multiple stuck-at fault coverage and requires less test vectors comparing to previously proposed method.

- The open and bridging fault coverage problems in CMOS circuits were studied, with particular emphasis on the bridging fault detection problem. Stuck-at fault model is insufficient and inadequate to model bridging faults in CMOS circuits. The detection of bridging faults by voltage testing is a very complicated task. We integrated the Iddq testing technique in the self-checking system and applied the test generation method to the two-rail checkers for bridging fault detection. By combining the multiple stuck-at fault detection and Iddq testing, the test quality can be greatly increased.

- The structures of domino-CMOS logic circuits are more testable than their static

family for transistor stuck-open and stuck-on faults. However, the dynamic nature

of the domino circuit structure prevents effective application of Iddq testing.

Modification of domino-CMOS logic circuits was proposed to enhance the overall

testability of both voltage and Iddq testing. Furthermore, the extra cost of hardware is also very low.

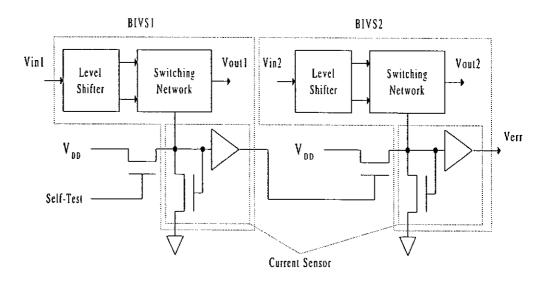

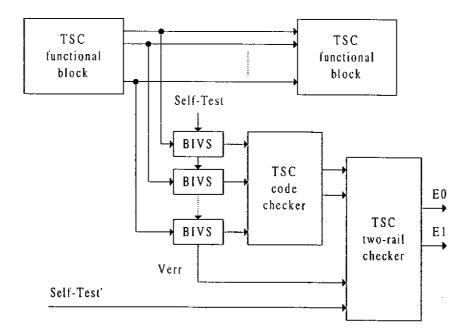

Another serious problem of the self-checking circuits is the misinterpretation of the output of the functional block due to the effect of bridging fault. In our earlier work, we focused on the use of built-in current sensor to detect bridging faults. However, Iddq testing is relatively slow in detection speed and suffers from low current resolution. The detection problem is mainly due to the occurrence of intermediate voltage at the fault site. In this respect, a sensing circuit called built-in intermediate voltage sensor(BIVS) was proposed to detect the intermediate voltage. Detailed analysis shows that the sensing circuit can achieve the self-checking requirements. So that it is suitable for on-line testing applications. An integration of BIVS and self-checking system is further proposed as an application example.

### **Table of Contents**

| Abstract                                     | i    |

|----------------------------------------------|------|

| Table of Contents                            | iii  |

| List of Figures                              | vi   |

| List of Tables                               | viii |

| List of Publications                         | ix   |

| Acknowledgements                             | X    |

| 1. Introduction                              | 1    |

| 1.1 Introduction                             | 1    |

| 1.2 Outline and Objectives of the Thesis     | 3    |

| 2. Background Theory                         | 7    |

| 2.1 Introduction                             | 7    |

| 2.2 Faults, Errors and Failures              | 7    |

| 2.3 Fault Models                             | 10   |

| 2.3.1 Logical Stuck-at Fault Model           | 10   |

| 2.3.2 Stuck-Open Fault Model                 | 12   |

| 2.3.3 Bridging Fault Model                   | 14   |

| 2.4 Basic Properties of Error-Detecting Code | 16   |

| 2.5 Summary                                  | 19   |

| 3. Self-Checking Circuits                    | 20   |

| 3.1 Introduction                             | 20   |

| 3.2 Self-Checking Circuits                   | 21   |

| 3.3 Self-Testing Checkers                    | 24   |

|    | 3.4 Summary                                             | 26 |

|----|---------------------------------------------------------|----|

| 4. | Analysis of Multiple Stuck-at Fault Coverage in SCCs    | 27 |

|    | 4.1 Introduction                                        | 27 |

|    | 4.2 Test Generation in Two-Rail Checkers                | 30 |

|    | 4.2.1 Test Generation Algorithm                         | 32 |

|    | 4.2.2 Fault Simulation                                  | 37 |

|    | 4.2.3 Validity of the Test Generation Method            | 38 |

|    | 4.2.4 Implementation of the Test Generation Method      | 42 |

|    | 4.2.5 Application of Test Generation in Parity Checkers | 48 |

|    | 4.3 Summary                                             | 51 |

| 5. | Testability Analysis and Detection of Transistor        | 52 |

|    | Faults in CMOS VLSI Circuits                            |    |

|    | 5.1 Introduction                                        | 52 |

|    | 5.2 Testability Analysis of Static CMOS Logic Circuits  | 53 |

|    | 5.2.1 Stuck-Open Fault                                  | 53 |

|    | 5.2.2 Bridging Fault                                    | 55 |

|    | 5.2.3 Integration of Iddq Testing with TSC System       | 59 |

|    | 5.2.4 Application Example                               | 65 |

|    | 5.3 Testability Analysis of Domino-CMOS Logic Circuits  | 70 |

|    | 5.3.1 Iddq Testability                                  | 72 |

|    | 5.3.2 Testability Improvements                          | 78 |

|    | 5.4 Summary                                             | 83 |

| 6. | Built-in Intermediate Voltage Sensor                    | 84 |

|    | 6.1 Introduction                                        | 84 |

|    | 6.2 Design of Sensing Circuit                           | 86 |

|    | 6.3 Testability Analysis of BIVS System                 | 93 |

| 6.4 BIVS System Design and Its Application                          | 96  |

|---------------------------------------------------------------------|-----|

| 6.4.1 BIVS System Design                                            | 96  |

| 6.4.2 Integration of BIVS System with Totally Self-Checking Circuit | 97  |

| 6.5 Summary                                                         | 99  |

| 7. Conclusions and Future Works                                     | 100 |

| 7.1 Conclusions of Present Works                                    | 100 |

| 7.2 Future Works                                                    | 104 |

| References                                                          | 105 |

## **List of Figures**

| Figure 2.1  | Illustration of the application of the logical stuck-at fault model. | 1 1 |

|-------------|----------------------------------------------------------------------|-----|

| Figure 2.2  | CMOS two-input NAND gate.                                            | 13  |

| Figure 2.3  | Bridging fault between two outputs of inverters.                     | 15  |

| Figure 3.1  | Block diagram of a self-checking system.                             | 21  |

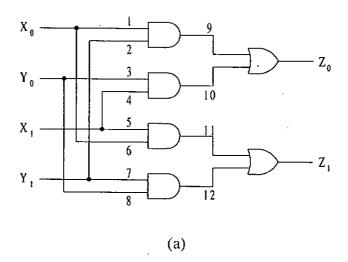

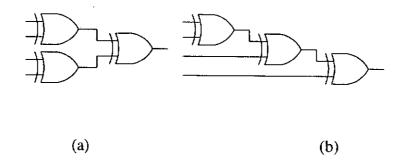

| Figure 4.1  | Three types of 2-pair TRC, (a) AND-OR, (b) NAND, and (c)             | 32  |

|             | NOR gates implementation.                                            |     |

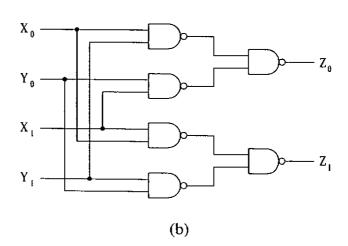

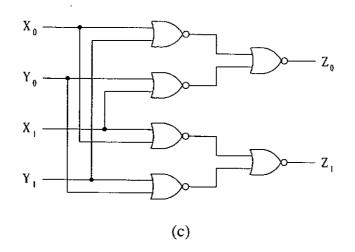

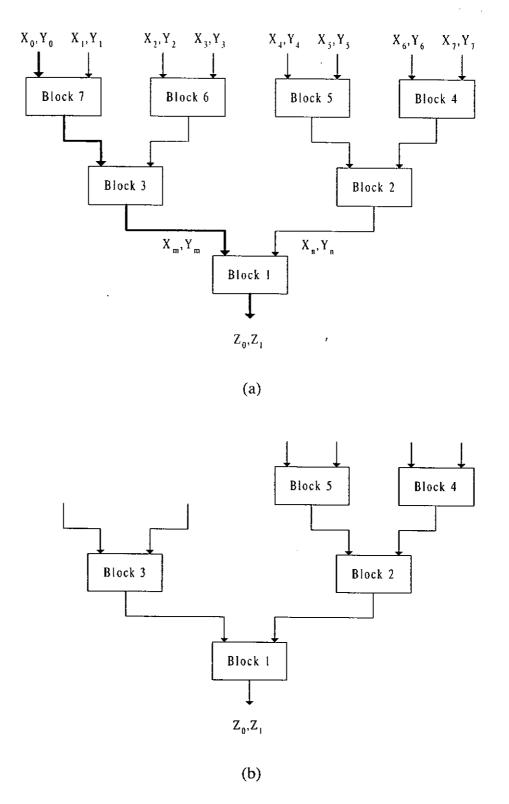

| Figure 4.2  | Construction of TRCs using the 2-pair TRC as basic building          | 33  |

|             | blocks, (a) complete tree structured 8-pair TRC, and (b)             |     |

|             | incomplete tree structured 6-pair TRC.                               |     |

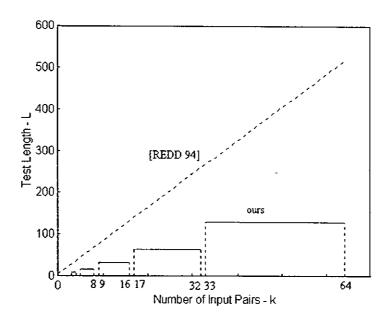

| Figure 4.3  | Test length comparison in terms of input pairs.                      | 37  |

| Figure 4.4  | An example of 6-pair TRC.                                            | 44  |

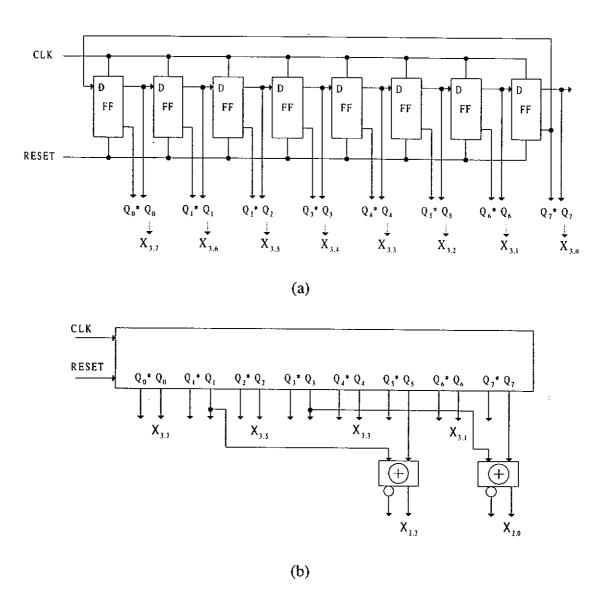

| Figure 4.5  | LFSRs for (a) Figure 4.2(a), and (b) Figure 4.2(b).                  | 47  |

| Figure 4.6  | Examples of two different parity tree configurations.                | 49  |

| Figure 4.7  | Example of test generation of parity tree.                           | 49  |

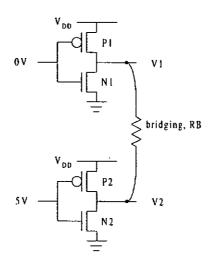

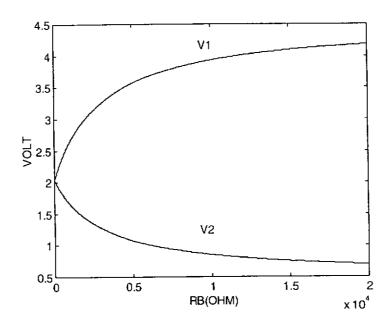

| Figure 5.1  | Bridging between two outputs of inverters.                           | 55  |

| Figure 5.2  | Plotting of output voltages of two inverters with different          | 58  |

|             | bridging resistance.                                                 |     |

| Figure 5.3  | Plotting of Ids versus different bridging resistance.                | 58  |

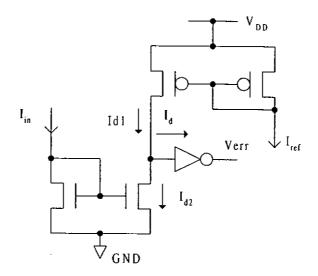

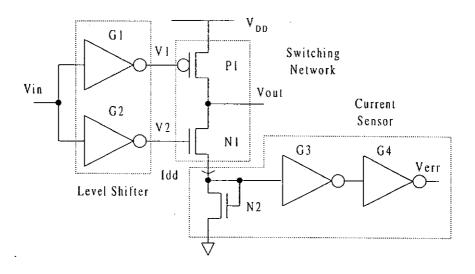

| Figure 5.4  | Built-in current sensor.                                             | 60  |

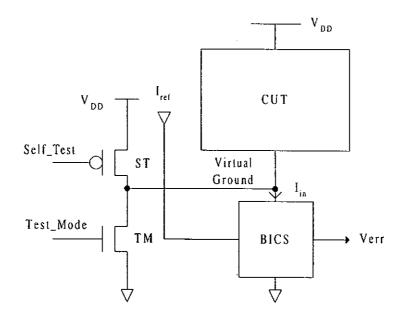

| Figure 5.5  | Application of BICS.                                                 | 61  |

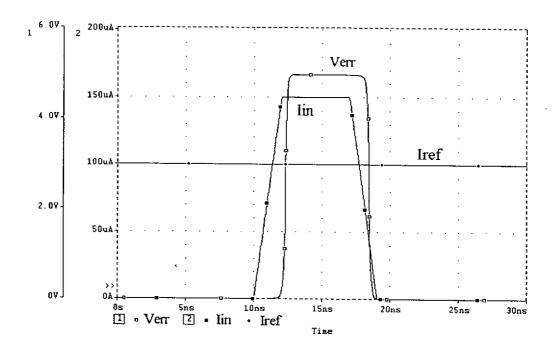

| Figure 5.6  | Output of the BICS corresponding to a faulty circuit.                | 62  |

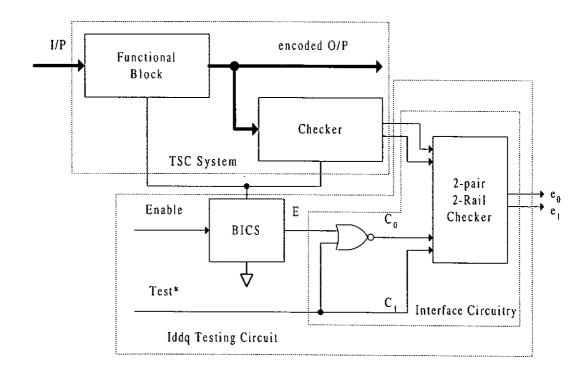

| Figure 5.7  | Additional testing circuitry for Iddq testing in TSC circuit.        | 63  |

| Figure 5.8  | A NOR-type 2-pair two-rail checker.                                  | 66  |

| Figure 5.9  | Bridging faults at block level.                                      | 68  |

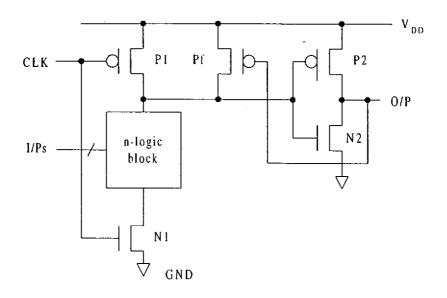

| Figure 5.10 | A domino-CMOS logic circuit.                                         | 72  |

| Figure 5.11 | (a) Domino-CMOS logic circuit, (b) gate-level representation,        | 73  |

|             | and (c) modified gate-level representation                           |     |

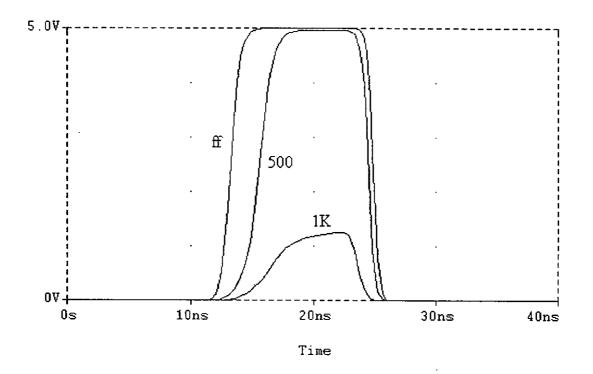

| Figure 5.12 | Output waveforms under different drain-source bridging                      | 76 |

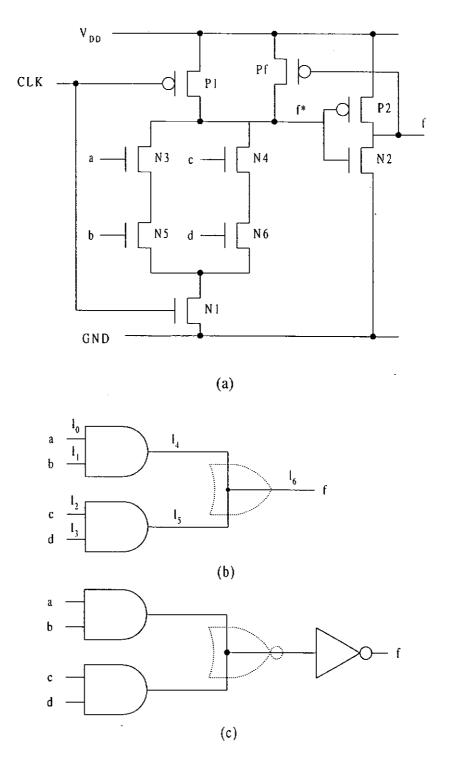

|-------------|-----------------------------------------------------------------------------|----|

|             | resistance.                                                                 |    |

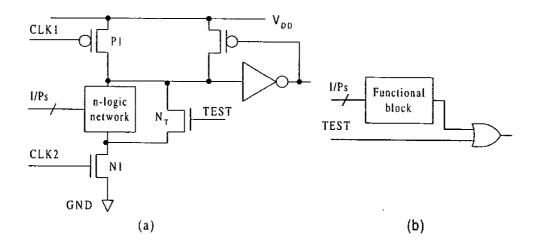

| Figure 5.13 | (a) Modified domino-CMOS gate, and (b) equivalent gate-level                | 79 |

|             | representation.                                                             |    |

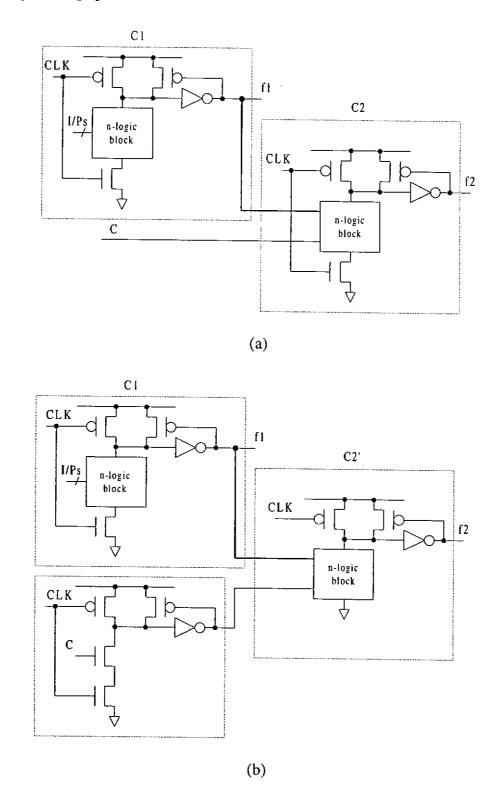

| Figure 5.14 | Example of domino-logic circuit, (a) original, and (b) modified             | 81 |

|             | one.                                                                        |    |

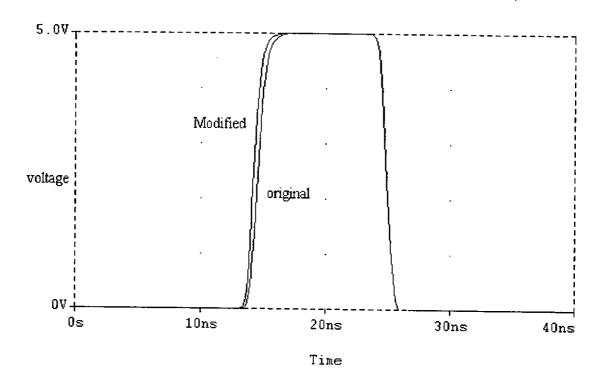

| Figure 5.15 | Comparison of output waveforms of original domino-CMOS                      | 82 |

|             | gate and modified one of Figure 5.11(a).                                    |    |

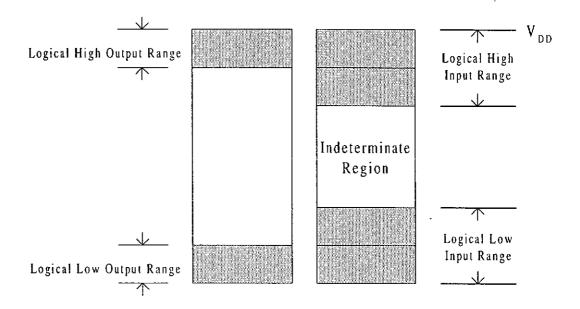

| Figure 6.1  | Definitions of input and output logical range.                              | 87 |

| Figure 6.2  | Built-in intermediate voltage sensor(BIVS).                                 | 88 |

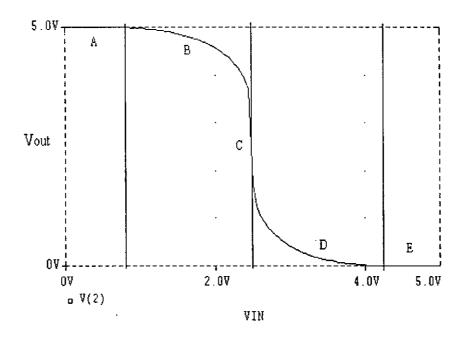

| Figure 6.3  | CMOS inverter DC transfer characteristic and operating regions.             | 90 |

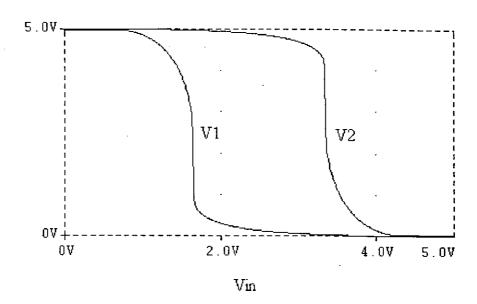

| Figure 6.4  | Output voltage of inverters G1 and G2 respect to the input                  | 91 |

|             | voltage.                                                                    |    |

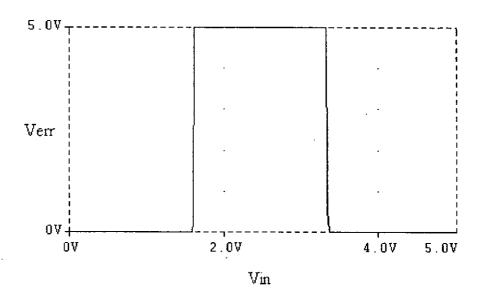

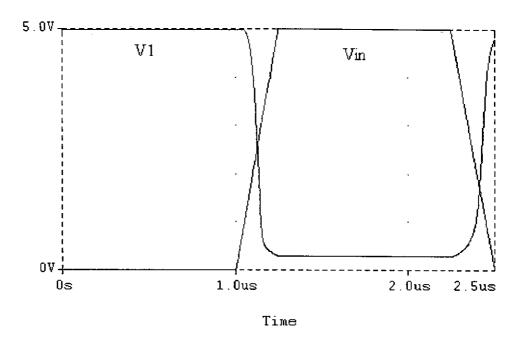

| Figure 6.5  | Error output of BIVS respect to the input voltage.                          | 92 |

| Figure 6.6  | Voltage V1 respect to the input voltage in under transistor P <sub>G1</sub> | 95 |

|             | stuck-on.                                                                   |    |

| Figure 6.7  | BIVS system.                                                                | 96 |

| Figure 6 8  | Integrating of a RIVS system and a TSC circuit                              | റം |

### **List of Tables**

| Table 2.1 Outputs of a fault-free and a stuck-at 1 AND gate.                      | 11 |

|-----------------------------------------------------------------------------------|----|

| Table 2.2 Truth table for CMOS NAND gate.                                         | 14 |

| Table 4.1 Test vectors determined for Figure 4.2(a).                              | 36 |

| Table 4.2 Multiple fault diagnosis of a 2-pair TRC.                               | 39 |

| Table 4.3 Diagnosis of two-rail checker having the outputs responses equal to     | 40 |

| the complement of fault-free ones.                                                |    |

| Table 4.4 Re-arrangement of Table 4.1.                                            | 46 |

| Table 5.1 The operation conditions of transistors P1 and N2 under bridging        | 57 |

| fault condition.                                                                  |    |

| Table 5.2 Summary of the operation for Iddq testing circuit.                      | 63 |

| Table 5.3 Output of transistor stuck-on fault in CMOS NOR gate(of Figure          | 64 |

| 5.8(b)).                                                                          |    |

| Table 5.4 Iddq in static CMOS NOR gate(of Fig. 5.8(b)) under intratransistor      | 70 |

| bridging faults.                                                                  |    |

| Table 5.5 Test vectors for circuit Figure 5.11(b) based on logic testing.         | 74 |

| Table 5.6 Test results of intratransistor bridging faults of Figure 5.11(a) based | 75 |

| on Iddq testing.                                                                  |    |

| Table 6.1 Summary of transistor sizes.                                            | 88 |

| Table 6.2 Summary of CMOS inverter operation.                                     | 90 |

| Table 6.3 Rehaviour of RIVS in the presence of transistor faults                  | 02 |

### **List of Publications**

#### **JOURNAL PAPER:**

J. C. W. Pang, M. W. T. Wong, and Y. S. Lee, "An efficient test generation for multiple fault coverage of two-rail checkers", International Journal of Electronics, 83, 6, Dec. 1997, pp. 837-848.

#### **CONFERENCE PAPERS:**

- J. C. W. Pang, M. W. T. Wong, and Y. S. Lee, "An efficient test generation for multiple fault coverage in two-rail checkers", Proc. 2<sup>nd</sup> IEEE Int'l On-Line Testing Workshop, France, pp. 118-123, July 8-10, 1996.

- J. C. W. Pang, M. W. T. Wong, and Y. S. Lee, "Hybrid test generation approach for multiple fault detection of TSC system implemented with CMOS two-rail checker", 7<sup>th</sup> Int'l Symp. On IC Technology, Systems and Applications(ISIC-97), Singapore, Sept. 10-12, 1997.

- J. C. W. Pang, M. W. T. Wong, and Y. S. Lee, "Design and implementation of strongly code-disjoint CMOS built-in intermediate voltage sensor for self-checking circuits", accepted for presentation in Asian Test Symposium 1997(ATS'97), Japan, Nov 17-19. 1997.

- J. C. W. Pang, M. W. T. Wong, and Y. S. Lee, "On testability analysis of domino-CMOS logic circuits", accepted for presentation in 7<sup>th</sup> Symp. on Fault Tolerant Computing(CFTC-7), China, Dec. 11-12, 1997.

### **Acknowledgements**

I am indebted to express my sincere gratitude to everyone who giving up their time and support to this research.

Thanks to Dr. Mike W. T. Wong, my chief supervisor, for his valuable advice and helpful assistance. Without his intensive knowledge, initiative and great insight, the goal of this research work would not be achieved successfully. I have got great benefit by his guidance, supervision and encouragement. Both of my knowledge and character are improved.

I wish also to thank Professor Y. S. Lee, my second supervisor, for his ever-ready support and many thoughtful suggestions. His enthusiasm and experience enriched my research work.

Finally, thanks to the Hong Kong Polytechnic Research Committee for providing financial support and without which support, the research would be nothing more than an idea.

### Chapter 1

### Introduction

### 1.1 INTRODUCTION

Digital systems have been widely adopted in the past decades and become irreplaceable in modern society. Computing systems, communication networks, control systems are made possible by the advance in microelectronics technology such that the performance of these systems is greatly increased. As our real life becomes inseparable from them, these systems should be built with as high quality as possible.

A global concept called dependability which subsumes the usual attributes of reliability, availability, safety, maintainability, performability and testability describes the quality of a system [PRAD 86][JOHN 89]. High dependability is always desired. However, physical defects, imperfection or flaws may occur in the system during manufacturing phase, or even in operating phase. Periodic off-line testing may be used to discover any defects before shipping the products to the customer, but it is not effective to detect the temporary faults. Once the product is working in normal operation, errors produced by hardware faults will remain undetected until the test phase. Also, off-line testing is not effective against temporary faults. Those factors will affect the quality of a system. Furthermore, design error is also the main source of error. In order to build a highly dependable system, fault-tolerant(FT) design

techniques have been proposed. Two major goals of FT system are: 1) the system is capable of producing correct output under the occurrence of some restricted error types, and 2) the system is capable of producing extra signal to indicate the error under the occurrence of some restricted error types. Consequently, the availability and reliability can be significantly increased.

Nowadays, FT systems have been widely used to provide highly reliable and safe-critical applications. However, there are some drawback from the existing design techniques. For example, in a triple modular redundancy(TMR) system [PRAD 86][JOHN 89], a voter performs majority vote on the outputs of three identical systems. Any single system error will be masked at the output of the voter. However, the voter is not checked. Also, large cost due to additional hardware is required. Generally, the problem of "checking the checker" becomes the major difficulty in FT design.

Based on this observation, the development of totally self-checking(TSC) goal is motivated. That is, the first erroneous output of the functional block or checking circuit(checker) must be a non-codeword. Basically, in TSC system, the functional block is monitored by a checker concurrently. The necessary mathematical properties that the circuits must be verified in order to achieve the TSC goal were firstly introduced by [CART 68]. Later, the largest class of TSC functional circuits were defined in [ANDE 71][SMIT 78]. More recently, the largest class of checkers necessary to ensure the TSC goal has been defined by [NICO 88].

Synthesis of self-checking circuits is a major topic in FT field. The design methods of the checkers have been intensively studied by [ADER 71][ADER 73][REDD 74][MARO 78][HUGH 84][KHAK 84][FUJI 87][MIN 88][LO 90][PASC 90][FUJI 91][OZGU 91][TAO 92][RAO 93][BURN 94][METR 94a][REDD 94][DIMA 95]. Design methodologies for functional circuits can be found in [HIRA 91][BUSA 94][SAPO 96]. In practice, the effectiveness of TSC property is dependent on the predetermined fault model. That is, all possible faults in the predetermined fault model must satisfy the mathematical properties of TSC goal. In most of the studies, the fault model used is the single stuck-at fault model. Several design methods for different checkers based on the PLA implementation have been developed [MIN 88][HATA 91][TAO 92]. Furthermore, it has been showed that dynamic CMOS and NMOS logic circuits are more applicable to realise self-checking circuit(SCC) designs rather than fully static CMOS family under the realistic fault model such as open fault [JHA 84][JHA 90][CHEE 92]. Generally, there is still no design methodology to achieve high realistic fault coverage in SCCs.

### 1.2 OUTLINE AND OBJECTIVES OF THE THESIS

In our study, two major areas have been identified which are important in SCC designs. They are, namely, the multiple fault problem and the realistic fault coverage problem. Firstly, multiple fault is the concurrently occurrence of two or more than two faults in the circuit. In the past decades, automatic test pattern generation(ATPG) algorithms have been developed based. These are on the single stuck-at fault model only because the computational complexity of multiple fault is very large [FUJI 85][ABRA 90]. Also, for on-line testing approach, single fault model is used because

it is very hard to implement a TSC system under multiple fault assumption [NANY 88][NICO 89a]. However, many physical defects may only be modelled as multiple faults. Therefore, the ability to detect the multiple faults in early stage is highly desired.

Secondly, in order to enhance the quality of testing scheme, realistic fault detection must be considered. As reported in [WADS 78][GALI 80][LEVI 81][MALA 82][SHEN 88][SHER 88][STOR 90][FERG 91][STOR 91][LIDE 92][LEE 96a][LEE 96b][WEN 97], realistic faults such as bridging faults and open faults are hard to be detected by logic testing approach because they include the degradation in certain parameters such as voltage, current and timing. Furthermore, these faults may not result in logical error at the primary output node such that they are hard to be detected. Recently, the fault coverage problem of present SCCs have been investigated by [JHA 84][JHA 90][MILL 91][LIDE 92][JHA 93][NICO 94]. Different techniques to handle this problem were carried out by [JHA 84][NICO 91][CHEE 92][LO 95][METR 95][FAVA 96]. In particular, modification of the circuit layout may be required in their methods which may not easily apply to existing CAD tools. In our study, we have extended our study to realistic fault model and to explore methods to tackle the problem more effectively.

The main contents of this thesis are as follows:

• To review the concept of fault, error and failure and also the principle of coding theory are discussed. And to study the principles and concepts of self-checking properties as background knowledge to support the work to be presented.

- To study the multiple fault testability of existing self-checking circuits. Off-line multiple stuck-at fault detection methods were studied. In the following study, attention is focused on the following two important issues of existing self-checking circuits: 1) present TSC circuits are designed to achieve concurrent error detection of single fault only, but not multiple fault and 2) although off-line testing for multiple fault is very important, very little work has been done in this area. In this thesis, extensive coverage on the multiple fault detection problem of two-rail and parity checkers will be included. The fundamental benefit of multiple fault detection allows the selection of high quality circuits during manufacturing test, resulting in higher mean-time-to-failure.

- To study the realistic fault coverage problem in static CMOS self-checking circuits. Stuck-at fault model is insufficient and inadequate to model many CMOS faults. In this thesis, we are mainly concerned with the detection of bridging fault because this kind of fault is hard to be detected by logic testing. We shall integrate Iddq testing method with the logic testing approach. Based on this implementation, an example of detecting bridging fault in two-rail checkers will be used to show the effectiveness of our implementation.

- To improve the Iddq testability in domino-CMOS logic circuits. The structures of domino-CMOS logic circuits are more testable than their static family for transistor stuck-open and stuck-on faults. However, the inherent dynamic structure prevents

the application of Iddq testing. Modifications of domino-CMOS logic circuits are proposed to enhance the overall testability of both logic and Iddq testing.

To study the bridging fault detection problem for on-line testing application. In the previous work, we have focused on the use of built-in current sensor(BICS) to detect bridging faults. However, Iddq testing is relatively slow in detection speed and suffers from low current resolution. The detection problem is mainly due to the occurrence of intermediate voltage(indeterminate logic value) at the fault site. Problem arises especially when this effect appears at the input of the checker. The checker may fail to detect it. Alternative method called built-in intermediate voltage sensor(BIVS) to detect the intermediate voltage is proposed. Detailed analysis will be carried out to show the effectiveness of BIVS. The integration of BIVS and self-checking system is also proposed as an application example.

To summarise, the main aims of this research are: i) in-depth study of the fault coverage problems of SCCs under different fault models, and ii) design and implement effective solutions in terms of different detection and design-for-testability techniques for these problems.

### Chapter 2

### **Background Theory**

### 2.1 INTRODUCTION

In this chapter, we shall present the basic terminology and the definitions of several key concepts used in the fault-tolerant field as the background knowledge for this research work. It is imperative to state any technical terms used clearly because there are ambiguities arising from different interpretation of the same word. For example, [JOHN 89] has defined physical defects as faults while [PIES 95] has considered that a failure is a physical defect. This provides the basis for a good overall understanding of the causes of faults, the types of faults and the effects of the faults which are essential in this study. Furthermore, the important aspect of fault-tolerant computing field and the properties of error-detecting codes will be discussed.

### 2.2 FAULTS, ERRORS and FAILURES

Here we concern the definitions of faults, errors and failures in a digital system. The terminology presented here is based on [JOHN 89] whose definitions are widely accepted in the field.

**Definition 2.1.** A fault is a physical defect, imperfection, or flaw that occurs within some hardware component in a circuit. Examples of faults include bridging between two electrical conductors, a break or open in conductors, or physical flaws or imperfections in semiconductor devices such that the parameters are not within the specifications.

Faults can be classified as logical or parametric, and permanent or temporary. A logical fault is one that causes the logic function of a circuit element to be changed to some other logic function. The typical example of logical faults is logical stuck-at-z fault (s-at-z). This fault model assumes that the logic value on an input or output line of a circuit element is set to logic z permanently, independently of the input value applied to the faulty line. On the other hand, a parametric fault may result in degradation in circuit parameters, causing a change in magnitude of some factors such as signal timing, current, or voltage. Examples of these faults may include bridging faults and open faults.

Further classification of faults may include the time of duration. Permanent faults that always present and do not disappear, or change their nature during testing. These faults are mainly due to the imperfection in the manufacturing process. Temporary faults, which have been predominant in modern digital system, include two types of faults: transient faults and intermittent faults. Transient faults are faults which may appear once and may never appear again. It may be caused by power supply fluctuation, electromagnetic perturbations, temperature and humidity variation, radiation etc. Intermittent faults may appear, disappear and then reappear repeatedly. Hence, there are no reliable means of detecting their occurrences of temporary faults

because they may disappear when a test is applied or may appear during system runtime. The early detection of temporary faults for the reliable operation of the system is very important, hence it motivates the development and implementation of fault-tolerant techniques to detect or tolerate the occurrence of temporary faults as well as permanent faults during the system's life cycle.

**Definition 2.2.** An error is the manifestation of a fault. In other words, it is the occurrence of an incorrect state at the observation nodes caused by faults within a circuit. For example, a fault occurs inside a circuit and is activated by suitable inputs, the effect may only be observed at the primary output of the circuit. If the observed output deviates from the normal one, an error in operation of the circuit is occurred.

**Definition 2.3.** A failure occurs in a digital system when the system performs one of its functions incorrectly. It is also considered as the under specifications of same functions in terms of quantity and quality.

It is clear that there are cause-and-effect relationship between faults, errors and failures. Faults, when activated, may result in an error. However, error may not occur if the fault is redundant or the effect of the activated fault is negligible. When a system experiences errors, it may be lead to failures. From another point of view, errors are the effect of faults, and finally, failures are the effect of errors.

. 212

### 2.3 FAULT MODELS

Throughout our research, it is necessary to pre-determine the kinds of faults that we are considering in the analysis. In practice, large numbers and types of probable defects can happen, in order to make the analysis more effective and more meaningful, only a subset of all possible faults will be considered. This is because the complexity of analysing multiple fault coverage is too high and some faults may not occur in a particular technology.

Fault model allows us to specifically define the types and the numbers of faults. In our study, we consider three primary fault models: 1) logical stuck-at fault model at gate-level, 2) stuck-open fault model, and 3) bridging fault model at the transistor-level.

### 2.3.1 Logical Stuck-at Fault Model

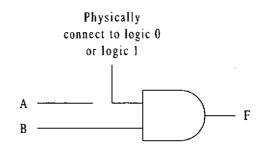

The most common fault model is the logical stuck-at fault model or simply the stuck-at fault model. This fault model includes two types of faults: 1) stuck-at 0 fault (s-at 0), and 2) stuck-at 1 fault (s-at 1). Stuck-at z fault assumes that the faulty circuit node is set to value logic z permanently, independent to the applied value on the node. This fault model is most popular because it is simple and easy to manipulate. Also, it can represent a large number of possible defects in the circuit. Figure 2.1 further illustrates the application of stuck-at fault model. For example, an input of an AND gate is stuck-at 1 (e.g. line A is stuck-at 1). It is easy to verify that when the input vector AB is 10 or 11, the fault-free gate produces correct output value 0 and 1 respectively.

However, when the stuck-at fault is activated, it produces incorrect output. Table 2.1 summaries the operation of a fault-free and faulty AND gate to demonstrate the stuck-at fault model. In this example, we also demonstrated how a fault is activated. A fault is considered as important when it can result in an error.

**Figure 2.1** Illustration of the application of the logical stuck-at fault model.

**Table 2.1** Outputs of a fault-free and a stuck-at 1 AND gate.

| Input test vector AB | fault-free output | faulty output |

|----------------------|-------------------|---------------|

| 00                   | 0                 | 0             |

| 01                   | 0                 | 1             |

| 10                   | 0                 | 0             |

| 11                   | 1 .               | 1             |

Usually, in most test generation algorithms, testability analysis and fault-tolerant system designs, single s-at fault model is assumed. For a circuit with n nodes, it will have at most 2n number of s-at faults. However, there will be 3<sup>n</sup>-1 possible multiple s-at faults. The computational complexity of multiple stuck-at fault grows exponentially as the circuit size increases. On the other hand, it has been shown in

[ABRA 90] that test set for single s-at fault coverage also provides a very high fault coverage of multiple s-at fault as well. In general, it is restricted to single fault because it is very hard to design a fault-tolerant system that is capable of handling multiple faults [NICO 89].

As CMOS technology becomes the most popular VLSI design technology, it is necessary to verify the effectiveness of the s-at fault model versus the actual CMOS VLSI circuit faults. Stuck-at fault model is found to be insufficient and inadequate to model CMOS VLSI circuits faults [GALI 80][MALA 82][WADS 78]. Bridging and open faults are the most representative CMOS VLSI circuit faults, however, these two faults cannot be represented by stuck-at faults precisely. In order to model these faults accurately, it is necessary to extend our fault model to transistor-level as opposed to gate-level. Transistor-level fault model is sometimes known as switch-level fault model because a transistor is essentially performing a switching function.

#### 2.3.2 Stuck-Open Fault Model

It might be thought that all the silicon chips that are processed using a set of correctly designed photomasks would work at the first time. Practically, this is not the case. Defects may occur at manufacturing stage or during the chip's life cycle. Stuck-open fault is a fault in which there is a break at the conductor. It might result in misalignment of different masks during VLSI manufacturing process, over-removal of polysilicon and metal during etching, failure in cutting oxide windows, etc. Examples of electromigration and corrosion of metal due to trapped moisture can result in stuck-open fault during the chip life-cycle. In general, stuck-open fault will result in high

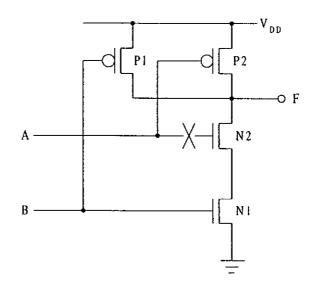

impedance at the fault site. It may turn the combinational circuit into a sequential one. An example of CMOS two-input NAND gate as shown in Figure 2.2 illustrates the behaviour of stuck-open fault. Assume that a break occurs between line A and gate node of transistor N2. This fault prevents the conducting of transistor N2 while input AB is set to 11. That is, output F is at high impedance state. As a result, the value of F is depending on the previous state. Table 2.2 shows the truth table for the two-input CMOS NAND gate for both the fault-free and faulty conditions. Based on this observation, two-pattern tests is required to detect stuck-open fault [GALI 80][MALA 82][WADS 78]. Based on this technique, firstly a suitable input pattern initialises the output of a gate to a known state. Then, another input pattern, which normally produces a complement output to the previous one, is applied. If the output of the gate does not toggle, stuck-open fault is detected.

Figure 2.2 CMOS two-input NAND gate.

Table 2.2 Truth table for CMOS NAND gate.

| Input pattern AB | Fault-free output | Faulty output  |

|------------------|-------------------|----------------|

| 00               | 1                 | 1              |

| 01               | 1                 | 1              |

| 10               | 1                 | 1              |

| 11               | 0                 | Previous state |

### 2.3.3 Bridging Fault Model

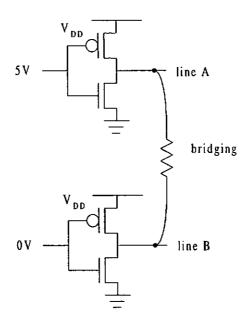

Bridging fault is caused by an excess connection between two nodes. This fault is activated when the bridged two nodes are set at different logic values. The effects of bridging faults are dependent on the process technology used. For some technologies such as TTL and ECL, wired-AND or wired-OR model is valid since they are either logic high dominate or logic low dominate. However, it has been shown that these two models are inadequate for CMOS technology [GALI 80][LEVI 81][MALA 82][SHEN 88].

For CMOS logic gate, a logic high at the output of a gate means that there is at least one serial connection of PMOS transistor(s) connecting to the V<sub>DD</sub> node. On the other hand, a logic low at the output of another gate means that there is at least one serial connection of NMOS transistor(s) connecting to the ground node. If the two output lines are bridged, the output voltages of the two gates will depend on the resistance of the pull-up transistor(s), the resistance of the pull-down transistor(s) and the bridging resistance [LEE 96a][LEE 96b][STOR 90][TANG 95]. For example, let

A and B be the two bridged lines. Let the correct value of A be logic 0 and of B be logic 1 and let I be the indeterminate voltage. When the resistance of the bridging is increased, the current across the bridging branch will be decreased. Thus, the voltage at A will move from I to 0 and the voltage at B will move from I to 1. Hence, when the short resistance is increased, this effect is amplified. Based on the above observation, it can be seen that the resultant value of the two bridged lines can be any value between V<sub>DD</sub> and ground providing that voltage at line B is always larger than voltage at line A. Bridging faults can occur between any two electrical nodes in the circuit. In practice, the occurrence of bridging faults is dependent on the physical layout of the circuit. In most cases, intratransistor bridging faults and gate-level bridging faults are the most popular and are considered in detailed in our study.

Figure 2.3 Bridging fault between two outputs of inverters.

For most practical purposes, most faults resulting from physical defects can be modelled by stuck-at, stuck-open or bridging faults. However, not all faults can be modelled by these fault models, for example, such as crosspoint faults in PLA, delay faults etc. In this thesis, we shall consider stuck-at, stuck-open and bridging faults only.

### 2.4 BASIC PROPERTIES OF ERROR-DETECTING CODE

On-line testing schemes are usually based on redundancy techniques: hardware redundancy and information redundancy. Information redundancy is the addition of extra information by means of encoding of data with an error-detecting code(EDC) or an error-correcting code(ECC). Popular coding schemes such as parity, two-rail code, Berger code, Hamming code are used in information redundancy. Hardware redundancy is the addition of extra hardware for the purpose of either fault detection or fault tolerance. For self-checking designs, both redundancy techniques are implemented. Self-checking circuits(SCCs) are designed based on hardware encoding techniques such that the output is a kind of EDCs. Extra hardware is always required in order to achieve the totally self-checking(TSC) goal [BUSA 94][LALA 85]. In this section, we briefly introduce the basic properties of error-detecting code used in digital systems [PIES 95][PRAD 86].

For a combinational circuit of n input lines and m output lines, there will be  $2^n$  number of input data and  $2^m$  number of output data. In order to distinguish the status of the circuit easily, SCCs are implemented such that a subset of all possible output space C, called codewords, will be produced and will be considered as correct outputs

during on-line normal operation. And non-codewords are considered as errors. Then, the status of the circuit can be identified. In general, the output of the SCCs is encoded to a kind of EDCs such as parity code, residue code, Berger code, m-out-of-n code, etc. We explain the properties of EDC as follow:

**Definition 2.4.** For any two codewords(say  $C_1$  and  $C_2$ ) in code space C, if the number of different bits between  $C_1$  and  $C_2$ (Hamming distance) is equal to or larger than 2,  $C_1$  is capable of detecting any single bit error. For example, given two odd parity codewords 0111 and 0010, differ in two positions. Therefore, the Hamming distance is 2. And clearly, if codeword 0111 is contaminated by a single bit error, it will be changed to an even parity word and error is detected.

**Definition 2.5.** Given two codewords  $C_1$  and  $C_2$  in code space C. We say that  $C_1$  covers  $C_2$  if and only if  $C_1$  has 1s everywhere  $C_2$  has 1s. If neither  $C_1$  covers  $C_2$  nor  $C_2$  covers  $C_1$ , C is called an unordered code. For unordered code, the minimum Hamming distance of the code is always larger than or equal to 2. That is, it can detect any single or unidirectional error. Therefore, Berger code is more effective in error detection than parity code.

**Definition 2.6.** A code is called systematic if the information bits and the check bits are separable. For example, Berger code is a kind of systematic code, while m-out-of-n is non-systematic code.

The selection of a EDC in a particular application may be dependent on the following factors:

- In many applications, more than one output line can be affected by a fault inside

the circuit. The circuit is modified such that any fault will produce single or

unidirectional errors. So, unordered code may be suitable for this kind of

applications.

- 2. Systematic code is convenient to use because the information is separable. The self-checking circuit is also easier to modify or design. For non-systematic code, extra decoding hardware is always necessary to produce the required outputs and the decoding hardware is not "protected" by any coding technique. On the other hand, many circuits such as PLA-based design circuits have shown the use of non-systematic code efficiently.

- 3. Since self-checking design always introduces extra hardware (for both the modification of the functional circuit and the checker), the circuit complexity and the speed degradation become important considerations.

The effectiveness of encoding the output of a digital circuit in a suitable EDC is highly dependent on the effect of the faults inside the circuit. As demonstrated in previous paragraphs, existing EDCs for digital systems are capable of detecting single or unidirectional bit errors, but not multiple random bit errors. That is, it is necessary to verify that all possible faults inside the circuit will only result in single and unidirectional bit errors. Otherwise, these faults may not be detected by the monitoring circuitry. Hence, a class of circuits called self-checking circuits are defined to achieve this requirement. Details of which will be introduced in the next chapter.

### 2.5 SUMMARY

In this section, we introduced several terminology in the fault-tolerant computing field. Relationships between faults, errors and failures were clearly defined. In practice, we shall consider the fault models and error models only. Usually, stuck-at fault model is adopted. However, stuck-at fault model is inadequate and insufficient to represent stuck-open and bridging faults in CMOS VLSI circuit. We have extended our consideration to include the more realistic faults. Finally, we have explained in detail the properties of error-detecting code. EDC plays an important role in fault-tolerant field. Equipped with this knowledge, we can define the error model more accurately and we can implement the fault-tolerant computing system more effectively.

### **Chapter 3**

### **Self-Checking Circuits**

### 3.1 INTRODUCTION

The use of self-checking system was motivated by the low reliability of the components in the past. As the design and manufacturing technology advances, component reliability has been significantly improved. On the other hand, the complexity of VLSI circuits grows quickly with the decreasing size of internal devices. However, as the complexity of circuit and system increases, the cost of testing such complicated system grows rapidly. Also, the systems are more and more prone to temporary faults [MASA 88]. These intermittent and transient faults are hard to detect by the traditional off-line testing approach. To meet the challenge, concurrent error detection(CED) by the self-checking design technique providing efficient on-line testing capability is required. The implementation of self-checking technique requires extra overhead. However, the gain in system quality and reliability outweighs the cost of additional circuitry.

The objective of designing self-checking circuits is to achieve the totally self-checking(TSC) goal, that is, the first erroneous output of the functional circuit must not belong to the output code. The necessary mathematical properties that the circuits must have in order to achieve the TSC goal was firstly introduced by [CART 68].

Later, the largest class of TSC functional circuits were defined in [ANDE 71][SMIT 78]. More recently, the largest class of checkers necessary to ensure the TSC goal was defined by [NICO 88]. Self-checking circuits now become an important topic in fault-tolerant field [ABRA 90][FUJI 85][JOHN 89][LALA 85].

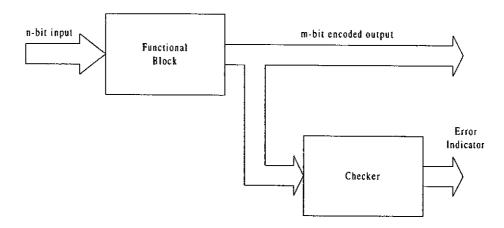

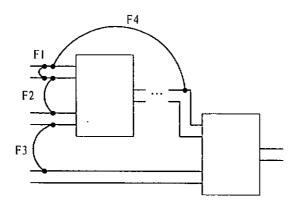

In general, the basic structure of these circuits (as shown in Figure. 3.1) consists of two main blocks: a functional circuit and a checker. The output of the functional circuit, in fault-free operation belonging to a suitable error-detecting code, feeds the checker. The checker should be capable of detecting not only the presence of a non-code word at its inputs, but also faults in itself. In this chapter, the properties of self-checking systems will be introduced.

Figure 3.1 Block diagram of a self-checking system.

### 3.2 SELF-CHECKING CIRCUITS

In this section, we introduce the necessary properties to implement the functional block such that the overall system can achieve the TSC goal. During normal operation, the output of the functional block belongs to a suitable EDC. A non-

codeword at the output of the functional block indicates the presence of a fault. However, a fault may also result in incorrect codeword at the output. So, we need the following definitions to describe the manner in which self-checking circuits deal with faults.

**Definition 3.1.** A circuit is fault secure(FS)[ADER 71][ADER 73] with respect to a given fault set F if it never produces incorrect codeword output for any input for every fault f in F.

A FS circuit will never produce incorrect codeword output when a fault occurs. However, it cannot guarantee that the fault can be indicated by means of non-codeword output. Additional property is required.

**Definition 3.2.** A circuit is self-testing(ST)[CART 68] with respect to a given fault set F if it produces non-codeword output for at least one input for every fault f in F.

**Definition 3.3.** A circuit is totally self-checking(TSC)[ADER 71][ADER 73] if it is both self-testing and fault-secure for every fault f in F.

Existing self-checking circuit designs are based on the following fundamental assumption:

Assumption 3.1. At any time, only one fault can occur and the time interval between the occurrence of two faults is sufficient long such that all the required test vectors can

be applied to the circuit. In other words, TSC circuits are defined respect to single fault assumption.

Apparently, a TSC functional circuit for a given fault set guarantees its correct operation in the presence of faults. Once the fault is activated and the effect is propagated to the output, it must be a non-codeword output. Designing of a circuit with TSC property is always desirable because every fault inside the circuit can be detected by codewords. However, it is hard to achieve TSC respect to some realistic fault models [JHA 84][JHA 90][JHA 93]. So, a more general definition was introduced.

**Definition 3.4.** A circuit is strongly fault secure(SFS)[SMIT 78] for a fault set F if and only if, for every fault f in F, either

- 1) the circuit is TSC when f occurs, or,

- 2) the circuit is still FS but not ST, and the resultant circuit is still SFS for the remaining fault in the fault set.

In other words, undetectable faults are allowed in a SFS circuit. However those faults will not result in incorrect codeword output.

The SFS circuits are the largest class of functional circuits that can achieve the TSC goal. A SFS circuit can be transformed to a TSC circuit if all the redundancy faults are removed. However, application of SFS property is quite complicated. It is necessary to verify that under the occurrence of all combinations of all possible undetectable faults, the circuit is SFS. [WANG 94] stated that it is difficult to achieve TSC goal without significant overhead in terms of hardware cost and extra delay.

#### 3.3 SELF-TESTING CHECKERS

The function of the checker is to determine whether the output of the function block is a codeword or not. Generally, if the output is a codeword, 01 or 10 is generated by the checker output. For non-codewords, the checker will indicate 00 or 11 as error signal. Obviously, the checker generates two outputs that can overwhelm the problem of output line stuck-at fault. Also, two-rail encoded outputs can detect the wired-AND or wired-OR bridging between output lines that otherwise cannot be detected by identical outputs. So, for a checker, we have the following definitions.

**Definition 3.5.** A circuit is code-disjoint(CD)[ADER 71][ADER 73] if it always maps input code space to output code space and input non-code space to output non-code space under normal condition.

**Definition 3.6.** A self-testing checker[ADER 71][ADER 73] is both code-disjoint and self-testing.

In fault tolerant field, "checking the checker" is a universal problem. An ST checker can detect any error at its input, but must also be capable of detecting faults in itself. A TSC functional block monitored by an ST checker can achieve the TSC goal. Let us use the following two examples to demonstrate this point.

**Example 3.1.** If a fault occurs inside the TSC functional block, it will produce a non-codeword for at least one input vector. The checker detects the non-codeword and produces an error signal.

**Example 3.2.** If a fault occurs inside the ST checker, it will be detected by the codeword which is fed by the functional block.

Practically, it is hard to achieve that all faults inside the checker must be detectable. Also, it was thought that under the occurrence of some faults, the checker can still maintain CD property, but not ST. The desired function of a checker is not affected. So a more general property of a checker is defined as follow:

**Definition 3.7.** A checker is strongly code-disjoint(SCD)[NICO 88] for a fault set F if and only if, for every fault f in F, either

- 1) the circuit is ST and CD when f occurs, or

- 2) the circuit is still CD but not ST, and the resultant circuit is still SCD for the remaining fault in the fault set.

In other words, undetectable faults are allowed in an SCD checker. However, the checker is still capable of mapping non-codeword input to non-codeword output.

In both cases, FS property is not necessary for an ST or SCD checker. The ST property ensures that all internal faults will result in non-codeword output and the CD property ensures that all non-codewords at the input will be mapped to non-codewords at the output. [JHA 90] proposed that the output code space may be reduced to either codeword 01 or codeword 10 under the occurrence of the undetectable fault sequences. In a complex self-checking system, a final two-rail checker(TRC) is used to multiplex output signals of the checkers. Based on the observation, the final TRC may not receive sufficient codeword to fully exercise itself. It means that some faults

may not be activated due to insufficient codewords. Therefor, FS property may be useful to the checker. However, [NICO 94] showed that the above observation will not happen for realistic fault models. The reduction in code space is not likely to occur. So, the final TRC can still be fully exercised. On the other hand, in such a complex system, it is necessary to verify that each subsystem can receive all required input tests [BOUD 91].

### 3.4 SUMMARY

In this section, we defined the necessary conditions to achieve the totally self-checking goal. Fault-secure and self-testing are the basic requirements that a TSC functional circuit has to meet. Furthermore, the functional circuit must be monitored by self-testing checker to achieve both self-testing and code-disjoint properties. This system is called totally self-checking system. In practice, under some realistic fault models, the circuit may not achieve totally self-checking property. Strongly fault-secure and strongly code-disjoint properties are defined such that redundancy faults are allowable. An SFS functional block monitored by an SCD checker can achieve the TSC goal.

## Chapter 4

# Analysis of Multiple Stuck-at Fault Coverage in SCCs

### 4.1 INTRODUCTION

In this chapter, we study the multiple stuck-at(s-at) fault coverage in self-checking circuits(SCCs) in general and the self-testing checkers(STCs) in particular. For many years, SCCs are designed based on the single fault assumption as stated in Chapter 3. It is assumed that fault occurs once at a time and before the occurrence of next fault, enough codewords are presented at the input of the SCCs(both the functional block and the checker). From another point of view, SCCs are highly testable circuits because there are no redundancy faults. Self-testing(ST) property ensures that all faults will result in non-codeword for at least one input. Therefore, all single faults in the predefined fault set must be testable.

As the complexity of VLSI circuits increases rapidly, the cost of testing such complicated circuits increases. However, testing must be carried out before shipping the products to customers. Since a large number of physical defects can happen on the VLSI chips, these fabrication defects may be modelled as multiple faults. In the past few decades, test pattern generation algorithms are mostly focused on single s-at fault

model [ABRA 90][FUJI 85][JOHN 89][LALA 85] because the computational complexity of multiple fault detection issue is very high. For a circuit with n lines, it will have at most 2n number of single s-at faults. However, there will be up to 3<sup>n</sup> number of possible multiple s-at faults. Fault driven based test generation method is therefore not possible. On the other hand, random test generation cannot guarantee a high fault coverage and also is computationally costly.

[JACO 92] proposed an algorithm to modify an irredundant two-level multioutput PLA such that a test set for all single s-at faults is capable of detecting any multiple s-at faults. However, his work is limited to PLA applications.

[COX 88] proposed a fault diagnosis algorithm which was based on the A-16 alphabet to keep track of the set of unique line values possible in the presence of any single or multiple faults. However, the work was based on pseudo-random test generation. They do not have a solution to generate a test for multiple fault coverage. On the other hand, the algorithm may be used to show the effectiveness of a test generation method.

Similar work was carried out [KARK 94]. Fault dropping technique was used for fault analysis. Also, the work was based on pseudo-random test generation which have no guarantee that high fault coverage can be obtained.

[MACI 95][TAKA 91] proposed test generation algorithm for multiple fault coverage. However, simulation results showed that there were large variation of fault

coverage between different benchmark circuits. It is believed that there is no single solution that can solve all problems.

[JONE 94][SETH 77] focused on multiple fault coverage problems in parity tree networks. Test generation algorithms were proposed to detect all single and multiple s-at faults.

[NANY 88] studied the multiple s-at fault testability of self-testing checkers. The simulation results showed that the fault coverage decreased as number of multiple faults increased for codeword testing in STCs. The use of non-codewords in off-line production testing to detect multiple s-at faults in the checkers was then proposed. However, in many systems, the checkers are not directly accessible from the primary inputs. Also, the functional blocks are not capable of generating non-codewords during normal operation. It means that additional hardware is required to provide the non-codewords to the checker.

More recently, [REDD 94] proposed a test generation algorithm for two-rail and parity checkers which is based on the output sequence analysis. Comparing this work with [JONE 94][SETH 77], there are many redundancies in the resultant test set. Therefore, the test set is not minimised.

Recall that SCCs are used in highly reliable and safe-critical applications. The TSC, SFS and SCD properties are defined based on single fault assumption. Under the occurrence of multiple faults, these properties would be invalidated. To discover the multiple faults in production stage becomes essential. Therefore, the idea of merging

off-line testing approach for multiple faults with on-line testing capability becomes very attractive. The fundamental benefit of implementing a multiple fault detection algorithm is that it can provide good quality of the system during production test, resulting in higher mean-time-to-failure(MTTF). The effectiveness of on-line testing then becomes higher.

### 4.2 TEST GENERATION IN TWO-RAIL CHECKERS

As discussed in previous section, multiple s-at fault detection algorithm is hard to develop. It is believed that there is no general solution to solve the multiple fault coverage problem. However, some circuit structures are highly testable for multiple faults such as two-level circuits, tree structured circuits, etc. In this research, we have studied the multiple fault detection algorithm of two-rail and parity checkers. Two-rail checkers(TRCs) are the most commonly used STCs. It is commonly used, for example, to multiplex outputs from different checkers to form a final checker. Furthermore, a pair of identical functional blocks and a two-rail checker(TRC) as a comparator can form the most simplest self-checking system. And parity checkers are usually used in bus-based system and memory modules.

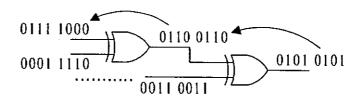

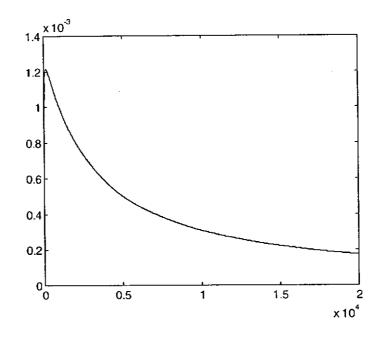

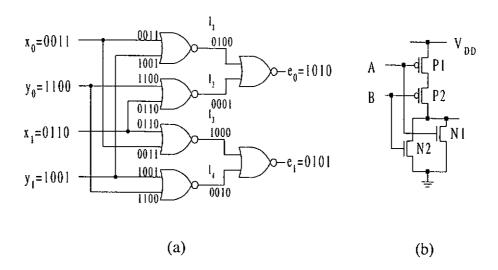

A TRC compares two words that should normally be bit-by-bit complementary. If the two words are complementary, the checker will indicate a fault-free signal (01 or 10) at the two outputs,  $Z_0$  and  $Z_1$ . And if the checker itself is faulty or the two words are not complementary, it will produce an error signal (00 or 11) at the two outputs,  $Z_0$  and  $Z_1$ . Figure 4.1 shows three possible designs of a 2-pair TRC

where  $(X_i, Y_i)$  is an input pair. The circuits implement the following Boolean function:

$$Z_0 = X_0 \bullet Y_1 + Y_0 \bullet X_1$$

$$Z1 = X_0 \bullet X_1 + Y_0 \bullet Y_1$$

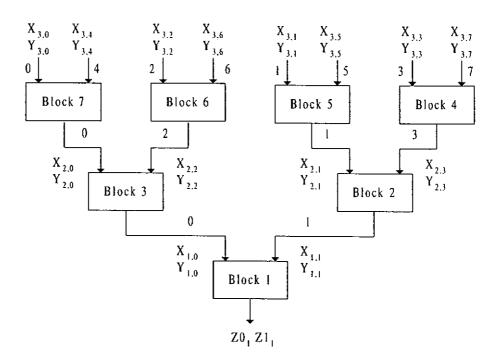

In general, an n-pair TRC can be implemented by cascading 2-pair TRCs as basic building blocks. Figure 4.2 shows two examples of TRC with a simplified TRC block diagram as basic building block. Each block is a 2-pair TRC which can be implemented by any one of the designs as shown in Figure 4.1. Each arrow-line represents a pair of input lines.

Figure 4.1 Three types of 2-pair TRC, (a) AND-

OR, (b) NAND, and (c) NOR gates implementation.

### 4.2.1 Test Generation Algorithm

In our multiple s-at fault analysis, the circuit configuration is based on the circuit diagram as shown in Figure 4.1(a). Fault is detected based on an output sequence analysis approach which is similar to the one proposed in [REDD 94]. If the output sequence is not the same as the fault-free one, faults are detected. To simplify the analysis, we require that the output will toggle between two consecutive input vectors. So, if one of the following conditions are fulfilled, faults will be detected.

- 1) The output is a non-codeword,

- 2) The output is not toggled between two consecutive test vectors.

Figure 4.2 Construction of TRCs using the 2-pair TRC as basic building blocks, (a) complete tree structured 8-pair TRC, and (b) incomplete tree structured 6-pair TRC.

### A. Fault Model

In self-testing checker, it has been found that all single s-at faults can be detected only by codeword inputs in [ADER 73][SMIT 78][NICO 88]. It is shown in [NANY 88] that a minimum 4-codeword test set is enough to detect all single s-at faults in a 2-pair TRC. But the fault coverage will be reduced as multiple faults occur. In this subsection, we shall define the fault model that our analysis is based on.

Consider the 2-pair TRC as shown in Figure 4.1(a). After fault collapsing, 12 unique faults are obtained in a 2-pair TRC. Lines 1 to 8 are modelled as s-at 1 faults and lines 9 to 12 as s-at 0 faults. Now, we can formally define our multiple fault model. Let Fs denote the set of s-at faults so that each block in the TRC will have a set Fs consisting of these 12 faults. The collection of Fs of all blocks in the checker constitutes a complete fault set F. The multiple faults we shall consider are the combination of all faults of all multiplicity in F.

### B. Test Generation Procedure

Now we present the test generation method and show the validity of the method. In this method, the test generation procedure works backward from primary output to primary input, on a block-by-block basis. The test vectors for a block are derived based on the analysis of the output sequence of the block. We introduce our method by the following example.

Refer to Figure 4.2(a). If the outputs  $(Z_0, Z_1)$  of block-1 are ({0101}, {1010}), the inputs of block-1  $(X_m, Y_m, X_n, Y_n)$  derived are ({0011}, {1100}, {0110}, {1001}). Note that {} denotes a sequence of bits. It can easily be seen that all codewords are presented at the inputs of block-1. Based on this observation, a set of rules is derived for the test generation procedure:

- 1) Only one input pair is allowed to change between two consecutive test vectors.

Although any odd number of input pair change will toggle the output, we change only one pair to simplify the test generation.

- 2) All possible codewords must be presented at the inputs of each block. Based on the example above (Figure 4.2(a)), block-2 will not have enough codewords at the inputs. Additional data outputs are therefore required. This is achieved by duplicating the original outputs sequences ({0101}, {1010}) to ({0101 0101}, {1010 1010}). The inputs of block-1 then become ({0011 0011}, {1100 1100}, {0110 0110}, {1001 1001}) as shown in Figure 4.2(a). It is easy to show that the inputs of block-2 are ({0001 1110}, {1110 0001}, {0111 1000}, {1000 0111}). All codewords are presented at the inputs of block-2. Similar procedures can be performed for other blocks.

- 3) The test generation procedure described in Rule 2) is applied iteratively level-bylevel until the primary inputs are reached.

Based on the proposed test generation procedure, a complete test set for the X-terminal inputs(denoted from left-to-right) of the 8-pair TRC of Figure 4.2(a) is shown

in Table 4.1. Note that only the test vectors of the X-terminal inputs are shown. The Y-terminal inputs are only the complements of the corresponding X-terminal inputs. With the test generation procedure demonstrated above, the importance of "ease of use" cannot be over-emphasised.

Table 4.1 Test vectors determined for Figure 4.2(a).

| X-Inputs       | bit sequence        |  |

|----------------|---------------------|--|

| X <sub>7</sub> | 0111 1111 1000 0000 |  |

| X <sub>6</sub> | 0000 0111 1111 1000 |  |

| X <sub>5</sub> | 0001 1111 1110 0000 |  |

| X <sub>4</sub> | 0000 0001 1111 1110 |  |

| X <sub>3</sub> | 0011 1111 1100 0000 |  |

| X <sub>2</sub> | 0000 0011 1111 1100 |  |

| X <sub>1</sub> | 0000 1111 1111 0000 |  |

| X <sub>0</sub> | 0000 0000 1111 1111 |  |

### C. Test Length Comparison

The number of test vectors required by our method is determined by the number of input pairs, k, and the number of levels, d. For a tree structured network with highest level d, if there are no primary inputs attached to blocks with more than 1 level difference, we have

$$d = \lceil \log_2 k \rceil$$

For a single level tree network, the number of input vectors required is 4. With each additional level of blocks, one duplication of output sequence is required. So the test length, L, generated by our method is,

$$L=2^{d+1}$$

Figure 4.3 shows the test length comparison between our method to the one given by [REDD 94].

Figure 4.3 Test length comparison in terms of input pairs.

### 4.2.2 Fault Simulation

Fault simulation was done by C programming. A 16-pair TRC, which contains totally 180 number of unique faults after fault collapsing, was used to verify the test generation method. We determined the multiple fault coverage by exhaustively injecting all combination of the unique faults up to 4 multiplicity and randomly

generating I million multiple faults all any multiplicity in the circuit. Then, the determined test set is applied to the circuit for fault coverage evaluation. Results showed that our test set is sufficient to detect the injected multiple faults and all determined test vectors are necessary in the fault detection process.

### 4.2.3 Validity of the Test Generation Method

Our test generation method is based on the assumption that the output function of TRC will not complement for multiple faults. We prove this by considering the fault effect on each block in a tree structured checker such as the one shown in Figure 4.2(a).

Lemma: There are no multiple faults such that the output responses are the same as fault-free ones or their complements in our test.

*Proof*: To detect multiple faults in a 2-pair TRC, four codewords are enough. We conduct the proof procedure in two steps. In step 1, a detailed multiple fault analysis of the 2-pair TRC is carried out based on the fault diagnosis scheme described in [COX 88] and [KARK 94]. The results of this analysis demonstrate the validity of the four codeword test in the presence of any multiple faults of all multiplicity. In step 2, we extend the multiple fault analysis to the k-pair TRC.

Table 4.2 summarises the results after step 1, where a set of input codewords  $(T_1 = 0101, T_2 = 1001, T_3 = 1010, T_4 = 0110)$  is applied pair-wise consecutively to the 2-pair TRC as shown in Figure 4.1(a). Each row shows all the possible logic values of

0

38

a particular line in the presence of any number of s-at faults in the checker. Any line values that invalidate the expected output line values are marked by a cross-over bar. In this case, the expected output line values are the same as fault-free ones, which are  $Z_0 = \{0101\}$  and  $Z_1 = \{1010\}$ .

Table 4.2 Multiple fault diagnosis of a 2-pair TRC.

| Line           | Test Pair { T <sub>1</sub> , T <sub>2</sub> } | Test Pair { T <sub>2</sub> , T <sub>3</sub> }          | Test Pair { T <sub>3</sub> , T <sub>4</sub> }          |

|----------------|-----------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| label          |                                               |                                                        |                                                        |

| 1              | { 01 / 44 }                                   | { 11 / 11}                                             | { 10 / 11 }                                            |

| 2              | { 11 / 11 }                                   | { 10/ <del>11</del> }                                  | { 00 / 11 }                                            |

| 3              | { 10 / 11 }                                   | { 00 / ++ }                                            | { 01 / 11 }                                            |

| 4              | { 00 / 11 }                                   | { 01 / 11 }                                            | { 11 / 11 }                                            |

| 5              | { 00 / 11 }                                   | { 01 / 11}                                             | { 11 / 11 }                                            |

| 6              | { 01 / 11 }                                   | { 11 / 11 }                                            | { 10 / <del>11</del> }                                 |

| 7              | { 11 / 11 }                                   | { 10 / 11 }                                            | { 00 / 11 }                                            |

| 8              | { 10 / 11 }                                   | { 00 / 11 }                                            | {01/11}                                                |

| 9              | { 01 / <del>00</del> , <del>11</del> }        | { 10 / <del>00</del> , <del>11</del> }                 | { 00 / <del>10</del> , 00, <del>11</del> }             |

| 10             | { 00 / <del>10</del> , 00, <del>11</del> }    | { 00 / 01, 00, 11 }                                    | { 01 / <del>00</del> , <del>11</del> }                 |

| 11             | { 00 / <del>01</del> , 00, <del>11</del> }    | { 01 / <del>00</del> , <del>11</del> }                 | { 10 / <del>00</del> , <del>11</del> }                 |

| 12             | { 10 / <del>00</del> , <del>11</del> }        | { 00 / 10, 00, 11 }                                    | { 00 / 01, 00, 11 }                                    |

| Z <sub>0</sub> | { 01 / 10, 00, 11 }                           | { 10 / <del>01</del> , <del>00</del> , <del>11</del> } | { 01 / <del>10</del> , <del>00</del> , <del>11</del> } |

| $Z_1$          | { 10 / 01, 00, 11 }                           | { 01 / <del>10</del> , <del>00</del> , <del>11</del> } | { 10 / <del>01</del> , <del>00</del> , <del>11</del> } |

- Line labels are referred to Figure 4.1(a)

- Line values are denoted as { fault-free values / all possible faulty values }

From the results obtained, it can be seen that no multiple faults can cause the two outputs of a 2-pair TRC to have the fault-free values.

**Table 4.3** Diagnosis of two-rail checker having the outputs responses equal to the complement of fault-free ones.

| Line  | Test Pair { T <sub>1</sub> , T <sub>2</sub> } | Test Pair { T <sub>2</sub> , T <sub>3</sub> } | Test Pair { T <sub>3</sub> , T <sub>4</sub> }         |

|-------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------|

| label |                                               |                                               |                                                       |

| 1     | { 01 / 11 }                                   | {11/11}                                       | { 10 / 11 }                                           |

| 2     | { 11 / 11 }                                   | { 10 / 11 }                                   | { <del>00</del> / 11 }                                |

| 3     | { 10 / <del>11</del> }                        | { 00 / 11 }                                   | { 01 / 11 }                                           |

| 4     | { <del>00</del> / 11 }                        | { 01 / 44 }                                   | { 11 / 11}                                            |

| 5     | { <del>00</del> / 11 }                        | { 01 / 11 }                                   | { 11 / 11 }                                           |

| 6     | { 01 / ++ }                                   | {11/11}                                       | { 10 / 11 }                                           |

| 7     | { 11 / 11 }                                   | { 10 / 11 }                                   | { 00 / 11 }                                           |

| 8     | { 10 / <del>11</del> }                        | { 00 / 11 }                                   | { 01 / 11 }                                           |

| 9     | { 01 / 00, 11 }                               | { 10 / 00, 11 }                               | { <del>00</del> / 10, <del>00</del> , <del>11</del> } |

| 10    | { 00 / 10, 00, 11 }                           | { 90 / 01, 90, 11 }                           | { 01 / 00, 11 }                                       |

| 11    | { 00 / 01, 00, 11 }                           | { 01 / 00, 11 }                               | { 10 / 00, 11 }                                       |

| 12    | { <del>10</del> / 00, <del>11</del> }         | { 00 / 10, 00, 11 }                           | { 00 / 01, 00, 11 }                                   |

| $Z_0$ | { 01 / 10, 00, 11 }                           | { 10 / 01, 00, 11 }                           | { 01 / 10, 00, 11 }                                   |

| $Z_1$ | { 10 / 01, 00, 11 }                           | { 01 / 10, 00, 11 }                           | { 10 / 01, 00, 11 }                                   |

- Line labels are referred to Figure 4.1(a)

- Line values are denoted as { fault-free values / all possible faulty values }

Next, we consider the multiple fault detection problem in a k-pair tree-structured TRC. Refer to Table 4.3. There is only one input pair that can be changed between two consecutive input test patterns. Consider the high-lighted path from primary inputs to primary outputs in Figure 4.2(a). Suppose that block 2<sup>d</sup>-1 is the first faulty block along the path. After applying a two-pattern test, there are three possible fault effects occurring at the output of this faulty block: 1) one output line carries unidirectional transition(i.e. either {01} or {10}) while the other output line remains unchanged or both lines carry unidirectional transition, 2) both output lines stay unchanged(i.e. {00} or {11}), 3) the outputs are complement to the fault-free ones. For a fault going undetected, there must be other faulty block(s) along the path(e.g. blocks 3 and 1) such that these faulty outputs will be converted to fault-free ones. In the following, we shall prove that for all of the above three fault effects, our test method is capable of detecting the existence of multiple faults.

- 1) One output line carries unidirectional transition while the other output line remains unchanged or both lines carry unidirectional transition. It can be shown that there are no faults such that a faulty 2-pair TRC can produce fault-free outputs. The reason for this is that a 2-pair TRC is an unate function which is not capable to generate any EXOR operation when it is faulty. Similarly, no fault-free outputs can occur when both lines carry unidirectional transition.

- 2) Both output lines stay unchanged. The outputs of the faulty 2-pair TRC under multiple faults may appear as codewords. However, the output would not be toggled in the two-pattern test. This fault effect will propagate to the primary outputs and be eventually detected.

3) The outputs are complement to the fault-free ones. In Table 4.2, it has already been proved that no multiple faults can result in fault-free outputs. Therefore here we only need to show that no multiple faults can occur such that the outputs are the complements of the fault-free ones. We show this by referring to Table 4.3, which is generated based on the assumption that the outputs are complement of the fault-free ones. Consider as an example test (T<sub>1</sub>, T<sub>2</sub>). In order to produce ({10}, {01}) at the outputs, line 9 must be {00} which is not generated by the AND gate. So line 9 can be assumed to be s-at 0. But in test (T<sub>3</sub>, T<sub>4</sub>), line 9 must carry values {10} such that outputs can be complement to the fault-free ones. So there is a contradiction between tests (T<sub>1</sub>, T<sub>2</sub>) and (T<sub>3</sub>, T<sub>4</sub>). Therefore, it is impossible for a faulty TRC block to generate any faulty outputs which are complemented to the fault-free ones for our test.

Through such detailed analysis, it can be proved that there are no faults such that the outputs are equal to the fault-free ones, or their complements. On the other hand, the erroneous outputs(under the occurrence of either fault effect 1 or fault effect 2) generated by a faulty block along the path can propagate to the primary output lines. All multiple faults can thus be detected by our test.

### 4.2.4 Implementation of the Test Generation Method

In order to make use of the test generation method more effectively, a two-step method to implement the test generation algorithm was proposed In the first step, every pair of input lines of a TRC is labelled by an unique number according to a every line through the test can be easily determined. If the line is primary input, test set is derived. In the second step, a novel analytic scheme is used to analyse the test set, to enable the user to simplify the implementation of the test generation procedure.

### A. Input Pair Number Assignment Method