# **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

### IMPORTANT

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="https://www.lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

Pao Yue-kong Library, The Hong Kong Polytechnic University, Hung Hom, Kowloon, Hong Kong

http://www.lib.polyu.edu.hk

# OPTIMIZING BIG DATA SYSTEMS WITH NON-VOLATILE MEMORIES: FROM GRAPH COMPUTING TO FLASH-BASED SSD ARRAYS

HAN LEI

PhD

The Hong Kong Polytechnic University

2019

# THE HONG KONG POLYTECHNIC UNIVERSITY DEPARTMENT OF COMPUTING

# Optimizing Big Data Systems with Non-volatile Memories: From Graph Computing to Flash-based SSD Arrays

Han Lei

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

February 2019

# CERTIFICATE OF ORIGINALITY

I hereby declare that this thesis is my own work and that, to the best of my knowledge and belief, it reproduces no material previously published or written, nor material that has been accepted for the award of any other degree or diploma, except where due acknowledgement has been made in the text.

\_\_\_\_\_(Signature)

Han Lei (Name of Student)

#### ABSTRACT

Big data has been exerting an increasingly pervasive and profound influence on everyday life. For example, social networks, such as Facebook and Twitter, produce huge volumes of data and analyze big data to learn relationships between users, which are usually linked as largescale graphs. However, as a huge collection of data over a time frame for processing and managing, big data remains extraordinarily complex and large for current computing infrastructures, leading to high processing costs and high storage resource consumption. Graph processing is an important part of big data analysis. Processing large-scale graphs on traditional platforms including CPU, GPU and FPGA is inefficient due to the many random memory access. Moreover, high-variety information with various data characteristics has significantly boosted. Persistently storing them on SSD-based arrays for high-velocity incurs high disk replacement rates due to the limited lifetime of SSDs. In addition, employing erasure codes for data protection in storage systems consumes high computational resources, further exacerbating the inefficiency of big data processing. In this thesis, we optimize big data systems with non-volatile memories from several aspects, including improving the performance of large-scale graph processing, extending the lifetime of SSD arrays and flash chips, and improving the efficiency of erasure coding on SSD arrays.

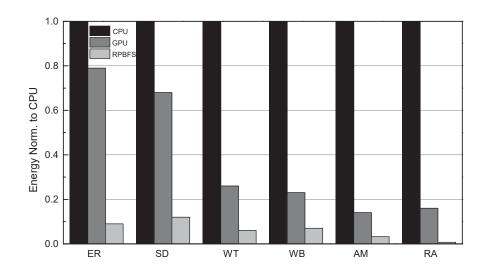

In the first part, we focus on optimizing the computational performance of big data with an emerging metal-oxide resistive random access memory (ReRAM). In the case of large-scale graph traversal, processing breadth-first search (BFS) on traditional platforms issues many random and irregular memory accesses, especially on CPU-based and GPUbased platforms. This leads to a huge amount of data movement between memories and processors, so that processors are always waiting for memories and executing instructions slowly. Moreover, the off-chip main memory in traditional platforms is a major consumer of energy. To weaken these limitations, we propose a novel ReRAM-based processing-inmemory architecture for BFS, called RPBFS. In RPBFS, the ReRAM-based memory banks are separated into graph banks and master banks. We design an efficient graph mapping scheme to distributively store a graph on multiple graph banks. To reduce data movement overhead, we design an efficient traversal scheme that can constrain a graph search inside the related graph banks through collaboration with a master bank. Moreover, we propose an analytical performance model for RPBFS, which can help us identify bottlenecks and provide optimization opportunities for our design. The experimental results show that the proposed schemes can significantly improve graph traversal performance and achieve high energy reductions compared with both CPU-based and GPU-based BFS implementations.

In the second part, we optimize the storage efficiency for big data systems with NAND-based flash memory and ReRAM, achieving lower operational cost. Flash-based SSD arrays are increasingly being deployed in data centers. Compared with hard disk drive arrays, SSD arrays drastically enhance storage density and I/O performance, and reduce power and rack space. However, SSDs suffer aging issues since a flash block can only be experienced by a limited number of program/erase (P/E) cycles. The ability of storage systems to maintain service in the time aspect is particularly relevant to operational cost, frequently replacing failed drives makes service unstable. To optimize this, first, we propose FreeRAID which applies approximate storage via the interplay of RAID and SSD controllers to improve the lifetime of SSD-based RAID arrays. Our basic idea is to reuse faulty blocks (which contain pages with uncorrectable errors) to store approximate data (which can tolerate more errors). FreeRAID integrates two key techniques: dual-space management, which can efficiently allocate independent space for normal and approximate data, and adaptive-FTL, which can dynamically switch FTL schemes for an SSD according to its lifespan stage. We conduct experiments and compare our FreeRAID with conventional RAID and FTL schemes. The experimental results show that we can significantly increase the lifetime of SSD-based RAID arrays. Second, we extend the lifetime optimization to embedded storage systems. We propose Rebirth-FTL, a pure software management in the flash translation layer for the lifetime optimization. Rebirth-FTL efficiently and effectively manages two spaces, approximate space and normal space, with approximation-aware address mapping, coordinated garbage collection and differential wear leveling. We also develop a scheme to pass approximate information from userland to kernel space in Linux, which can collaborate with Rebirth-FTL to optimize the lifetime of flash memory. A lifetime model is also presented for lifetime analysis. We implement Rebirth-FTL on an embedded development board and a simulator. Evaluations across a wide variety of workloads show that Rebirth-FTL significantly outperforms conventional FTLs in lifetime extensions and satisfies the workloads quality. Third, erasure codes such as Cauchy Reed-Solomon codes have been gaining ever-increasing importance for fault-tolerance in SSD-based RAID arrays. However, erasure coding on processor-based implementations such as a dedicated RAID controller relies on Galois Field arithmetic to perform matrix-vector multiplication, increasing computational complexity and leading to a huge number of memory accesses. We propose Re-RAID which uses ReRAM as the main memory in both RAID and SSD controllers. In Re-RAID, erasure coding can be processed in ReRAM memory to achieve high throughput. To minimize the overhead for recovering a single failure, we propose a confluent Cauchy-Vandermonde matrix as the generator matrix, which allows ReRAM memory on SSDs to perform the reconstruction task for a single failure. Experimental results show that our Re-RAID has a significant performance improvement in encoding and decoding compared with conventional processor-based implementation.

**Keywords:** Big data storage system, ReRAM, NAND flash memory, SSD, graph traversal, RAID, FTL, erasure codes, lifetime

#### PUBLICATIONS

- Lei Han, Zhaoyan Shen, Duo Liu, Zili Shao, H. Howie Huang, Tao Li, "A Novel ReRAM-based Processing-in-Memory Architecture for Graph Traversal", in ACM Transactions on Storage (TOS), 2018.

- Lei Han, Bin Xiao, Xuwei Dong, Zhaoyan Shen, and Zili Shao, "DS-Cache: A Refined Directory Entry Lookup Cache with Prefix-Awareness for Mobile Devices", accepted in 2019 Design, Automation & Test in Europe Conference & Exhibition (DATE '19), Florence, Italy, March 25-29, 2019.

- Fang Wang, Zhaoyan Shen, Lei Han, and Zili Shao, "ReRAM-based Processing-in-Memory Architecture for Blockchain Platforms," in *Proceedings of the 24th Asia and South Pacific Design Automation Conference* (ASP-DAC '19), Tokyo, Japan, Jan.21-24, 2019.

- Lei Han, Zhaoyan Shen, Zili Shao, and Tao Li, "Optimizing RAID/SSD Controllers with Lifetime Extension for Flash-based SSD Array", in ACM SIGPLAN/SIGBED Conference on Languages, Compilers, and Tools for Embedded Systems (LCTES '18), Philadelphia, Pennsylvania, United States, June 18-22, 2018.

- Lei Han, Zhaoyan Shen, Zili Shao, H. Howie Huang, and Tao Li, "A novel ReRAMbased processing-in-memory architecture for graph computing," in 2017 IEEE 6th Non-Volatile Memory Systems and Applications Symposium (NVMSA '17), Hsinchu, Taiwan, Aug.16-18, 2017.

#### ACKNOWLEDGEMENTS

First and foremost, I feel so grateful to have Prof. Zili Shao and Prof. Bin Xiao as my supervisors in the Hong Kong Polytechnic University (Polyu). I have learned a lot from their insightful guidance, meticulous attitude and professional supervision. It is my great pleasure to be a student of Prof. Shao, he has been giving me many elaborate suggestions and guidance even though he is now with the Chinese University of Hong Kong. Especially such a sentence "be a valuable member to society" has been affected me. I want to thank him for supporting me over the years. I also want to thank Prof. Bin Xiao for his encouragement and advice. Actually, without those fruitful discussions, I can hardly achieve the research outcomes which constitute the main content of this thesis.

I must acknowledge Prof. Howie Huang at the George Washington University and Prof. Tao Li at the University of Florida. I learned a lot from the discussions and interactions with them in academic research. Their truly scientist intuitions and genial personalities enrich my intellectual maturity. Besides, I want to thank Prof. Yi Lin at the Northwestern Polytechnical University, for his guidance and encouragement. I also express my gratitude to Prof. Shuai Li from the Polyu for his comments and suggestions on my research.

I would like to thank my research group in Polyu, including Dr. Yi Wang, Dr. Duo Liu, Dr. Renhai Chen, Dr. Zhaoyan Shen, Chenlin Ma, Yuanjing Shi, Fang Wang, Dr. Shang Gao, Dr. Zhe Peng, Zecheng Li, Songlin Hou and Lihao Liu. Thanks for their considerate assistance on my research and daily life during my Ph.D. study. Another particular thanks goes to my friends in Polyu, including Lei Xue, Zhijian He, Xingye Lu, Qiang Li, Yu Lei, Quanyu Dai, Hui Li, Liang Zhang, Xinbo Yu, Runjie Tan, Wengen Li, Ruosong Yang, Ningning Hou, Qiang Zhang, Edison Chan, Sitong Mao, Yumeng Guo, Jin Xiao, Wangmeng Xiang, Chuang Hu, Yinyan Zhang, Zhonghuang Yang, Jiaxing Shen, Jianrui Cai, Wenjian Xu, Bo Tang, Shuhang Gu, Bo Lu, Tian Lan, Yin Xiao, Jacob, Daniel, Shamsa, Prof. Cecilia W.P. Li-Tsang and many others. The discussions and exchanges with them made my Ph.D. study a nice journey.

I want to thank Prof. Man Lung Yiu from Hong Kong Polytechnic University for kindly being the Chairman of the Board of Examiners (BoE). I also thank Prof. Tei-wei Kuo from National Taiwan University, and Prof. Xiaowen Chu from Hong Kong Baptist University, for kindly taking time out from their busy schedule to serve as my external examiners.

I recognize that this thesis would not have been possible without the financial assistance from the Polyu. I appreciate Prof. Shao and Prof. Xiao, and the Department of Computing for offering me the travel grants to attend several international conferences. I also acknowledge the student halls of residence of Polyu for providing me a cosy living space for my stay.

Finally, my special thanks goes to my family, including my parents, my grandmother and also in memory of my grandfather. Thanks for their endless love, support, and encouragement through my entire life. They are always on my side, and they always let me pursue my dream for so long and so far away from home. Also, I am really grateful for my girlfriend's endless love, patience, and understanding.

## TABLE OF CONTENTS

| CEF | RTIFIC | ATE OF ORIGINALITY                                                                | ii   |

|-----|--------|-----------------------------------------------------------------------------------|------|

| ABS | STRAC  | Т                                                                                 | iii  |

| PUE | BLICA  | TIONS                                                                             | vi   |

| ACH | KNOW   | LEDGEMENTS                                                                        | vii  |

| LIS | ГOFF   | IGURES                                                                            | xiii |

| LIS | ГOFТ   | ABLES                                                                             | XV   |

| CHA | APTER  | 1. INTRODUCTION                                                                   | 1    |

| 1.1 | Relate | ed Work                                                                           | 4    |

|     | 1.1.1  | Processing-in-memory Accelerator                                                  | 5    |

|     | 1.1.2  | Approximate Storage                                                               |      |

|     | 1.1.3  | Software-managed RAID Arrays and Flash                                            | 7    |

| 1.2 |        | nified Research Framework                                                         |      |

| 1.3 | Contri | butions                                                                           | 10   |

| 1.4 |        | Organization                                                                      |      |

| CHA | APTER  | 2. A NOVEL RERAM-BASED PROCESSING-IN-MEMORY ARCHI-<br>TECTURE FOR GRAPH TRAVERSAL | 13   |

| 2.1 | Introd | uction                                                                            |      |

|     |        | round and Motivation                                                              |      |

|     | C      | Graph Representation                                                              |      |

|     |        | Breadth-first Search                                                              | 18   |

|     | 2.2.3  | ReRAM Basics                                                                      | 19   |

|     | 2.2.4  | Motivation Example                                                                | 19   |

| 2.3 | ReRA   | M-based PIM Architecture for Graph Traversal                                      | 21   |

|     | 2.3.1  | Microarchitecture                                                                 | 22   |

|     | 2.3.2  | Mapping Graph to A ReRAM Crossbar                                                 | 22   |

|     | 2.3.3  | Graph Layout in Multiple Crossbar Arrays                                          |      |

| 2.4                                                       | Bread                                                                                                                        | th-first Search on ReRAM-based Main Memory                                                                                                                                                                           | 26                                                                                                         |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                                           | 2.4.1                                                                                                                        | Graph Mapping                                                                                                                                                                                                        | 26                                                                                                         |

|                                                           | 2.4.2                                                                                                                        | Graph Initialization                                                                                                                                                                                                 | 26                                                                                                         |

|                                                           | 2.4.3                                                                                                                        | Graph Traversal                                                                                                                                                                                                      | 27                                                                                                         |

|                                                           | 2.4.4                                                                                                                        | Extra Vertex Cache                                                                                                                                                                                                   | 30                                                                                                         |

|                                                           | 2.4.5                                                                                                                        | Software-hardware Interface                                                                                                                                                                                          | 30                                                                                                         |

|                                                           | 2.4.6                                                                                                                        | Limitations                                                                                                                                                                                                          | 31                                                                                                         |

| 2.5                                                       | Perfor                                                                                                                       | mance Analysis                                                                                                                                                                                                       | 32                                                                                                         |

|                                                           | 2.5.1                                                                                                                        | Performance Model                                                                                                                                                                                                    | 32                                                                                                         |

|                                                           | 2.5.2                                                                                                                        | Performance Analysis                                                                                                                                                                                                 | 36                                                                                                         |

| 2.6                                                       | Exper                                                                                                                        | imental Evaluation                                                                                                                                                                                                   | 37                                                                                                         |

|                                                           | 2.6.1                                                                                                                        | Methodology                                                                                                                                                                                                          | 37                                                                                                         |

|                                                           | 2.6.2                                                                                                                        | Evaluation Results                                                                                                                                                                                                   | 39                                                                                                         |

| 2.7                                                       | Other                                                                                                                        | Related Work                                                                                                                                                                                                         | 46                                                                                                         |

| 2.8                                                       | Summ                                                                                                                         | ary                                                                                                                                                                                                                  | 47                                                                                                         |

| CII                                                       | APTER                                                                                                                        | 2 OPTIMIZING DAID/COD CONTROLLEDS WITH LIEFTIME EX                                                                                                                                                                   |                                                                                                            |

| ιн                                                        |                                                                                                                              | - 3 - OPTIVIZING RAID/SSD CONTROLLERS WITH LIFETIVE EX-                                                                                                                                                              |                                                                                                            |

| CHA                                                       | APIEK                                                                                                                        | 3. OPTIMIZING RAID/SSD CONTROLLERS WITH LIFETIME EX-<br>TENSION FOR FLASH-BASED SSD ARRAYS                                                                                                                           |                                                                                                            |

| 3.1                                                       |                                                                                                                              |                                                                                                                                                                                                                      | 48                                                                                                         |

|                                                           | Introd                                                                                                                       | TENSION FOR FLASH-BASED SSD ARRAYS                                                                                                                                                                                   | 48<br>48                                                                                                   |

| 3.1                                                       | Introd                                                                                                                       | TENSION FOR FLASH-BASED SSD ARRAYS                                                                                                                                                                                   | 48<br>48<br>51                                                                                             |

| 3.1                                                       | Introd<br>Backg<br>3.2.1                                                                                                     | TENSION FOR FLASH-BASED SSD ARRAYS                                                                                                                                                                                   | 48<br>48<br>51<br>51                                                                                       |

| 3.1                                                       | Introd<br>Backg<br>3.2.1                                                                                                     | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays                                                                                                                                       | 48<br>48<br>51<br>51<br>52                                                                                 |

| 3.1                                                       | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3                                                                                   | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes                                                                                                    | <ul> <li>48</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> </ul>                         |

| 3.1<br>3.2                                                | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3                                                                                   | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes<br>Approximate Storage                                                                             | <ul> <li>48</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> <li>53</li> </ul>             |

| 3.1<br>3.2                                                | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1                                                                 | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes<br>Approximate Storage<br>AID                                                                      | <ul> <li>48</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>54</li> </ul> |

| 3.1<br>3.2                                                | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2                                                        | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes<br>Approximate Storage<br>AID<br>Overview                                                          | 48<br>48<br>51<br>51<br>52<br>53<br>53<br>53<br>54<br>55                                                   |

| 3.1<br>3.2                                                | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3                                               | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes<br>Approximate Storage<br>AID<br>Overview<br>New Type: Exploitable Blocks                          | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56                                                         |

| 3.1<br>3.2                                                | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                                      | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction<br>round<br>SSD-Based RAID Arrays<br>Existing Optimized RAID Schemes<br>Approximate Storage<br>AID<br>Overview<br>New Type: Exploitable Blocks<br>Dual-Space Management | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56<br>60                                                   |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>             | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Evalua                            | TENSION FOR FLASH-BASED SSD ARRAYS                                                                                                                                                                                   | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56<br>60                                                   |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>             | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Evalua<br>3.4.1                   | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction                                                                                                                                                                         | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56<br>60<br>65<br>65                                       |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>             | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Evalua<br>3.4.1<br>3.4.2          | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction                                                                                                                                                                         | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56<br>60<br>65<br>65<br>66                                 |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Introd<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>FreeR<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Evalua<br>3.4.1<br>3.4.2<br>Other | TENSION FOR FLASH-BASED SSD ARRAYS<br>uction                                                                                                                                                                         | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>55<br>56<br>60<br>65<br>65<br>66<br>71                           |

| CH  | APTER   | 4. REBIRTH-FTL: LIFETIME OPTIMIZATION VIA APPROXIMATE STORAGE FOR NAND FLASH           | 73  |

|-----|---------|----------------------------------------------------------------------------------------|-----|

| 4.1 | Introdu | action                                                                                 | 73  |

| 4.2 |         | round                                                                                  |     |

|     | -       | NAND Flash Memory                                                                      |     |

|     |         | Flash Translation Layer                                                                |     |

|     |         | Approximate Storage                                                                    |     |

| 4.3 |         | h-FTL                                                                                  |     |

|     |         | Overview                                                                               |     |

|     | 4.3.2   | Approximation-aware Address Mapping                                                    | 79  |

|     | 4.3.3   | Coordinated Garbage Collection                                                         | 81  |

|     | 4.3.4   | Differential Wear Leveling                                                             | 83  |

| 4.4 | Data A  | Attributes Cut-through                                                                 | 83  |

| 4.5 | Lifetin | ne Model                                                                               | 85  |

| 4.6 | Experi  | mental Evaluation                                                                      | 88  |

|     | 4.6.1   | Experiment Setup                                                                       | 88  |

|     | 4.6.2   | Evaluation Results                                                                     | 89  |

| 4.7 | Summ    | ary                                                                                    | 93  |

| CH  | APTER   | 5. OPTIMIZING CAUCHY REED-SOLOMON CODING VIA RERAM CROSSBARS IN SSD-BASED RAID SYSTEMS |     |

| 5.1 | Introdu | action                                                                                 | 95  |

| 5.2 | Backg   | round and Motivation                                                                   | 98  |

|     | 5.2.1   | SSD-based RAID System                                                                  | 98  |

|     | 5.2.2   | Erasure Coding Process                                                                 | 98  |

|     | 5.2.3   | Cauchy Reed-Solomon Codes                                                              | 99  |

|     | 5.2.4   | ReRAM Basics                                                                           | 100 |

|     | 5.2.5   | Motivation Example                                                                     | 101 |

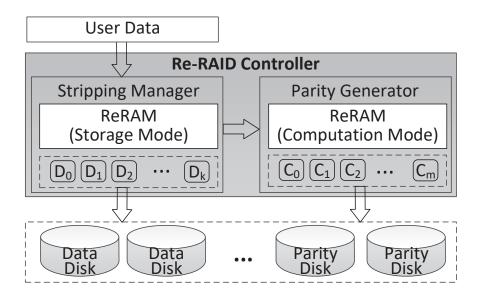

| 5.3 | Re-RA   | ID: A New SSD-based RAID System with ReRAM-accelerated CRS Coding                      | 102 |

|     | 5.3.1   | Overview                                                                               | 102 |

|     | 5.3.2   | Cauchy Reed-Solomon Coding on Re-RAID                                                  | 103 |

|     | 5.3.3   | Reconstruction on Re-RAID                                                              | 105 |

|     | 5.3.4   | Limitations                                                                            | 107 |

| 5.4 | Experi  | mental Evaluation                                                                      | 108 |

|     | 5.4.1   | Experiment Setup                                                                       | 108 |

|     | 5.4.2 Evaluation Results            | 109 |

|-----|-------------------------------------|-----|

| 5.5 | Other Related Work                  | 112 |

| 5.6 | Summary                             | 113 |

|     |                                     |     |

| CHA | APTER 6. CONCLUSION AND FUTURE WORK | 114 |

| 6.1 | Conclusion                          | 114 |

| 6.2 | Future Work                         | 116 |

|     |                                     |     |

| REF | ERENCES                             | 117 |

## LIST OF FIGURES

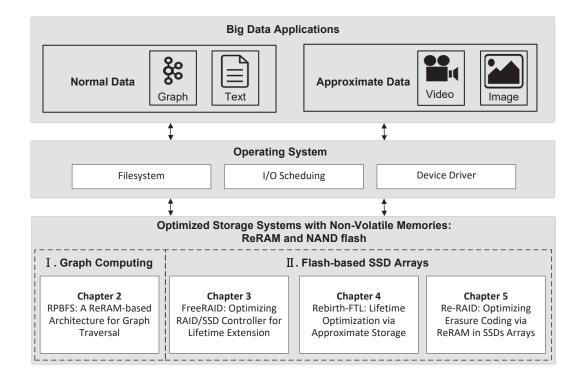

| 1.1  | Unified Research Framework                                                           | 9  |

|------|--------------------------------------------------------------------------------------|----|

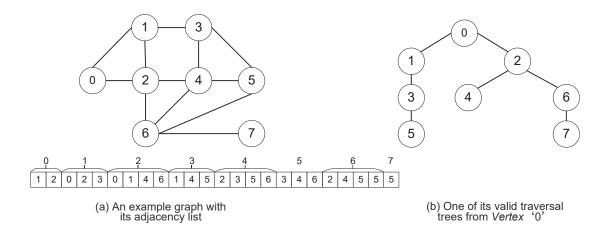

| 2.1  | An example graph $G$ and one of its valid traversal trees                            | 17 |

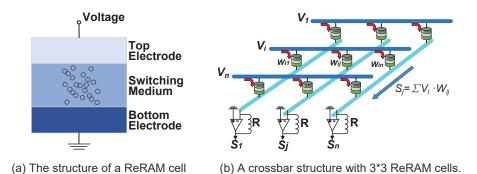

| 2.2  | ReRAM basics                                                                         | 19 |

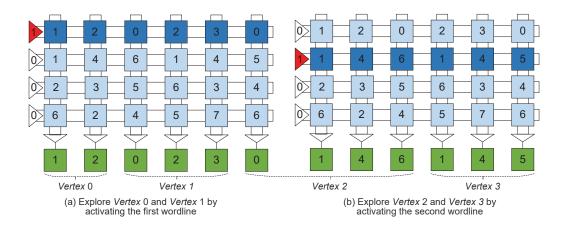

| 2.3  | Activating one wordline can lead to the traversal of multiple vertices               | 20 |

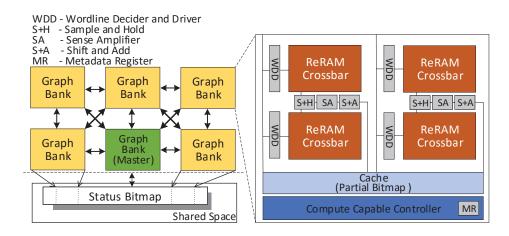

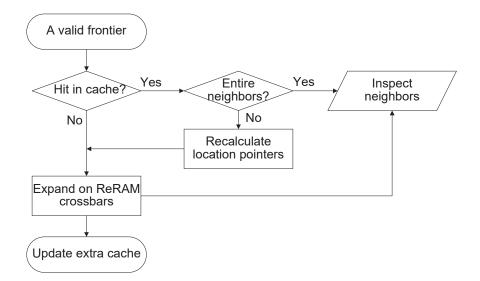

| 2.4  | RPBFS architecture.                                                                  | 21 |

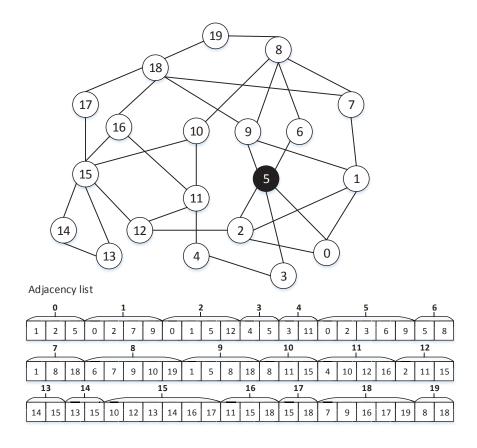

| 2.5  | An example graph <i>H</i> with its adjacency list                                    | 23 |

| 2.6  | The layout of graph $H$ involved with multiple banks                                 | 24 |

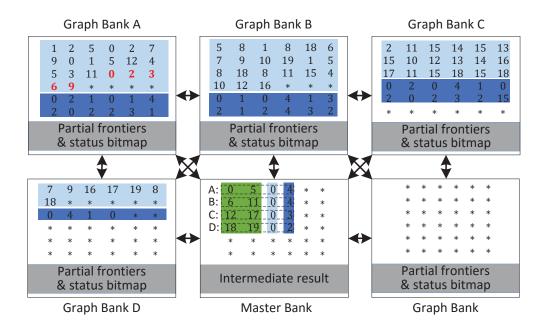

| 2.7  | The workflow of the extra vertex cache                                               | 30 |

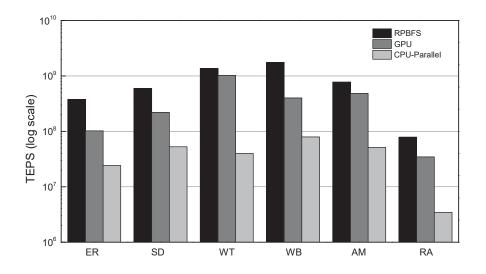

| 2.8  | Performance of RPBFS and direction-optimizing GPU-based and CPU-based solu-<br>tions | 40 |

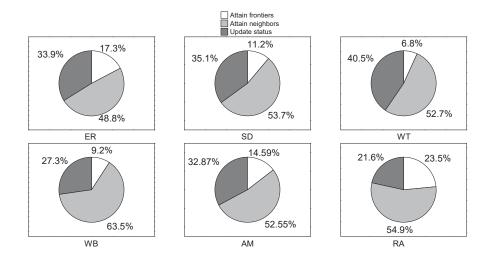

| 2.9  | The breakdown of the execution time of BFS in RPBFS architecture                     | 41 |

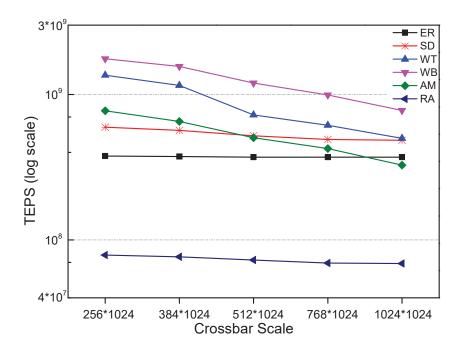

| 2.10 | Performance with the scalability of RPBFS.                                           | 42 |

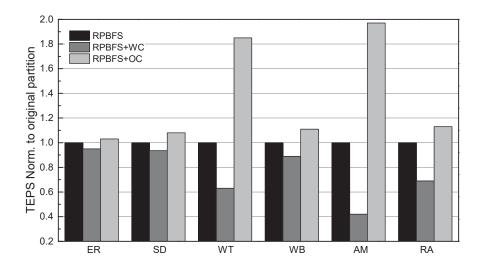

| 2.11 | Performance improvement with different graph partitioning schemes                    | 44 |

| 2.12 | Energy saving results (vs. CPU and GPU).                                             | 45 |

| 2.13 | Area breakdown of RPBFS.                                                             | 45 |

| 3.1  | Higher error tolerance can extend the endurance of a NAND flash block                | 49 |

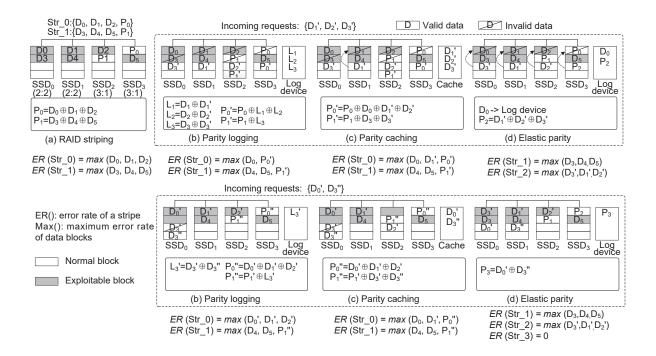

| 3.2  | Three optimized RAID schemes                                                         | 52 |

| 3.3  | Overview of FreeRAID.                                                                | 54 |

| 3.4  | The transitions of blocks in a lifecycle and their error rate                        | 55 |

| 3.5  | The transitions of blocks in a lifecycle and their error rate                        | 56 |

| 3.6  | An example of data allocation and error isolation.                                   | 58 |

| 3.7  | Combination with existing RAID schemes                                               | 59 |

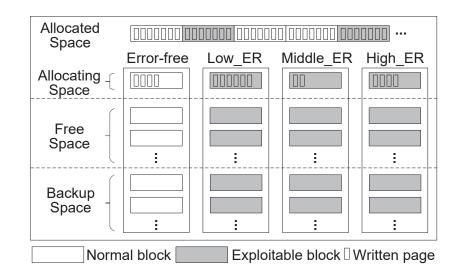

| 3.8  | Block Allocation in FreeRAID.                                                        | 61 |

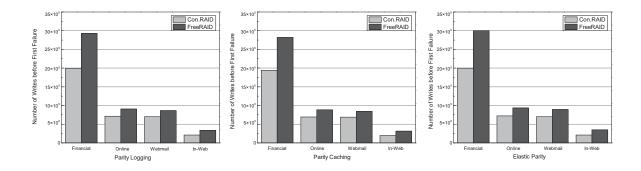

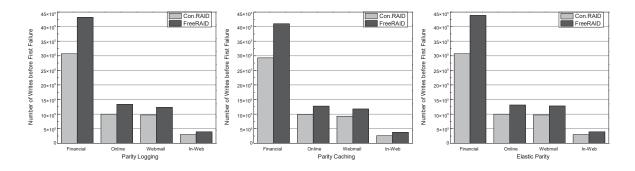

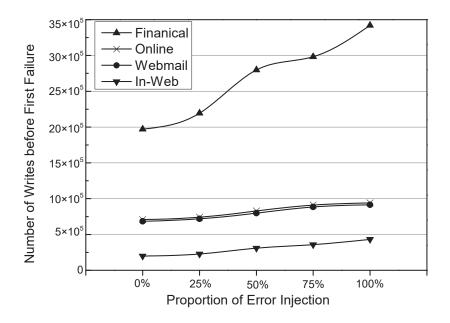

| 3.9  | Total writes of FreeRAID and a conventional RAID with SSDs in balanced ages          | 67 |

| 3.10 | Total writes of FreeRAID and a conventional RAID with SSDs in differential ages      | 67 |

| 3.11 | Lifetime extensions under different ratios of error-relaxation workloads             | 68 |

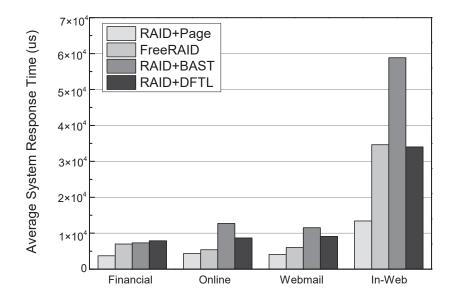

| 3.12 | Comparisons of average system response time                                          | 69 |

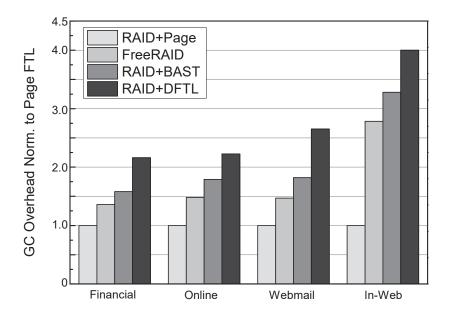

| 3.13 | Comparisons of GC overhead.                                                          | 70 |

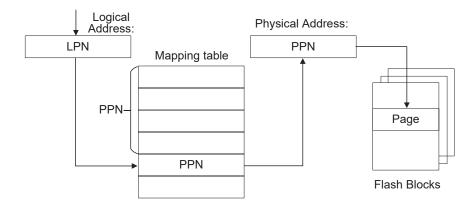

| 4.1  | A typical page-level FTL scheme                                                      | 77 |

| 4.2  | NAND flash system architecture with Rebirth-FTL.                                                                                                                 | 79 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | Block management in Rebirth-FTL.                                                                                                                                 | 80 |

| 4.4  | Error-separated address mapping in Rebirth-FTL.                                                                                                                  | 81 |

| 4.5  | Data attributes cut-through in the Linux I/O stack                                                                                                               | 84 |

| 4.6  | The average write request response time from Rebirth FTL and PFTL                                                                                                | 90 |

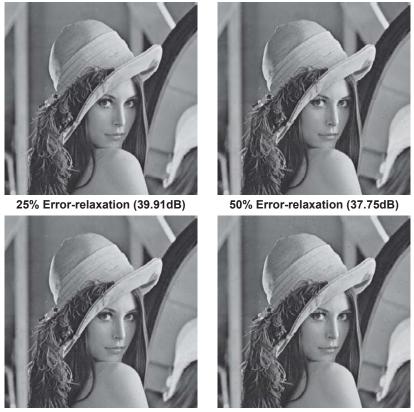

| 4.7  | Quality loss in PSNR with different percentage of error-relaxation requests                                                                                      | 91 |

| 4.8  | One example of bad frames in the video                                                                                                                           | 92 |

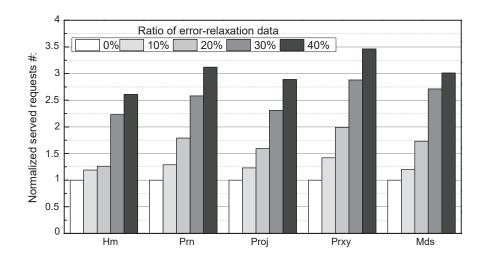

| 4.9  | Normalized served requests #: comparing baseline and Rebirth-FTL                                                                                                 | 93 |

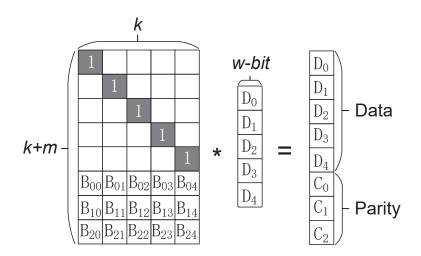

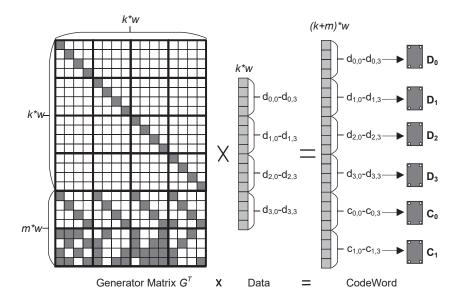

| 5.1  | Encoding process with a generator matrix $G^T$                                                                                                                   | 99 |

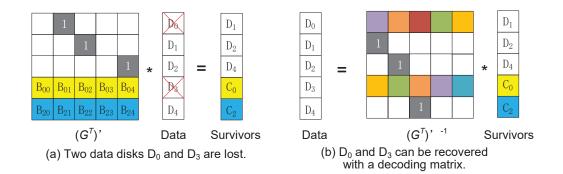

| 5.2  | Decoding process with survivors and an inverse matrix.                                                                                                           | 99 |

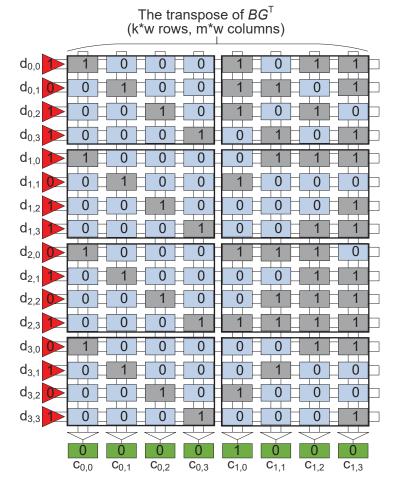

| 5.3  | The matrix-vector representation of a Cauchy Reed-Solomon code with $k = 4, m = 2, w = 4$ . Each element is one bit                                              | 00 |

| 5.4  | Example of performing Cauchy Reed Solomon coding on a ReRAM crossbar 10                                                                                          | 01 |

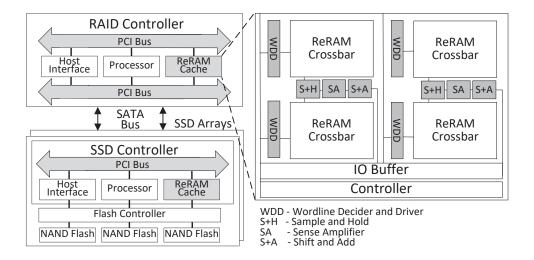

| 5.5  | Overview of Re-RAID and microarchitecture of a ReRAM memory bank 10                                                                                              | 03 |

| 5.6  | Data flow with CRS encoding on Re-RAID                                                                                                                           | 04 |

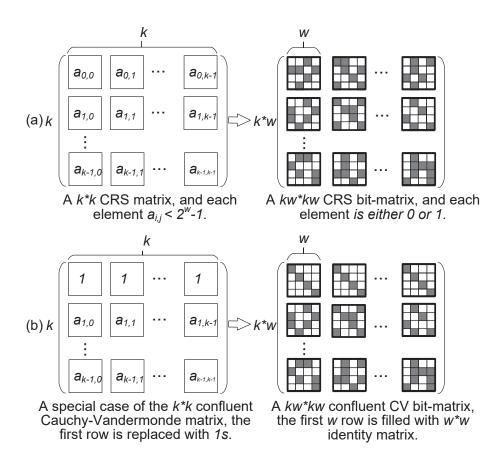

| 5.7  | (a). Traditional Cauchy matrix and its bit-matrix with a given k and w. If $k \le 2^{w-1}$ , the matrix will be invertible. (b). An optimized code in our design | 05 |

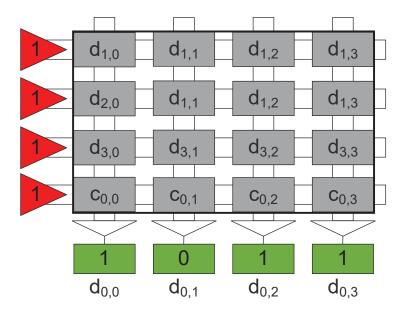

| 5.8  | Recovering a single failure in the ReRAM crossbars on SSDs                                                                                                       | 06 |

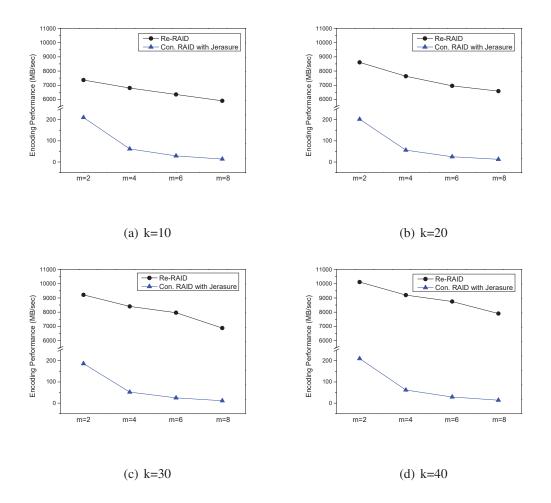

| 5.9  | Comparison of encoding performance                                                                                                                               | 10 |

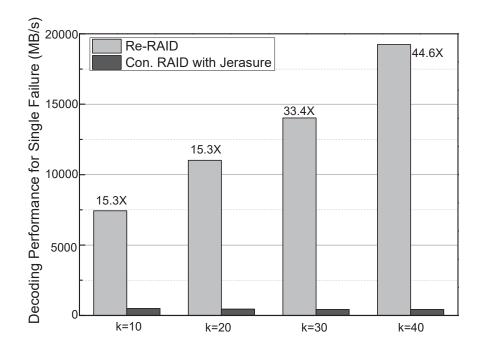

| 5.10 | Comparison of decoding performance for a single failure                                                                                                          | 11 |

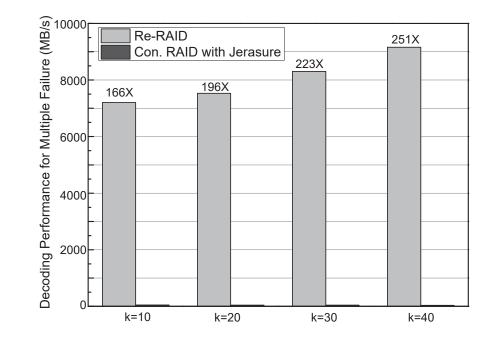

| 5.11 | Comparison of decoding performance for multiple failures 1                                                                                                       | 12 |

## LIST OF TABLES

| 2.1 | Software-hardware interface of RPBFS                                 | 31  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | Analysis terminology                                                 | 33  |

| 2.3 | Latency terminology                                                  | 34  |

| 2.4 | The configurations of RPBFS architecture and hardware                | 38  |

| 2.5 | Graph specification                                                  | 39  |

| 2.6 | Performance improvement by employing extra vertex cache              | 41  |

| 3.1 | Workload characteristics                                             | 66  |

| 4.1 | Analysis terminology                                                 | 86  |

| 4.2 | Workload characteristics                                             | 89  |

| 4.3 | Quality Loss of an example of bad frames in PSNR                     | 92  |

| 5.1 | The Configurations of ReRAM-based RAID controller and SSD controller | 108 |

# CHAPTER 1 INTRODUCTION

The uses of big data have become ubiquitous in many areas of our daily life. For example, there were 500 millions Tweets sent [6] and 300 millions photos uploaded to Facebook [32] for storage each day in 2018. Although big data is increasingly becoming more understandable to computers with sustainable technologies, it is still extraordinarily complex and large for current computing infrastructures, leading to high data processing costs and high storage resource consumption. In the case of large-scale graph processing, simply increasing the number of processor cores is ineffective in improving performance [1]. Moreover, high-volume and high-variety information has increased significantly, requiring terabyte-level (TB) and petabyte-level (PB) storage systems for ongoing storage. SSD-based Redundant Arrays of Independent Disks (RAID) can provide mass and high-speed storage, and they rely on redundancy to protect data against data loss. Compared with hard disk drives (HDDs), SSDs benefit from lower access latency and energy consumption, and smaller rack space. However, SSDs suffer aging problems [121]. Especially in the RAID systems, parity updates incur extra writes and garbage collections (GC), which further degrades the lifetime of SSDs arrays. Reported from [47], 2%-7% SSDs develop at least one bad chip in the deployment of a data center. Frequently replacing failed drives makes big data application services unstable. In addition, among various methods for generating redundancy, several storage systems have been employing erasure coding to protect data due to the lower storage overhead. However, erasure coding on traditional processor-based implementations is still computationally expensive, further exacerbating the inefficiency of big data processing. Thus, it becomes extremely important to optimize big data storage systems in computing performance and operational costs.

In this thesis, we focus on optimizing big data storage systems with non-volatile

memories in computing performance and operational cost. Specially, we employ two kinds of emerging non-volatile memories, metal-oxide resistive random access memory (ReRAM) [4] and NAND flash memory, to improve the performance of large-scale graph processing and erasure coding, and to improve the lifetime of SSD-based arrays and flash chips. ReRAM stores information according to the creation and destruction of the conductive filaments in the metal oxide layer. ReRAM enjoys low access latency (programming latency is less than 30ns), low energy consumption (0.1-3 pJ per bit) and long endurance (up to  $10^{12}$ P/E cycles), so it can be a good candidate for main memory. Compared with other nonvolatile memories such as STT-RAM and phase-change memory (PCM) which either have fast access or have high retention and endurance features, only the ReRAM crossbar structure has the computational capability of performing matrix-vector multiplication and sum operations, which inherently fits the process-in-memory (PIM) concept. Moreover, NAND flash memory has been widely adopted as the storage medium in many storage devices due to its fast access speed, such as in SSDs and embedded boards. However, it is still challenging to well utilize these non-volatile memories. First, processing data with ReRAM in a PIM way needs to be carefully examined. In the case of processing large-scale graphs, the graph mapping scheme and the execution mechanism on ReRAM memory should be properly designed to reduce data movement overhead and richly utilize memory bandwidth. Second, existing approaches that reducing the writes traffic on flash memory and redistributing parity on SSDs gain few benefits to extend the lifetime of flash memory. With the huge-variety of big data, some special data features, such as error-tolerance, are well worth exploring.

In the first part of this thesis, we investigate utilizing ReRAM to improve both computational and I/O performance for large-scale graph processing. We study the algorithm of breadth-first search (BFS). We propose a novel ReRAM-based processing-in-memory architecture called RPBFS, in which graph data can be persistently stored and processed in place. In RPBFS, the ReRAM-based memory banks are separated into graph banks and master banks. We design an efficient graph mapping scheme, in which a graph bank stores the adjacency list of a graph partition. We also propose an efficient graph traversal algorithm that works through collaboration with a master bank to traverse a graph. In RPBFS, the data movement for a graph traversal is wrapped within graph banks, and the movement is only related to the synchronization of vertex bitmaps. Moreover, we propose an analytical performance model to analyze the graph traversal efficiency with RPBFS, which can help us identify bottlenecks and provide optimization opportunities for our design.

In the second part, we optimize the storage efficiency of big data system with NAND flash memory and ReRAM, achieving lower operational cost. The ability of storage systems to maintain service in terms of time, such as the lifetime of storage devices, is particularly relevant to the operational cost. Moreover, many storage systems have been employing erasure codes to protect data, with coding performance one of the key factors into the system efficiency.

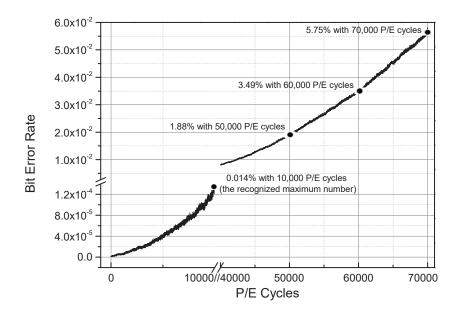

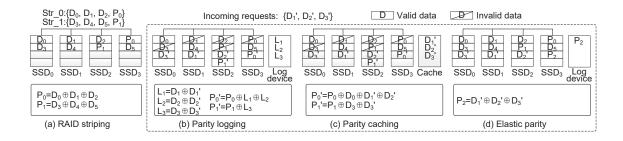

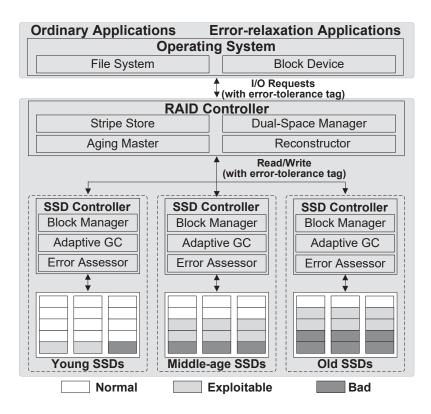

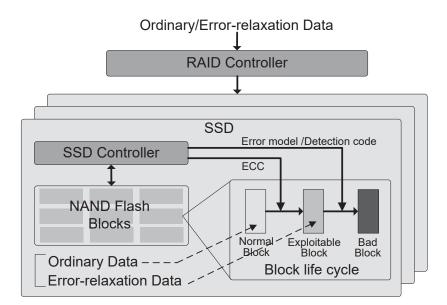

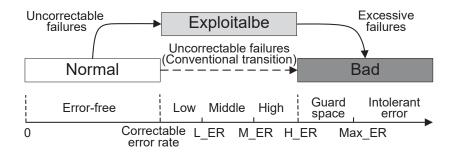

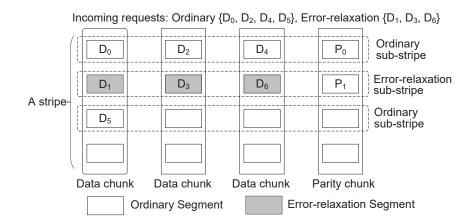

(1). We are the first to apply approximate storage, via the interplay of RAID and SSD controllers, to optimize the lifetime of SSDs arrays. We explore the benefits of relaxing the integrity constraints of flash blocks. Faulty flash blocks are reused to store approximate data that can tolerate some errors. With the goal of extending lifetime of SSD-based RAID arrays, we propose a cross-layer lifetime optimization framework, called FreeRAID (Flash-resurrection RAID). FreeRAID tightly couples the components in both RAID and SSD controllers. FreeRAID combines two techniques. First, with the knowledge of physical blocks in SSDs, the RAID controller in FreeRAID efficiently allocates normal and faulty blocks to serve data with different error-tolerances, and makes different types of data error-isolated. Also, FreeRAID and the existing optimized RAID schemes can coalesce to further reduce write traffic on SSDs. These optimized schemes include parity logging, parity caching and elastic striping. Second, FreeRAID can dynamically switch FTL strategies on an SSD to maintain access performance and storage efficiency. To determine whether data validity has been accomplished on faulty blocks, two error rate assessment approaches are proposed by considering two dominant errors sources of flash memory.

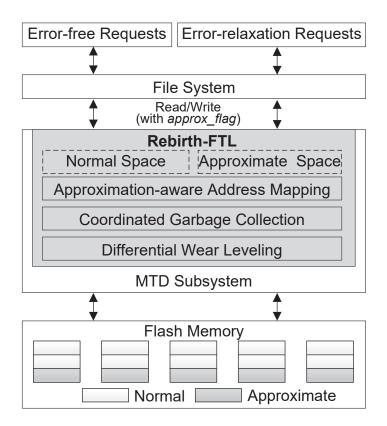

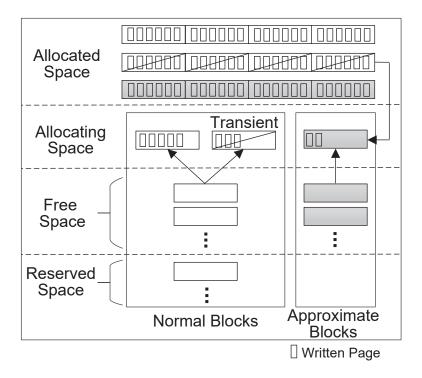

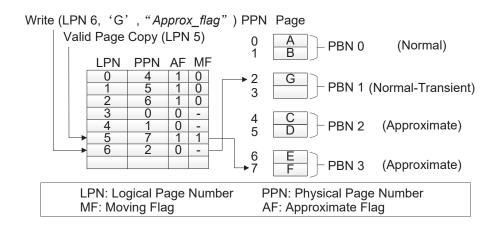

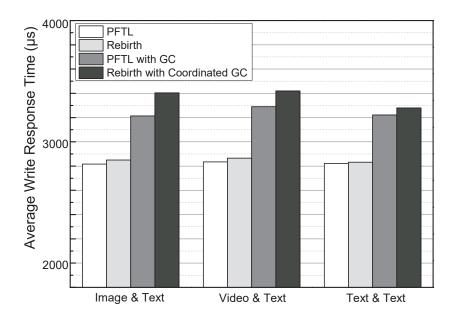

(2). For flash memory in embedded storage systems, we propose Rebirth-FTL, a pure software management in flash translation layer (FTL) for lifetime optimization. With an increasing amount of approximate data such as images and videos, Rebirth-FTL reuses

faulty blocks that contain uncorrectable errors to store these data. Rebirth-FTL efficiently and effectively manages two addressable spaces, approximate space and normal space, with efficient address mapping, coordinated garbage collection and differential wear leveling. To make the flash devices approximate information-aware, we demonstrate how to pass the approximate information from applications to flash devices through the whole Linux operating system (OS) in a top-down way. We analyze the benefits of a flash memory with Rebirth-FTL using a lifetime model. We implement and deploy Rebirth-FTL on an embedded development board and a simulator, and we demonstrate its effectiveness on them.

(3). The traditional processor-based RAID controller relies on Galois Field arithmetic to perform matrix-vector multiplication for erasure coding, which is computationally expensive on processors. We propose a novel ReRAM-optimized RAID system for accelerating erasure coding, called Re-RAID. Re-RAID uses ReRAM as the main memory in both RAID and SSD controllers, and it performs erasure coding on ReRAM crossbars. To minimize the overhead for recovering a single failure, we propose a confluent Cauchy-Vandermonde matrix as the generator matrix. Then, the SSDs can leverage their ReRAM memories to recover a single failure, which can greatly alleviate the computing workloads of a processor-based RAID controller. For multiple failures, processors and ReRAM memories in the RAID controller work in close collaboration. The processors construct a decoding matrix, and map the matrix to ReRAM memories, and then the ReRAM memories perform matrix-vector multiplication to recover lost data.

The rest of this chapter is organized as follows. The next section presents the related work. Section 1.2 discusses the unified research framework. We summary the contributions of this thesis in Section 1.3. Finally, Section 1.4 gives the outlines of this thesis.

#### 1.1 Related Work

In this section, we describe state-of-the-art work related to optimization approaches for big data systems in computing and storage.

In the previous work, there has been work done in three main domains: (I) Processingin-memory accelerator, (II) Approximate storage, and (III) Software-managed flash and RAID arrays. We briefly describe these techniques, and compare them with representative techniques in respective chapters.

#### 1.1.1 Processing-in-memory Accelerator

Processing-in-memory technique is an effective way to alleviate the bandwidth bottlenecks by integrating computational logic within or near memory. Recent studies have proposed in-memory accelerators for specialized applications. Mirzadeh et al. [80] push logic to-ward memory by leveraging 3D-stacked DRAM designs. The logic layer integrated with several DRAM dies can execute data-intensive operations. Jeddeloh et al. [50] propose a three-dimensional DRAM architecture in which the DRAM is moved to the logic layer with high-performance transistors. Timing, refresh and thermal management for DRAM can be optimized locally. Akin et al. [3] propose a near-memory accelerator integrated within 3D stacked DRAM, and Zhang et al. [143] move memory-intensive computations closer to memory in GPU. For large-scale graph processing, Ahn et al. [1] propose a programmable PIM accelerator by integrating many logic cores into 3D-stacked memory to increase memory bandwidth. The proposed architecture can process four graph algorithms, such as Single-Source Shortest Path (SSSP).

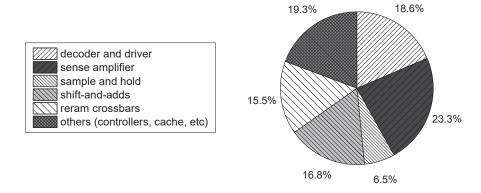

Due to the inherent computational capability of ReRAM, some recent studies also explore ReRAM to accelerate several kinds of applications in a PIM way. PRIME [19] is a PIM architecture to accelerate neural network applications. In PRIME, ReRAM serves as main memory and serves as computation units. The ReRAM crossbar is utilized to perform matrix-vector multiplication for neural network applications. ISSCC [113] and Pipelayer [119] are pipelined architectures with memristor crossbars for processing neural networks computations, and different parallelism granularities on them are explored to accelerate computation. ReRAM also has been studied for processing graph algorithms. Pinatubo [65] is a processing-in non-volatile memory architecture for bulk bitwise operations. The read circuitry redesigned for multi-row bitwise operations, is efficient for bitmap-based BFS processing. GraphR [120] follows the principle of near-data processing, and utilizes ReRAM crossbars to serve both storage and computational functions. The compressed graph data are persistently stored in ReRAM memory, and then the graph data can be converted to sparse matrix representation and mapped to other ReRAM memory for processing. However, the conversion incurs high execution and transfer costs. This thesis proposes a novel ReRAM-based PIM for graph processing without any conversion, and the data movement is wrapped within memory by an efficient mapping scheme and an efficient traversal scheme.

#### 1.1.2 Approximate Storage

Approximate storage exploits the error-tolerance of applications to reduce I/O latency and energy consumption of storage substrates. Bit-by-bit precision is costly for some applications; a small number of bit flips is acceptable to them, such as with videos and images. Recent work have demonstrated that approximate storage has led to multi-aspect improvements in solid state memories. Sampson et al. [109] propose reducing the number of write steps on PCM, to achieve higher write performance and energy savings. Similarly, Cui et al. [26] propose reducing the maximal threshold voltage for writes on 3D NAND flash memory, allowing write performance to be improved and the program disturbance in physical blocks to be alleviated. Ranjan et al. [100] leverage the error-tolerance of data to improve the energy-efficiency of spintronic memories. Sampson et al. [108] allow a programmer to declare precise data or approximate data, and then store approximate data to approximate storage including cheaper memory, cache, and registers, achieving significant energy saving at very little accuracy loss.

Recent researches have proposed applying approximate storage for specific applications. Jevdjic et al. [51] compute bit-level reliability requirements for encoded video by tracking coding dependencies, and they implement different levels of error correction for streams reliability needs. Guo et al. [38] propose a selective error correction technique to implement high-density image storage. Via a case study of JPEG images, they can significantly increase the storage density of PCM with negligible quality loss. In [39], Guo et al. use good error protection technique for the important parts of images and videos, while using minimal effort to protect less important parts. The proposed unequal error protection technique can attain higher quality with lower computational complexity. Palomino et al. [90] employ varying degrees of approximations at both the algorithmic and data levels to reduce on-chip temperature when processing a video. The regions of a video can be classified by an adaptive content-driven approximate technique, and then the regions with different approximate modes are processed with suitable approximate computing.

Our work shares a common principle with prior work of relaxing integrity constraints of storage substrates, but we aim to extend the lifetime of SSD-based RAID arrays and flash memories. This thesis focuses on software management at the RAID and FTL levels without the hardware changes (such as modifying the threshold voltage [109] [26]) or dedicated error correction codes (such as encoding videos with H. 264 [51]).

#### 1.1.3 Software-managed RAID Arrays and Flash

An SSD-based RAID array provides a virtual logical disk by combining the space of the SSDs. Striping and parity are two commonly-used RAID techniques in the RAID controller. With striping, logically sequential data are divided into data chunks. Parity is a redundancy-based protection scheme, by which parity data is generated based on a group of data chunks. Write updates incur additional writes for parity updates. To efficiently reduce write traffic, recent research has proposed various optimized schemes on RAID. Parity logging [122] utilizes a journaling scheme to reduce small writes cost by augmenting a log device. Parity caching scheme [21] delays parity updates by caching all incoming requests in a buffer, so the number of reads and writes for generating parity can be reduced. Elastic parity logging [66] encodes new incoming data chunks to form new stripes, and the parity for a partial stripe is appended to a log device. For SSD-based RAID arrays, Li et al. [67] propose an analytical model to quantify the reliability of arrays, which can help decide the appropriate parity

distribution. Pan et al. [91] propose a grouping-based elastic striping scheme to reduce both write traffic and response time on SSDs. Koo et al. [59] propose a dual RAID scheme which is a combination of RAID-5 and RAID-6 for maintaining high reliability and access performance. Besides that, the lifetime of SSD-based RAID arrays remains a major concern. Moon et al. [81] analyze the relationship between parity scheme and lifetime, and they find that write amplification is a major factor in the lifetime of RAID arrays. Yongseok et al. [87] use a log-structured cache to eliminate read-modify-write operations, and propose the use of destaging to enhance the lifetime of SSD arrays. Different from prior work which mainly focuses on reducing writes, our work explores the special features of big data, such as error-tolerance, to significantly extend the lifetime of SSD-based RAID arrays.

RAID schemes are categorized into several levels based on parity, and the methods for generating parity in a RAID system are varied. For example, with one to two parities generated for each stripe, RAID-5 and RAID-6 can tolerate one and two failed drive at any time, respectively. Many parity implementations exist. Fu et al. [36] propose a new Maximum Distance Separable (MDS) code with new parity chains and new parity distributions for RAID-6 to optimize degraded reads and partial stripe writes. With the same goal, D-Code [35] uses new kinds of horizontal parities to optimize I/O performance. Several codes are proposed to optimize parity computational complexity, including Tier-code [63], EVENODD [14], RD-P [24] and X-code [142]. Trifonov et al. [128] propose low-complex Reed-Solomon (RS) codes to improve encoding and decoding performance. Guruswami et al. [41] propose repair schemes for high-rate RS codes to optimize repair bandwidth in a cloud RAID system. Zhang et al. [144] propose an efficient Cauchy Reed-Solomon coding approach, called Caco.

The flash translation layer in the SSD controller manages flash memory. Several prior research studies specifically optimize FTL schemes in address mapping, garbage collection and wear leveling. Qin et al. [98] propose MNFTL to reduce the number of valid page copies for achieving low system response time. Liu et al. [70] propose RNFTL to improve the endurance and space utilization of blocks. DFTL [40] is an on-demand page-level FTL with one-level cache, with both the page-level mapping table and data blocks are stored in the flash memory. A block associative sector translation [58] scheme allocates a log block for only one

Figure 1.1: Unified Research Framework.

data block for the efficiency of address translation. Jimenez et al. [52] relieve the weakest pages to implement block lifetime extension with a wear unleveling technique. Chang et al. [17] propose a typical static wear-leveling strategy called SWL to save the management overhead of FTLs. In contrast to these prior works, our work leverages the special feature of data to optimize the lifetime of flash memory without any hardware changes.

#### **1.2 The Unified Research Framework**

We present the unified research framework of this thesis in this section. Figure 1.1 illustrates the sketch of our framework.

In this thesis, we optimize big data systems with non-volatile memories from graph computing to flash-based SSD arrays, as shown in Figure 1.1. The data generated from big data applications are classified into two types: normal data and approximate data. Normal data are precise data, such as graph and text data. Approximate data can tolerate some errors, such as video and image which can tolerate some died pixels. Our work contains two parts. In the first part for computing efficiency, we study the graph processing which is an important part of big data analysis. We investigate utilizing ReRAM to accelerate graph traversal. In the second part for storage efficiency, we propose integrating the RAID and SSD management to optimize the lifetime of flash memory by exploring the error-tolerance of approximate data. In addition, to improve the performance of erasure coding on SSD-based RAID arrays, we further propose leveraging ReRAM to achieve that.

In the first part, in Chapter 2, we propose a novel ReRAM-based processing-inmemory architecture for graph traversal, in which graph data can be persistently stored and processed in place. In the second part, in Chapter 3, we apply approximate storage via the interplay of RAID and SSD controllers to optimize the lifetime of SSDs arrays. The interplay tightly couples the components in both RAID and SSD controllers to efficiently manage the cross-layer space. In Chapter 4, we further explore approximate storage to optimize the lifetime of flash memory in FTL. We also demonstrate how to pass the approximate information from applications to flash devices in Linux OS. In Chapter 5, we use the ReRAM as an alternative main memory in both RAID and SSD controllers. The ReRAM-based main memory can perform erasure coding, which can greatly alleviate the computing workloads of processors in the controllers.

#### **1.3** Contributions

The contributions of this thesis are summarized as follows.

• To minimize data movement overhead, we investigate utilizing ReRAM to improve the performance of large-scale graph processing. We propose a novel ReRAM-based processing-in-memory architecture called RPBFS in which graph data can be persistently stored and processed in place. An efficient graph mapping scheme is proposed to map a graph on multiple ReRAM memory banks. We also design an efficient graph traversal algorithm in RPBFS. In addition, we propose an analytical performance model to analyze the benefits of a graph traversal in RPBFS.

- We explore exploitable blocks in SSDs to serve approximate data in SSD-based RAID arrays. We propose FreeRAID, which leverages the interplay between RAID and SSD controllers to extend the lifetime of SSDs arrays. FreeRAID integrates two key techniques: dual-space management which can efficiently allocate space for normal and approximate data, and adaptive-FTL which can dynamically switch FTL schemes of an SSD to improve its storage efficiency.

- For flash memory in embedded storage systems, we propose Rebirth-FTL, a pure software management in flash translation layer for lifetime optimization. Rebirth-FTL efficiently and effectively manages two spaces, approximate space and normal space, with approximation-aware address mapping, coordinated garbage collection and differential wear leveling. We also develop a scheme to pass approximate information from userland to kernel space in Linux. A lifetime model is also presented for lifetime analysis.

- We propose Re-RAID which uses ReRAM as the main memory in both RAID and SSD controllers. The erasure coding in Re-RAID can be processed in ReRAM memory. To minimize the overhead for recovering a single failure, we propose a confluent Cauchy-Vandermonde matrix as the generator matrix, which allows ReRAM memory on SSDs to perform the reconstruction task for a single failure.

- We implement prototypes with the proposed techniques, and demonstrate the effectiveness of the proposed schemes by conducting a set of experiments.

#### 1.4 Thesis Organization

The rest of this thesis is organized as follows.

• In Chapter 2, the first part of this thesis, we focus on optimizing the computational performance for big data. We investigate utilizing ReRAM to improve the performance of large-scale graph processing.

- In Chapter 3, the start of the second part, we optimize the storage efficiency of big data systems with NAND flash memory and ReRAM to achieve lower operational cost. We apply approximate storage via the interplay of RAID and SSD controllers to improve the lifetime of SSD-based RAID arrays.

- In Chapter 4, to extend the lifetime of flash memory in embedded storage systems, we propose Rebirth-FTL which reuses faulty blocks that contain uncorrectable errors to store approximate data for lifetime optimization in FTL.

- In Chapter 5, to alleviate the computing workloads of the RAID controllers, we propose Re-RAID which uses ReRAM as the main memory in both RAID and SSD controllers, and erasure coding can be processed in ReRAM memory.

- In Chapter 6, we present our conclusions and possible future directions for research arising from this work.

#### **CHAPTER 2**

# A NOVEL RERAM-BASED PROCESSING-IN-MEMORY ARCHITECTURE FOR GRAPH TRAVERSAL

#### 2.1 Introduction

The uses of graph-based computation for analyzing and understanding social networks, complex engineering systems, and metabolic networks are ubiquitous. With the tremendous increase in the amount of information, relationships between objects are often linked to form large-scale graphs, such as the friend relationship in social networks. In the above areas of applications, the common graph-theoretic algorithms on the large-scale graphs have been becoming increasingly important. A well-known example of algorithms is the breadth-first search that allows the peer-to-peer network BitTorrent to search all neighbors [22]. Current graph processing schemes mainly concentrate on CPU-based and GPU-based platforms. These traditional platforms separate graph processing into memory processing and processor processing, and it is still challenging to achieve good performance due to the many random and irregular memory accesses. This mechanism leads to a huge amount of data movement between memories and processors, so that the processors always wait for memories and execute instructions slowly [12] [1]. Moreover, the off-chip main memory system is a major consumer of energy due to the high capacitive load and power of buses and memory [115]. Although continuous efforts are being made to improve the multi-core parallelism and to optimize memory access performance, the data transfer between memory and processor in traditional platforms still represents one of the most significant bottlenecks for both performance and energy when performing graph-based algorithms. The possibility of reducing the data movement overhead in memory is therefore well worth exploring.

Processing-in-memory technique is an effective way to alleviate the bandwidth bottlenecks by integrating the computation logic within or near memory, so the memory-intensive computations can fully utilize the available memory bandwidth. Recent studies have proposed in-memory accelerators for specialized applications to reduce data movements [19] [125] [113] [119] [73] [143] [10] [149]. For example, Ahn et al. integrate PIM technology into 3D-stacked memory to increase memory bandwidth for graph processing [1]. Ozdal et al. propose an accelerator architecture to reduce the irregular access patterns and asymmetric convergence [88]. Although they are architectural accelerators for graph analysis, they cannot make graphs persistently stored in memory so as to involve slow secondary storage, and they ignore the effect of graph mapping and distribution on performance.

An emerging non-volatile memory, metal-oxide resistive random access memory, has the capability to perform arithmetic operations inside data storage [136], which inherently fits the concept of PIM. ReRAM enjoys lower access latency, lower energy consumption, and superior endurance than other non-volatile memories [139] [138] [134] [69]. Its most novel aspect is that the ReRAM crossbar structure is efficient at performing matrix-vector multiplication, which has been studied for neural network computation [19] [113] [119]. Furthermore, ReRAM crossbar has the potential to perform iterative graph processing algorithms. First, graph processing algorithms are not computation-intensive but memoryintensive [89] [72], and most of them (e.g., page-rank, graph traversal) can tolerate the imprecision arising from analog-to-digital conversions. Moreover, considering the fact that the size of cells keeps shrinking, multi-level cell (MLC) technology enables one ReRAM cell to store more information [5] [141] [98], which is suitable as a storage device to store large-scale graphs. Therefore, with the efficient capability in both storage and computation, ReRAM crossbar exhibits the potential to accelerate graph processing.

In reconsidering the connection between the computation and storage aspects of ReRAM crossbars, it is still challenging to utilize ReRAM crossbars to perform graph processing. First, a graph with several million vertices and edges needs to be mapped to multiple ReRAM crossbars, so the graph representation needs to be carefully organized. There are two major approaches to representing a graph: adjacent matrix and adjacency list. It is impractical to store the whole adjacent matrix in ReRAM, since the matrices of the real world graphs are highly sparse. For adjacency list, there are a number of formats, and each with different storage cost, computational characteristics and organizations. Second, the execution mechanism of ReRAM crossbars should be designed properly. Since most graph algorithms are iterative, it is important to maintain correctness in processing and the consistency of the intermediate data among all of the subgraphs located on the ReRAM crossbars. Some works have integrated ReRAM for large-scale graph processing [120] [45]. GraphR follows the principle of near-data processing, and it utilizes ReRAM crossbars for storage and computation [120]. The compressed graph data is persistently stored in ReRAM memory; however, it needs to be converted to sparse matrix representation for graph processing in ReRAM crossbars. The conversion incurs execution cost and transfer cost. Therefore, the data movement between ReRAM crossbars remains large, even the data do not need to pass through the memory hierarchy as in traditional platforms.

In this work we focus on accelerating graph traversal, and propose a novel ReRAMbased PIM architecture for BFS (RPBFS). RPBFS is a distinct ReRAM-based PIM architecture from recent PIM work. In this architecture, the ReRAM-based memory banks are separated into graph banks and master banks. The compressed adjacency lists are persistently mapped and scattered over multiple graph banks by an efficient mapping scheme. The master bank is selected for a graph to perform graph traversal through collaboration with graph banks. To reduce the data movement overhead, we design an efficient traversal scheme that can constrain the graph expansions inside the memory bank, and can parallelly perform the expansions on multiple memory banks. The movement of data in the RPBFS is only related to the synchronization of vertex bitmaps, which is much smaller than that of graph data. We also further explore the effect of graph distributions through an analytical performance model.

We conduct a series of experiments to evaluate the RPBFS across a wide variety of graphs compared with the state-of-the-art CPU-based and GPU-based parallel solutions [11] [71]. Our architecture yields speedups of up to  $33.8 \times$  on the graph traversal performance, and achieves energy reductions of up to  $142.8 \times$  over conventional systems. The results also

verify the improvement in the performance of different graph partitioning schemes as the optimizing opportunity identified by an analytical model.

This work explores graph traversal based on ReRAM crossbars. We believe that our proposed architecture can also benefit other graph algorithms, such as single source shortest path. To summarize, this chapter makes the following contributions:

- We design a novel ReRAM-based PIM architecture with a set of peripheral circuits. An efficient graph mapping scheme is proposed to map a graph on multiple ReRAM memory banks.

- We design efficient graph traversal algorithms for graph banks and master banks, respectively. Data movement is minimized and bank-level parallelism is explored to effectively accelerate graph traversal.

- We propose an analytical performance model for our ReRAM-based PIM implementation. Finally, we evaluate our proposed scheme using a variety of real world graphs and compare it with other state-of-the-art solutions.

The rest of this chapter is organized as follows. The next section gives basic background to this study and gives a motivation example. Section 2.3 describes the architecture of RPBFS, as well as the graph mapping scheme. In Section 2.4, we briefly introduce how graph traversal proceeds on the RPBFS architecture. An analytical performance model is presented in Section 2.5, and we apply it to explore the optimization opportunity. Section 2.6 evaluates the performance of RPBFS in several key metrics. Finally, Section 2.7 discusses related work, and Section 2.8 concludes this chapter.

#### 2.2 Background and Motivation

In this section, we first present the background on graph representation, BFS traversal and ReRAM basics. Then we use a motivation example to illustrate the traversal efficiency on a ReRAM crossbar.

Figure 2.1: An example graph G and one of its valid traversal trees.

#### 2.2.1 Graph Representation

Assuming a graph G with vertex set V and edge set E, there are a number of popular graph representations. Adjacency matrix and adjacency list are the most commonly used representations of graph, and the choice of the graph representation is situation specific.