#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

## Real-Time Feedback Control Mechanism on Packet Switching Network

### by Yam Kam Tai

Chief Supervisor Dr. C. K. Li Industrial Supervisor Mr. H. L. Yiu

10 June 2003

Department of Electronic and Information Engineering

The Hong Kong Polytechnic University,

Hunghom, Kowloon,

Hong Kong

A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF PHILOSOPHY TO THE HONG KONG POLYTECHNIC UNIVERSITY

### **Abstract**

This project is a joint research between Motorola (HK) Semiconductor Product Sector Limited Company and the Hong Kong Polytechnic University. In this project, Internet Telephony is studied as an example of real time traffic communication in Internet.

In recent years, due to the popularity of Internet and many applications that are associated with it, more emphases are focused on the QoS of delivery to Internet-users. At the beginning of the thesis, background research on packet voice is presented. It includes:

- (i) Several classic packet voice models.

- (ii) Real Time Protocol (RTP) and Real Time Control Protocol (RTCP) protocols.

- (iii) Definition of QoS and traffic management algorithm in Internet communications.

The real time communications issue in packet switching network is addressed.

This study providing an overview on the current technology on what one should consider in real time packet communications.

Base on above studies, a new traffic control algorithm, namely the Real Time

Feedback Control Mechanism (RFCM) is developed for Internet real time traffic management. The mechanism provides real time monitoring and scheduling base on individual channel characteristic. The proposal RFCM improves channel utilization in both of real time and non-real time data distribution. The main advantage of the RFCM is its provision of dynamic adjustment on the bandwidth utilization for different types real time applications. Network Simulations (NS2)[24] is used to validate the supervisor properties of the proposed RFCM.

Besides on the theoretical analysis of traffic management, a new systematic and flexibility design methodology in central office communications equipment - Common Communication Platform (CCP) is introduced. It is a generic hardware and software platform on how to design network equipment. By using such model, it reduces the cycle time and reuses the previous knowledge in designing network equipment. Also, a high density DSP array board is designed in this platform. Such board contains 64 DSPs in Compact PCI 6U form factor. It uses data hub (designed by FPGA) to interconnect the board's processor and the DSP farm. By using this board, it can increase the number of voice channel to support in a single networking system. Hence, with this hardware, the proposed RFCM and other algorithm can be implemented for further investigation.

## About the Motorola Semiconductors HK Ltd

Motorola Inc. is one of the world's leading providers of electronic equipment, systems, components and services produced for worldwide markets. Motorola products include two-way radios, telephones systems, semiconductors, defenses and aero-space electronics, automotive and industrial electronic equipments, data communications and information processing and handing equipments. The Corporate Headquarters is in Chicago, Illinois of the United States.

By specific product line, Motorola serves its customers as six groups - Semiconductor Products Sector, General Systems Sector, Land Mobile Products Sector, Messaging, Information and Media Sector, Government and Systems Technology Group and Automotive, Energy and Controls Group

The main role of Semiconductor Products Sector is to design, produce and distribute a broad line of discrete semiconductors and integrated circuits, including microprocessors, RF devices, microcomputers, memories and sensors.

## Acknowledgments

The author wishes to convey his sincere thanks to his supervisor, Dr. C. K Li for his excellent supervision of his project.

Thanks also to Motorola for providing me the financial support to the Teaching Company Scheme for his project and to Mr. H. L Yiu, General Manager of Network and Communications System Group of Motorola for his technical advice and guidance. The author would also like to thanks all the team members (Jeffrey Ho, Kevin Lam, Alex Wong, Joshua Leung, Wilson Lo, Fat, Matthew Liong and Lewis Tse) in Networking and Computing System Department (NCSD) for great support on this research project.

Last but not the least, I would like to thanks to my family for their love and kindness. Without any of the above people this research project and my thesis will never come to existence.

## Contents

| Abstract                                 |      |

|------------------------------------------|------|

| About the Motorola Semiconductors HK Ltd |      |

| Acknowledgments                          | IV   |

| Contents                                 | v    |

| List of Figures                          | viii |

| List of Tables                           | xı   |

| List of Symbols and Abbreviations        | XII  |

| CHAPTER 1                                | 1    |

| 1.1 Currently Algorithm                  | 3    |

| 1.2 Proposed Algorithm                   | 5    |

| 1.3 Scope of Thesis                      | 5    |

| CHAPTER 2 8                                                      |

|------------------------------------------------------------------|

| 2.1 QoS Parameter Measurement11                                  |

| 2.2 Real Time Protocol Design18                                  |

| 2.3 Common Voice Model Analysis20                                |

| CHAPTER 328                                                      |

| 3.1 Performance Requirement for Internet Telephony               |

| 3.2 Architecture and Network Solution on IP Phone33              |

| 3.3 Gateway Architecture on VoIP36                               |

| CHAPTER 4                                                        |

| 4.1 Direct Adjustment Algorithm (DAA)44                          |

| 4.2 Adaptive Layered Transmission Scheme (ALT)50                 |

| 4.3 Open Issues for These Networks59                             |

| CHAPTER 5 61                                                     |

| 5.1 Background                                                   |

| 5.2 Real Time Feedback Control Mechanism (RFCM)                  |

| 5.3 Simulation on Real time Feedback Control Mechanism (RFCM) 71 |

| CHAPTER 6 84                                                     |

| 6.1 Communications Common Platform (CCP) Architecture84          |

| 6.2 Hardware Design on Communications Common Platform (CCP) 85   |

| 6.3 Software Design on Communications Common Platform (CCP) | 92    |

|-------------------------------------------------------------|-------|

| CHAPTER 7                                                   | 103   |

| 7.1 Design Architecture                                     | . 103 |

| 7.2 Functional Description                                  | . 107 |

| 7.3 System Driver Control                                   | .110  |

| 7.4 DSP Array Board Performance Measurement                 | .116  |

| CHAPTER 8                                                   | 127   |

| 8.1 Conclusion                                              | 127   |

| 8.2 Further Improvement and Research Direction              | 132   |

| Reference1                                                  | 34    |

| Appendix A: H.323 and SIP Reference Model1                  | 139   |

| Appendix B : DSP Array Board Driver Design1                 | 49    |

## List of Figures

| Figure 2-1 RTP Protocol Stack                                           | 20          |

|-------------------------------------------------------------------------|-------------|

| Figure 2-2 MMPP Model, N Multiplexed Voice Sources                      | 25          |

| Figure 2-3 Statistical Multiplexer for Input Model                      | 26          |

| Figure 2-4 Two-dimensional State Space                                  | 26          |

| Figure 3-1 Server Side Solution for Voice over IP Gateway               | 37          |

| Figure 3-2 IP Telephony Reference Design on Client Side                 | 38          |

| Figure 3-3 IP Telephone Software Architecture                           | 41          |

| Figure 4-1 Direct Adjustment Algorithm Performance Testing Topology     | 48          |

| Figure 4-2a Rate of Single Connection of DAA under 5µ Second Round Trip | Times and   |

| Link Bandwidth                                                          | AQ          |

| Figure 4-2b Rate of Single Connection of DAA under 5m Second Round Trip | Times and   |

| Link Bandwidth                                                          | / Times and |

| Figure 4-2c Rate of Single Connection of DAA under 100m Second Round    | Trin Times  |

| and Link Bandwidth                                                      | /10         |

| Figure 4-3 Diagram of the Control Scheme with Three Layers              | 54          |

| Figure 4-4 Diagram of the Control Scheme with Three Layers              | 56          |

| Figure 4-5 A Three State Active-idle Source                             | 56          |

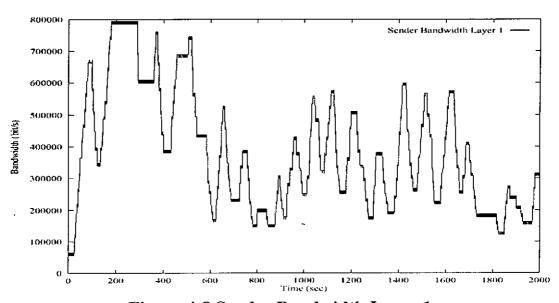

| Figure 4-6 Sender Bandwidth Layer 3                                     | 50<br>57    |

| Figure 4-7 Sender Bandwidth Layer 2                                     | 58          |

| Figure 4-8 Sender Bandwidth Layer 1                                     | 58          |

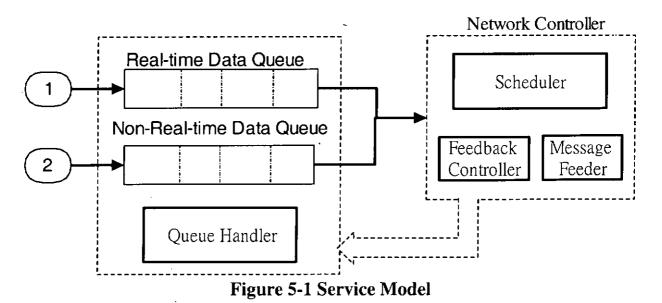

| Figure 5-1 Service Model                                                | 64          |

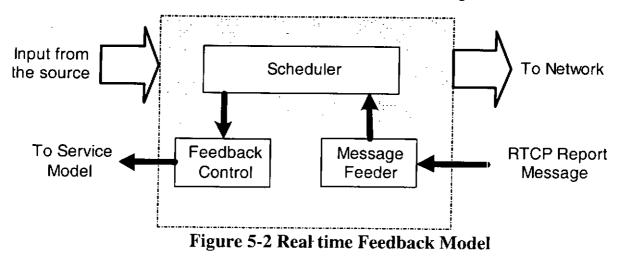

| Figure 5-2 Real time Feedback Model                                     | 66          |

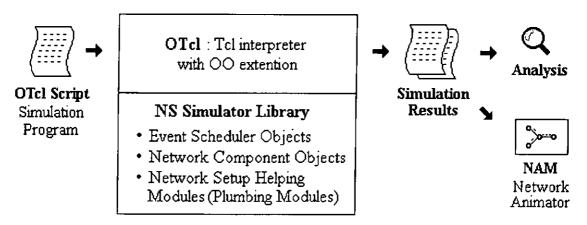

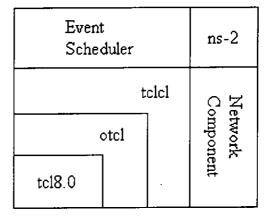

| Figure 5-3 User's View of NS                                            | 71          |

| Figure 5-4 Architectural View of NS                                     | 72          |

| The Hong Kong Polytechnic University                                    | VIII        |

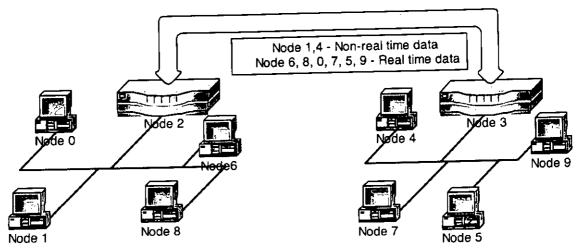

| Figure 5-5 Network Topology                                           | 74     |

|-----------------------------------------------------------------------|--------|

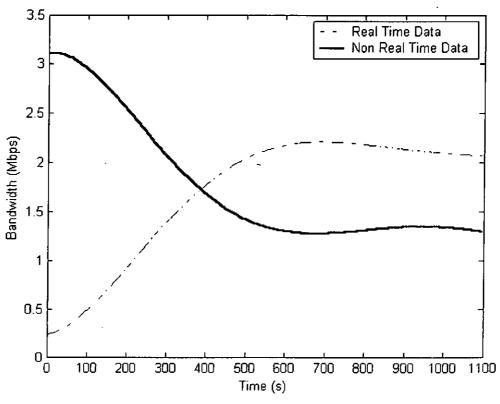

| Figure 5-6 Channel Capacity against Time                              |        |

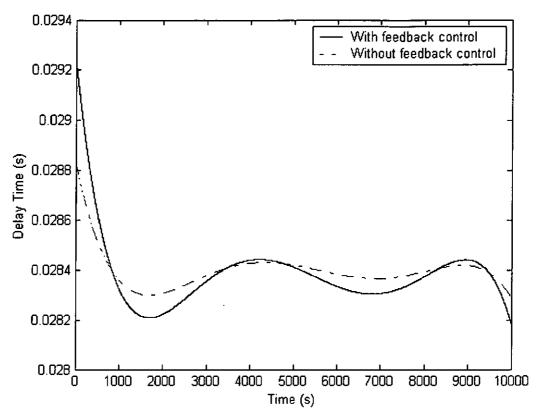

| Figure 5-7 Delay against Time                                         |        |

| Figure 5-8 Bus Network Topology                                       |        |

| Figure 5-9 Channel Utilization against Time                           |        |

| Figure 5-10 Delay against Time                                        |        |

| Figure 5-11 Bandwidth against Time on Link 2-3                        |        |

| Figure 6-1 Hardware Design Architecture for VoIP Equipment            |        |

| Figure 6-2 Architecture of DSP Array Board                            |        |

| Figure 6-3 Architecture of T1/E1 Line Card                            |        |

| Figure 6-4 Multimedia Application Software Design Architecture        |        |

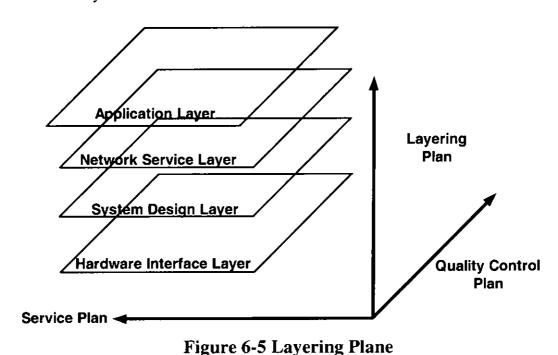

| Figure 6-5 Layering Plane                                             |        |

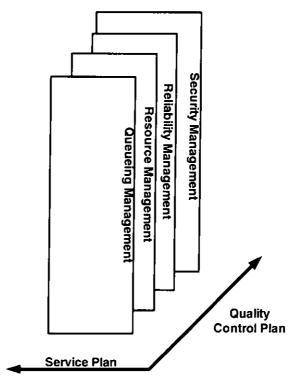

| Figure 6-6 Quality Control Plane                                      |        |

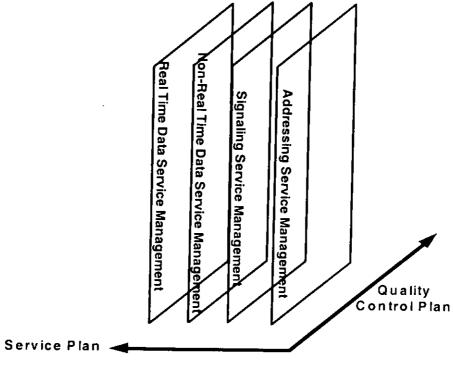

| Figure 6-7 Service Plane                                              |        |

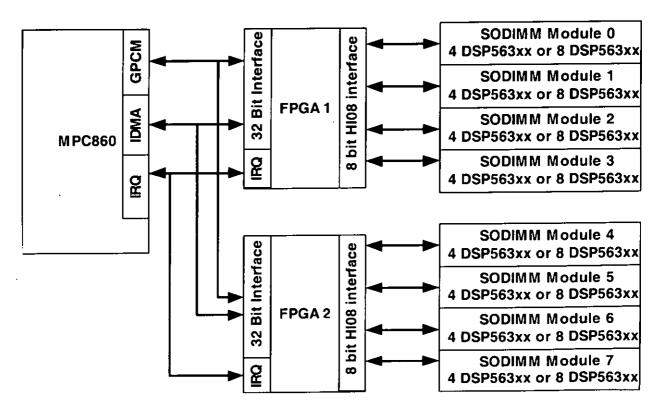

| Figure 7-1 64 DSP Configuration Using Data Hub Control                |        |

| Figure 7-2 HI08 Bus Interface                                         |        |

| Figure 7-3 Dual Data Hub Interface                                    | 112    |

| Figure 7-4 Data Hub (FPGA) FIFO Structure                             |        |

| Figure 7-5 FPGA Tx/Rx-FIFO                                            | 113    |

| Figure 7-6 DSP Status Structure                                       | 115    |

| Figure 7-7 Structure of HI08 Interface Driver                         | 116    |

| Figure 7-8 Time Diagram for 16 Bytes of Data                          | 119    |

| Figure 7-9 Doubling Time Diagram for 16 Bytes of Data                 | 119    |

| Figure 7-10 Time Diagram for 32 Bytes of Data                         | 119    |

| Figure 7-11 Continuous Send Data from Different Number of DSP         | 121    |

| Figure 7-12 Continuous Receive Data from Different Number of DSP      | 122    |

| Figure 7-13 Average Delay in By-pass Mode and IDMA Mode from MPC860   | to DSP |

| Direction                                                             | 124    |

| Figure 7-14 Average Delay in By-pass Mode and IDMA Mode from DSP to M | PC860  |

|                                                                       | 125    |

| Figure 7-15 Average Delay Using IDMA Mode on Both Directions          | 125    |

| Figure 7-16 IDMA Mode Ratio on Both Directions (DMA-Tx/DMA-Rx)        | 126    |

| Figure 7-17 Delay Ratio on Both Directions (By-pass Mode /IDMA Mode)  | 126    |

| Figure A-1 Protocol Stack                                             | 141    |

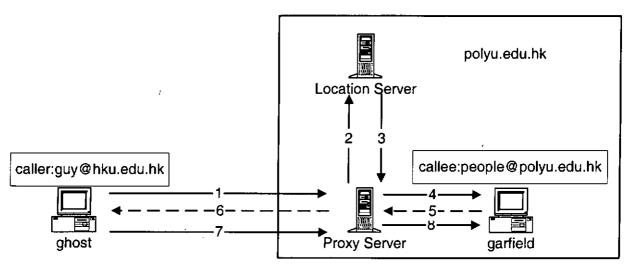

| Figure A-2 Through Proxy Server                                       | 148    |

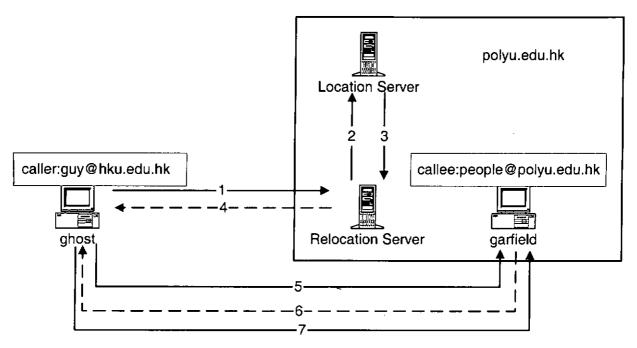

| Figure A-3 Through Relocation Server                                  |        |

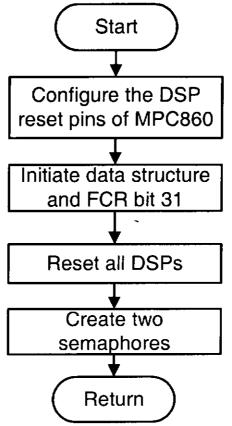

| Figure B-1 Flowchart of Hinit                                         |        |

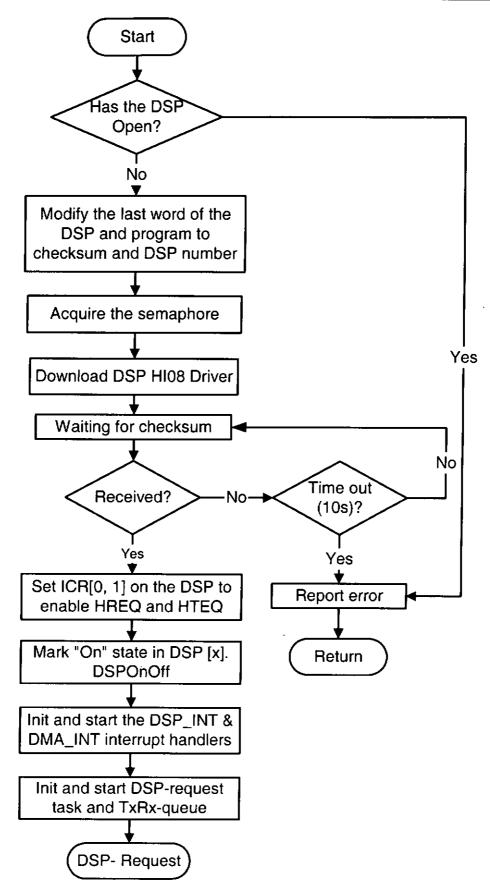

| Figure B- 2 Flowchart of Hopen                                        | 151    |

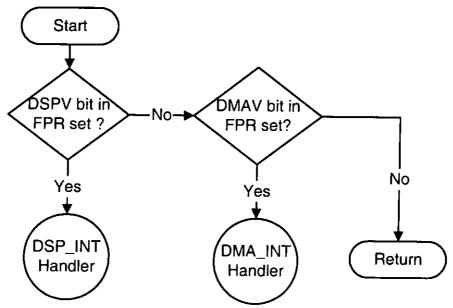

| Figure B- 3 Flowchart of Interrupt Handler                               | 152   |

|--------------------------------------------------------------------------|-------|

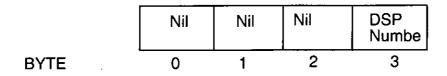

| Figure B- 4 Format of messages sent to TxRx-Queue                        | 153   |

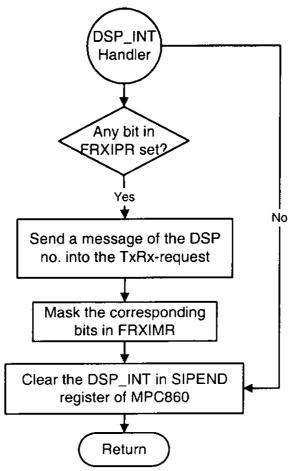

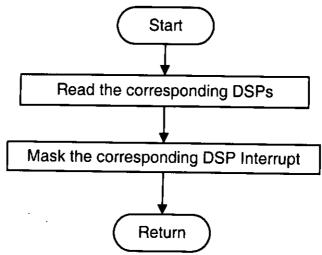

| Figure B- 5 Flowchart of DSP_INT interrupt handler                       | 153   |

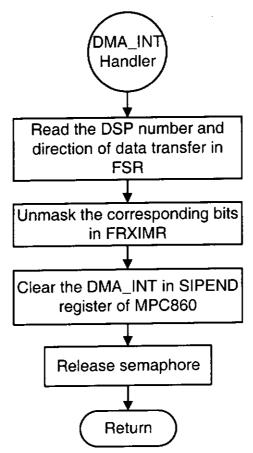

| Figure B- 6 Flowchart of DMA_INT Interrupt Handler                       | 154   |

| Figure B- 7 Request Type and Structure of the DSP header                 | 155   |

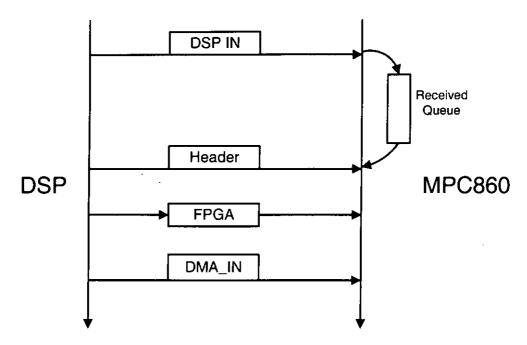

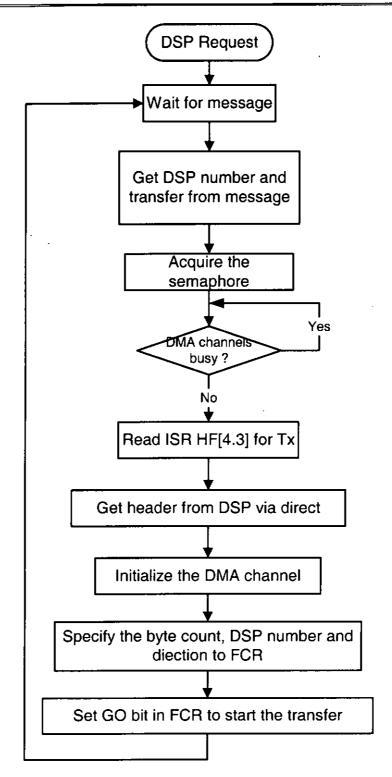

| Figure B- 8 Flow of the IDMA Data Transfer from DSP to MPC860            | 156   |

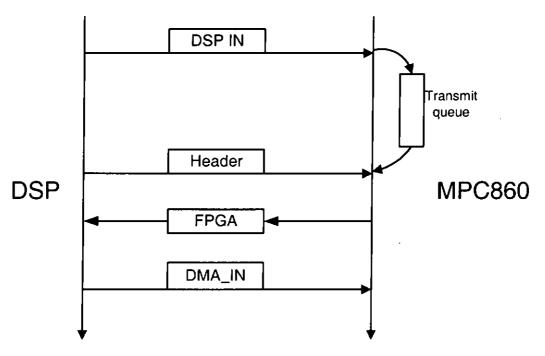

| Figure B- 9 Flow of the IDMA Data Transfer from MPC860 to DSP            | 156   |

| Figure B- 10 Flowchart of data transfer between MPC860 and DSPs via data | a hub |

| Interface                                                                | 157   |

| Figure B- 11 Flowchart of Hclose                                         | 158   |

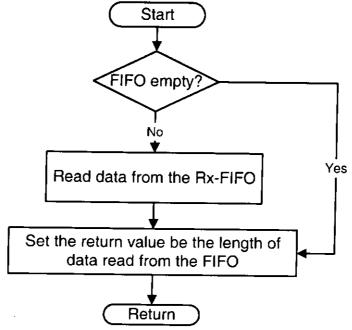

| Figure B- 12 Flowchart of FIFO Read                                      | 158   |

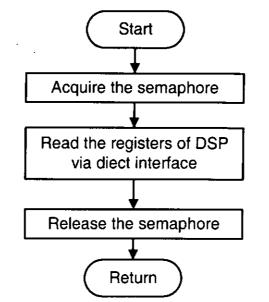

| Figure B- 13 Flowchart of DSP Read                                       | 159   |

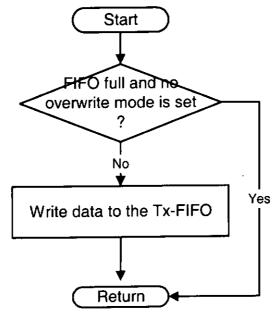

| Figure B- 14 Flowchart of FIFO Write                                     | 160   |

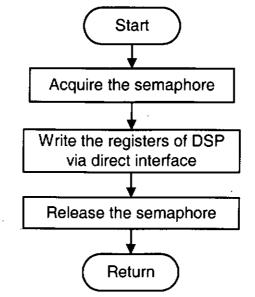

| Figure B- 15 Flowchart of DSP Write                                      | 161   |

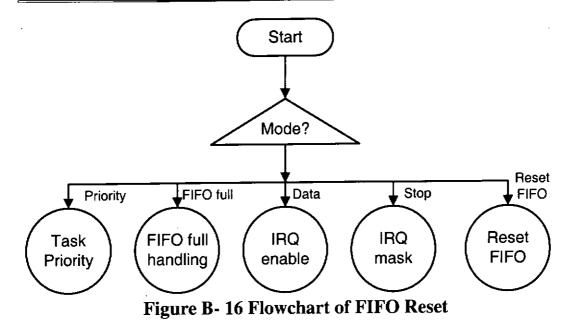

| Figure B- 16 Flowchart of FIFO Reset                                     | 162   |

## List of Tables

| Table 3-1 Codec Bit Rates, Delays                                             | 31  |

|-------------------------------------------------------------------------------|-----|

| Table 4-1 Link Utilization with the Direct Adjustment Algorithm for Different |     |

| Propagation Delays (τ) and Link Rates (α)                                     | 50  |

| Table 4-2 Parameter Values for the Adaptation Instances                       | 57  |

| Table 7-1 Parameter Values for the Adaptation Instances                       | 123 |

## List of Symbols and Abbreviations

| ADPCM       | Adaptive Differential Pulse Code Modulation                    |

|-------------|----------------------------------------------------------------|

| ALT         | Adaptive Layered Transmission Scheme                           |

| API         | Application Programming Interface                              |

| ATM         | Asynchronies Transfer Mode                                     |

| BSP         | Board Support Package                                          |

| CCP         | Communications Common Platform                                 |

| Compact PCI | Compact Peripheral Component Interface                         |

| CPM         | Communications Processor Module                                |

| CPU         | Center Processing Unit                                         |

| CTMC        | Continuous-Time Markov Chain Model                             |

| DAA         | Direct Adjustment Algorithm                                    |

| DBA         | Dynamical Bandwidth Arbitrator                                 |

| DMA         | Direct Memory Access                                           |

| DSP         | Digital Signal Processor                                       |

| DTMF        | Dual Tone Multi Frequency                                      |

| FCR         | FPGA Control Register                                          |

| FEC         | Forward Error Correction                                       |

| FPGA        | Field Programmable Gate Array                                  |

| FTP         | File Transfer Protocol                                         |

| G.711       | Pulse Code Modulation (PCM) of Voice Frequencies [ITU          |

|             | Recommendations]                                               |

| G.729       | Coding of Speech at 8 kbit/s using Conjugate-structure         |

|             | Algebraic-code-excited Linear-prediction (CS-ACELP) [ITU       |

|             | Recommendations]                                               |

| G.723.1     | Dual Rate Speech Coder for Multimedia Communications           |

|             | Transmitting at 5.3 and 6.3 kbit/s                             |

| GMII        | Gigabit Media Independent Interface                            |

| GPCM        | General Purpose Chip-select Machine                            |

| H.110       | Hypothetical Reference Connections for Videoconferencing Using |

|             | Primary Digital Group Transmission                             |

| H.323       | Packet-based Multimedia Communications Systems                 |

| HI08        | 8-bit Parallel Host Interface                                  |

|             |                                                                |

IDMA Independent Direct Memory Access

IP Internet Protocol

LAN Local Area Network

LPAS Linear Prediction Analysis by Synthesis

LPC Linear Predictive Coding

MAC Media Access Control

MAN Metropolitan Area Network

MIPS Million-Instruction Per Second

MMPP Markov Modulated Poisson Process

MMU Memory Management Unit

NS Network Simulator

OSI Open System Integration

Otcl Object-Oriented Tool Command Language

PABX Public Automatic Branch Exchange

PCM Pulse Code Modulation

PCI Peripheral Component Interconnect

PHY board Physical board POST Power On Self Test

PSOS Real Time Operating System for Embedded Microprocessors

RFCM Real Time Feedback Control Mechanism

RTOS Real Time Operation System

PSTN Public Switch Telephone Network

QoS Quality of Service

RLM Receiver-Driven Layered Multicast

RMII Reduced Media Independent Interface

RTCP Real Time Control Protocol RTOS Real Time Operating System

RTP Real Time Protocol

SAD Speed Activity Detector

SDRAM Synchronous Dynamic Random Access Memory

SIU System Interface Unit

SLIC Subscriber Line Integrated Circuit

SMP Semi-Markov Process Model

SNMP Simple Network Management Protocol

SSRC Synchronization Source

TDM Time-Division Multiplex

TFTP Trivial File Transport Protocol

UAS Uniform Arrival and Service Model

UISA User Instruction Set Architecture

UTOPIA Universal Test and Operations PHY Interface for ATM

VAD Voice Activity Detector VCI Virtual Channel Index

VoIP Voice over IP

VPI Virtual Path Index

VxWork Real Time Operating System for Embedded Microprocessors

WAN Wide Area Network

#### **CHAPTER 1**

### Introduction

IP Telephony is one of multimedia communications applications that allow several users to share the same physical transmission media using packet-switching communications method. Nowadays, the technology of IP Telephony is growing faster and mutual. Most of its applications are used for long-distance call. The reason is that it offers lower price to end-users as well as less maintenance cost. Within the framework, it also provides integration of voice and data multimedia communications. However, the lack of QoS control in today's Internet restricted the applications of any serious real time multimedia communications. Data transmission over Internet only operates on a "best effort" packet delivery basis, with no prioritization on which packets get delivered first or which packets are less likely to be lost. Due to congestion at routers within a network, unpredictable delay and unrecoverable packet loss in real time network is not acceptable but today's Internet technology cannot provide a solution with sufficient QoS control.

This issue affects the growth of IP Telephony and must be faced in future multimedia Internet development.

Traditionally, voice communications uses circuit-switching method such as Public Switching Telephone Network (PSTN). PSTN does not provide any method for voice compression and silence detection. Each dedicated call must reserve 64kbps bandwidth between two end-users. Although there is no traffic during silence period, the bandwidth still occupied. Until the call is finished, the line is free up for other users.

The most significant difference between Internet Telephony, also known as Voice over IP (VoIP), and traditional PSTN is bandwidth utilization for each connection. Internet Telephony is packet-based and does not reserve any bandwidth for two-end users. It means that the channel may not reserve sufficient bandwidth for voice transmission when comparing with circuit-switching network. Also, additional processes have to be done in Internet Telephony before transmitting out voice signal such as voice coding, compression and packetization. On the other side, there are issues that affect any real time transmission such as packet collusion, packet loss and packet delay. Those issues are the main factors that seriously affect the corresponding QoS.

With the reference to the original objective of PSTN and Internet, they are totally different. PSTN is designed for voice (real time) communications as Internet (packet switching network) is used for data (non-real time) communications. They have different

protocols to support their nature of data transmission such as packet encoding; network signaling, packet switching and terminal addressing method. The challenge is to integrate and handle real time data on Internet environment to provide multimedia service.

Traditional problems, such as packet delay and packet loss, should be addressed in order to guarantee the performance of Internet telephony application. New protocol design is also needed to handle voice packet in term of call setup signaling and timing measurement. Due to above reasons, it has to re-engine and re-design the Internet technology to enhance its functionality and reliability for multimedia service in Internet.

#### 1.1 Currently Algorithm

Network traffic control is one of main task to provide QoS for different applications. In packet-switching network, it needs to provide different types of traffic control mechanisms so as to delivery different level of QoS according to different situation. Currently, research effort indicates that there are two systematic and realistic approaches for traffic control. They are,

- 1. Direct Adjustment Algorithm (DAA)

- 2. Adaptive Layered Transmission scheme (ALT)

#### 1.1.1 Direct Adjustment Algorithm (DAA)

The Direct Adjustment Algorithm is based on both additive increase/multiplicative decrease approach under the same round trip time, packet size and loss ratio. It uses Real Time Control Protocol (RTCP) control message content to reflect the channel loss rate and round trip delay.

When the sender receives the control message, it calculates the smooth loss ratio  $L_s$ . If  $L_s$  is greater than 16%, then the sending rate is reduced by half. If  $L_s$  is smaller than 16%, then the sender sets its transmission rate  $R_A$  which depending on the Additive Increase Factor (AIF).

#### 1.1.2 Adaptive Layered Transmission Scheme (ALT)

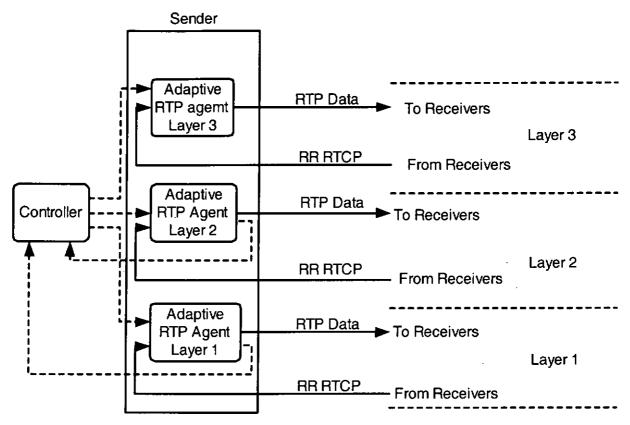

With the Adaptive Layered Transmission Scheme approach, the sender dynamically redistributes data stream on different layers based on the feedback of the receivers. In addition, ALT allows for dynamic discovery of the appropriate transmission rate for each layer. Receivers notify the sender of their view of the network congestion state using the Real Time Control Protocol (RTCP). The sender reacts to the reported loss rates by shifting bandwidth between the layers and keeping the overall sending rate constant. The scheme tries to provide all connected receivers on all layers with the best possible quality.

#### 1.2 Proposed Algorithm

In this research, a new mechanism is proposed for traffic control using in real time applications, called Real Time Feedback Control Mechanism (RFCM). This algorithm can improve loss ratio and jitter on the network. It reserves dedicated bandwidth for different applications with different QoS requirements according to current network status. The key features of this mechanism are shown as follow:

- Provide real time feedback control on bandwidth reservation and management

- Provide level of service according to different QoS requirement

- Predict the traffic on dedicated channel

#### 1.3 Scope of Thesis

Following the introduction chapter, the thesis is organized with the remaining seven chapters as follows.

In chapter 2, a general overview of current Internet Telephony technology is presented. It includes critical design issues of Internet Telephony such as packet delay, packet jitter, packet loss, echo in transmission line and voice coder. A brief description of Real Time Protocol (RTP) and Real Time Control Protocol (RTCP), which is used for real time packet traffic, is detailed. The characteristic of packet voice will be examined using different packet voice models.

In chapter 3, QoS requirement in Internet Telephony is introduced. It defines the

amount of bandwidth that is desired for voice channels as well as what QoS requirements in packet voice communications over Internet. On the other side, different types of architecture and network solution is outlined showing how to provide a realistic solution for real time packet transmission and management.

In chapter 4, the detail of two systematic approaches - Direct Adjustment Algorithm (DAA) and Adaptive Layered Transmission Scheme (ALT) is discussed in detail. As the proposed Feedback Control Mechanism (FCM) is quite similar to the DAA. This provides the basic idea on how to control the flow of packet in such schemes.

A new traffic control mechanism for real time multimedia applications is proposed in chapter 5. This jitter and loss ratio reduction algorithm composes of three models. They are:

- (i) Service model

- (ii) Real time control model

- (iii) Channel model

The objective of the algorithm is to adjust the transmission rate on different channels with according to the specific QoS requirements. A simulation tool, Network Simulators (NS), is used to analyze the Real Time Feedback Control Mechanism (RFCM). The simulation focuses on the bandwidth utilization, packet jitter and loss ratio on real time traffic as well as non-real time traffic. The result is analysis in this chapter.

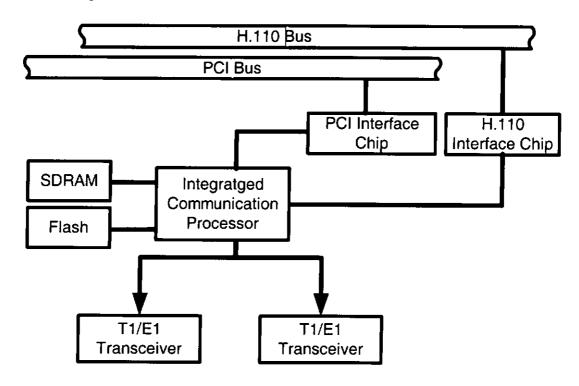

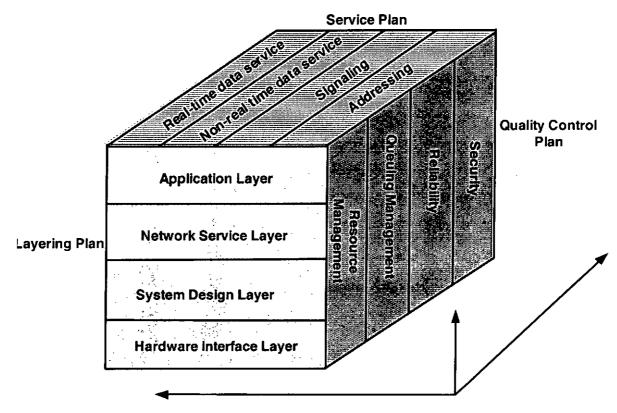

Implementation of real time control scheme in Communications Common Platform (CCP) is discussed in chapter 6. Integration of hardware components including communications processor, Digital Signal Processor (DSP) and line card is presented. The performance of any real time applications will be affected by the designed network equipments as well as the control software implemented on the network equipments. The influence of performance of the Feedback Control Mmechanism (FCM) is mainly due to the packet processing delay, which in term affected by factors such as signaling, channel setup and DSP encode/decodes speed, etc.

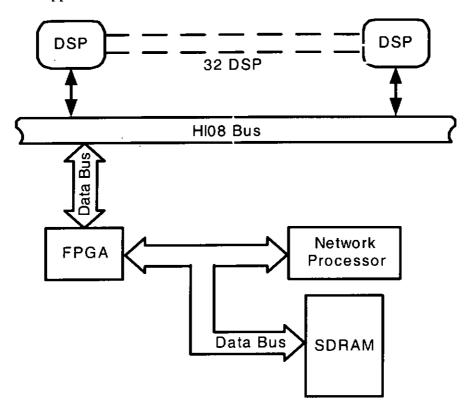

In chapter 7, high density of Digital Signaling Processor (DSP) design under Communications Common Platform (CCP) is presented. There are total 64 DSPs built in Compact PCI 6U form factor with 233.5x160mm through two data hub (design using Field Programmable Gate Array (FPGA)) control. The main task of data hub is to handle Direct Memory Access (DMA) transfer in between the network processor and the DSPs.

Finally, the last chapter concludes the thesis and discusses further work.

#### **CHAPTER 2**

# QoS Control Through Traffic Management

Nowadays, Internet Telephony becomes popular in long distance call because of its lower cost comparing with the traditional Public Switching Telephone Network (PSTN). There are two approaches to analyze voice quality of Internet Telephony. They are:

- 1. Quality of Service (QoS) Traffic control

- 2. Performance requirement in system design consideration.

The first approach in Quality of Service (QoS) traffic control needs to use of theoretical analysis in order to obtain the characteristic of packetized network. The task of theoretical analysis is to model voice packet behaviors. Different types of voice packet model have its constraints and limitations such as Uniform Arrival and Service Model (UAS) which ignores high frequency variations in buffer content as compared to the real system [1] and M/D/1 model assumes to provide large number of voice source. In

previous research [2], most of packet voice model analysis use MMPP as a common and simple model to study packet voice characteristic. On the other hand, network characteristic is another main factor that affect QoS provided by Internet such as packet loss, delay and jitter. These issues cannot be avoided because it is the nature phenomenon in IP network but needed to guard and control through traffic management. For instance, some real time applications have to suffer a number of packet losses in order to satisfy packet delay or jitter constraint. For these reasons, packet voice model and network characteristic have to be studied and then an appropriated scheme for traffic management is applied.

The second approach in real time applications is to analysis network performance requirement in system design consideration. Networking equipments can be separated into three segments, namely the core segment, the edge segment and the access segment. To implement real time service over packet network, specific system architecture design has to be considered within these three types of network segment. The performance of such network equipments affect QoS that the network can be provided such as encoding, signaling and addressing data processing. Unlike traditional PSTN network, VoIP system uses packet switching network to transmit voice signal. Such network can provide other service on top of voice service in between PSTN and Internet. It includes how to receive, process and transfer voice packet to circuit switching network and reverse.

In this chapter and the following chapter, basics introduction on packet voice network is outlined and problems on some outstanding issues are identified.

One major advantage of using packet-switching network for voice transmission is that instead of having a group of engineer and manager to operate a data network and another group to manage a single packet backbone network, a single network management software system can be employed. Furthermore, additional features can be added such as instant messaging, web integration, collaboration, video telephony and fax messaging. However, on the other side, the change of voice transmission from circuit switching to packet switching introduces several issues such as signaling, voice compression and how to interconnect traditional PSTN network to IP network together.

The most important issue in Internet Telephony that must be resolved is the real time consideration. In traditional Internet design, no real time concept is considered but today many applications require a certain real time specification. Real time data means that data transmission from source to destination must be completed within a defined time interval. Otherwise, such data is of no use. In fact, packet switching network is never designed for real time applications. To support real time applications in packet switching network, traffic control mechanism must be incorporated in order to handle such applications. Besides, different services in packet network have their own characteristic in terms of delay, loss ratio, etc. Those types of requirement can be

consolidated as "QoS". In fact, well-defined QoS and its consideration should be studied in detail before designing packet network to perform real time applications.

#### 2.1 QoS Parameter Measurement

There are four outstanding parameters that must be considered in measuring QoS of IP telephony. They are jitter, delay, packet loss ratio and voice compression ratio (voice codec). For these considerations, there is always trade-off when deploying those four QoS parameters. Gaining the improvement in one of these QoS parameters may degrade the other QoS parameters. For instance, either using packet retransmission or using FEC (Forward Error Correction) to recover the error can improve packet loss ratio, but it introduces processing and packetization delay. It should be keep in mind that the aim of traffic control cannot ignore any of those four phenomenon, but it has to guard or reduce such effect to a certain accept level so as to meet individual application's requirement. Before going into system design on packetized voice application in the next section, those four QoS parameters are described in detail.

Another issue arises in packet voice transmission is echo. Different from above four QoS parameters, echo can be overcome or removed by matching its line impedance. Currently, several echo cancellation methods are proposed and implemented to solve the problem. In later section, method on how echo affect packet voice application and how it can be compensated.

#### **2.1.1** Jitter

The occurrence of jitter is due to several factors such as queuing delay, variable packet length, and relative load on the intermediary links and routers. Every voice packet must arrive within a bounded interval to avoid being too late. In the receiver side, the introduction of jitter buffer is one of a commonly used method to compensate jitter effect. This jitter buffer must be carefully tuned to provide an optimal packet-delivery rate while minimizing delay. The real time applications such as voice and video are sensitive to jitter limitations. However, high delay variations introduced to real time applications can lead to high loss to the applications. Obviously, high delay variation requires large buffer size and the receiver design will also be more expensive due to additional memory requirements.

There are more problems while using jitter buffer. Firstly, the buffer requirements may make the design more expensive to implement. Secondly, there might not be a known maximum delay variation on the network, which make size of buffer difficult to determine. Thirdly, the pre-buffer delay may not be acceptable to certain applications. These problems imply that we need to understand a more realistic model of delay variation exceeding the receiver buffer constraints to avoid underflow or overflow.

#### **2.1.2 Delay**

Delay is caused by several reasons such as coding/encoding delay, packetization

delays, propagation delays and jitter compensation delay. It relates to bandwidth reservation when it comes to QoS parameters. If more bandwidth reservation is available for real time applications, it can greatly improve delay through the network. Different types of real time applications may accept different amount of delay. But on the other side, non-real time applications can accept more delay than its real time counterpart. Quite often, packet delay time is unpredictable and it may depend on several factors that generated during transmission. In Internet Telephony application, there are three causes of delay. They are propagation delay, queuing delay and processing delay.

Propagation delay is due to the speed of light in the channel. Such delay is limited by the transportation media and is difficult to minimize. It is measured by the distance between source and destination that the packet has to passing through.

Queuing delay occurs when there are more packets in the network than the system cannot process immediately at a given interval. When dealing with this type of delay, real time and non-real time application should be consider separately since they have different requirements in delay consideration.

Processing delay includes encode/decode (compression) delay, packetization delay and jitter buffer delay. The advantage of voice compression can optimize bandwidth utilization.  $\mu$ -law and A-law are the two basic variations of 64kbps Pulse Code Modulation (PCM) commonly used. A 12 to 13 bit linear PCM quality is

compressed into 8 bits. In order to achieve a higher compression ratio, another two common compression methods are used, they are the "Adaptive Differential Pulse Code Modulation" (ADPCM) and the "Linear Predictive Coding" (LPC). In general, increasing compression ratio also increases the processing time. In some system, they have to accumulate certain number of packet and then process it to prevent the jitter effect. The system used this method to prevent jitter effect will introduce jitter buffer delay because it has wait for a number of packet to arrive before start processing. Besides, during packet transmission, packetization is to add an appropriate header together with payload according to different protocol specification. The process includes data segmentation, checksum and packet length calculation. All this process consumes time, hence introduce more delay.

#### 2.1.3 Packet Loss

There are two reasons that cause packet loss in multimedia applications - occurrence of noise during transmission and excessive delay time. It is also impossible to re-transmit lost packet in real time applications.

Internet do not guaranteed packet delay because it only uses "best afford" transmission methodology, but on the other side, due to the stringent delay requirements on real time interactive applications, reliable transportation protocols, such as TCP, is not suitable to be used. It seems that packet loss is unavoidable, but it can be compensated by

several error detection and error correction methods such as the Forward Error Correction (FEC). In fact, packet loss control is a two-step processes. The first step is error detection and the second step is error recovery. Packet retransmission is one of error recovery method but it is not suitable for real time applications.

The most popular method to recover packet loss in real time communications is the forward error correction (FEC). This scheme has been proposed to alleviate loss busts of a small number of packets. However, the drawback of FEC-based loss recovery is that in order to recover packet n, we need to receive packet n+1 successfully. Thus, it will be subjected to at least one extra frame delay in addition to the processing delay of the FEC encoding and decoding. This additional delay may cause the recovered packet to arrive too late so that it is lost its usefulness anyway.

Another common method to recover the loss packet is adding copies of the previous k frames in the packet containing frame n. Like the FEC schemes, it is the most effective scenario in which a large receiver buffer is needed for several frames storage.

The other approach is to build redundancy into the speech coder itself. In this way, algorithms can be designed for each specific coder to recover from such loss but this method is less practical. Speech coders are applied to many different environments such as Internet, Asynchronous Transfer Mode (ATM) and wireless network. The codecs must therefore designed to meet general requirements for loss recovery, which are bother inter

and intra operative among these different mediums. However, this end up with a non-optimal codec for any single media. Moreover, loss behavior varies with time, which makes no sense if the behavior cannot be adequately characterized.

Another approach is diversity, which sends multiple copies of the same thing over several paths, and hope that at least one gets there. This approach is very inefficient and generally considered being a very poor method in the Internet environment.

Delay and losses are two main parameters affecting QoS control. For Internet Telephony application normal conversion, users accept a delay of 200ms or less while more tolerant users satisfies with the delay of 300-800ms[3]. Users also require a clear speech coming out from the speaker. There are trade-offs between these two parameters such that it can sati factorize defined in the QoS requirements.

#### 2.1.4 Voice Coder (Voice Compression)

There are two main purposes to do voice coding – digitization and compression. Digitization is the conversion of analog signal into digital signal. Compression is performed in the transmit side to reduce the bandwidth utilization without degrading the voice quality. Currently, the most popular voice coding protocol is the G.711, the G.729 and the G.723.1.

The G.711 is as 64kbps Pulse Code Modulation (PCM) including both A-law and  $\mu$ -law. It does not involve another kind of voice compression.

The G.729 is a 8-kbps Conjugate Structure Algebraic Code Excited Linear Prediction (CSACELP) speech algorithm providing good speech quality. It is designed for low-delay applications, with a frame size of only 10ms, a processing delay of 10ms and a lookahead of 5ms. This total to a 25-ms contribution [4] to end-to-end delay.

The G723.1 is a 6.3- kbps/5.3-kbps vocoder for multimedia communications that was originally designed for low-bit-rate videophones. The system encodes the voice signal into frames based on Linear Prediction Analysis by Synthesis (LPAS) coding. A coder is capable of producing two rates of voice traffic

- a. 6.3kbps for the high-rate

- b. 5.3kbps for the low-rate

The high-rate coder is based on Multipulse Maximum Likelihood Quantization (MP-MLQ), and the low-rate coder is based on Algebraic-Code-Excited Linear Prediction (ACELP).

#### 2.1.5 Echo

Echo is the signal reflections of the speaker's voice from the far end telephone equipment back into the speaker's ear. There are two types of echo to impact packet voice network. The first one is the usual far-end echo caused by the four-wire to two-wire hybrid conversion. End users will hear their own voice signal bouncing off the remote central office's line-card hybrid. The second form of echo occurs when a free-air

microphone and speakers are used, as is the case for most PC endpoints. The remote user's voice signal produced by the speakers is picked up by the microphone and echoed back to the remote user. The microphone may receive the PC speaker signal from multiple paths. Echo becomes a significant problem when the round trip delay is greater than 50 milliseconds. Packet voice must address the need for echo control and implement some means of echo cancellation.

#### 2.2 Real Time Protocol Design

Real Time Protocol (RTP) and Real Time Control Protocol (RTCP)[5] are commonly used for real time packet transmission. The purpose of these protocols allows receivers to generate report and such report can be used by applied algorithms in transmitter to compensate jitter and consequence introduced by packet network. RTP is used for real time data transmission and RTCP is the companion control protocol for RTP.

#### **Real Time Protocol (RTP)**

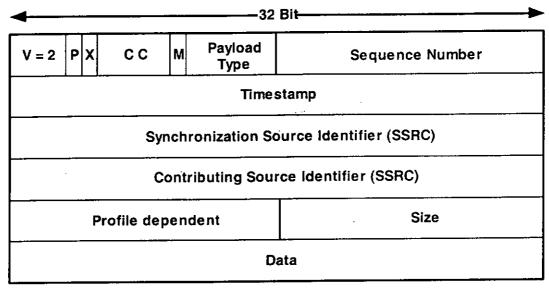

It is typically used on the top of UDP, which provides the notion of port and checksum. Figure 2-1 shows the packet format of RTP. Below is some useful fields description of RTP header:

Sequence Number - It is used to number each RTP packet. At the receiver, the sequence number is used to reconstruct the whole message due to different arrival rate of packet

- Timestamp It can be used to count the time taken for each RTP packet from source to destination in order to maintain the time information

- Payload type It identifies the type of message in the RTP stack. It can be used to classify the level of QoS that should be provided during transmission

- SSRC It identifies the source of RTP stream. All RTP packets within a common

SSRC have a common time and sequencing reference.

#### Real Time Control Protocol (RTCP)

RTCP is used to control packets transmission from time to time regarding a particular RTP session. Basically, RTCP packet types include Sender Report (SR), Receiver Report (RR), source description RTCP packet (SDES), BYE and APP. Below is the description of each reports:

- SR: Sender reports contain transmission and reception information for active senders

- RR: Receiver reports contain reception information for listeners who are not also active senders

- SDES: Source descriptions describe various parameters about the source, including the CNAME

- BYE: Send by a participant when he leaves the conference

- APP: Functions specific to an application

Through these control messages report, network operator can provide appropriate traffic management mechanism base on the result of that reports.

Figure 2-1 RTP Protocol Stack

#### 2.3 Common Voice Model Analysis

In 70s' and 80s', most of the research and analysis on packet voice modeling had started. Some outstanding models are given out in this period [6-9]. Most of research is focused on the voice packet model, queuing management on voice packet network analysis and studying voice packet delay and loss characteristic.

In early state, voice can be modeled as the on-off source model [10]. In talk spurt period, ones are speaking and the source is in 'ON' or active state. At this time, the source generates voice data. In the silence period, the source is in 'OFF' or inactive state and no voice data are produced. In normal conversation, the duration of active period fits the exponential distribution reasonably well while the duration of inactive period is

approximated less well by the exponential distribution.

In packet voice communications, voice is modeled as the embedded Markov chain which queue length is modeled as the "overload/underload" cycle based on the phase process [6]. Then the further development on the packet voice queue model is modeled as the bivariate Markov chain embedded at instants of phase state changes, queue increments, and queue decrements. Following is the mutual and common used for packet voice models.

#### 2.3.1 On-Off Source Model

In this voice model, voice conversation is divided into six states according to Brady 's[10] description. It assumed that voice source is based on Poisson distribution. It defined the voice conservation into 'solitary', 'interrupted', 'interruptor', 'pause', and 'alternate' and 'interrupt'. During change of the state, one of the signals is given out to fall into next state.

#### 2.3.2 Semi-Markov Process Model (SMP)

The voice source of this model is assumed to be an alternating renewal process. It means that active and inactive period is exponentially distributed. These approximations adopted for this model ignore the "high frequency" fluctuations present in the system being modeled. The second implication of the approximations is that a renewal occurs at

the instants of phase transition. That is, no fractional queue length growth is accrued to account for packets that are in the process of arriving between the time of the latest queue length change prior to a given phase transition and the time of the phase transition.

From the renewal theory,  $p_{i,j} = \lim_{t \to \infty} P\{l(t) = i, \wp(t) = j\}$  where l(t) is the number of packets in the queue at time t and  $\wp(t)$  is the number of active sources at time t. So, probability of the queue length:

$$\pi_i = P\{l = i\} = \sum_{j=0}^{N} p_{i,j}$$

(2-1)

where  $p_{i,j} = \frac{q_{i,j} m_{i,j}}{\sum_{k=0}^{\infty} \sum_{l=0}^{N} q_{k,l} m_{k,l}}$  is obtained by from the renewal theory.

$q_{i,j}$  is the equilibrium probabilities for the embedded Markov chain,  $m_{i,j}$  is the expected sojourn time in state (i,j) of the process, N is the total number of active source

### 2.3.3 Continuous-Time Markov Chain Model (CTMC)

This model assumed the generation of packets of the active voice is a Poisson Process. The generation of packets by an active voice source occurs according to a Poisson process with rate  $\beta$  rather than at a constant rate of one packet every 1/Vs as in the system being modeled. Also, the service times are exponentially distributed with parameter  $\upsilon$ .

In both real system and CTMC model, the average rate of growth in system occupancy is zero, but the length of time required to observe this zero average growth

rate would be quite different. The CTMC model experiences higher frequency fluctuations in system occupancy than does the real system. It is then expected that the CTMC model would yield conservative estimates for probability of buffer overflow and waiting time. That is, if the system were engineered to achieve a certain probability of overflow based on the CTMC model, then the probability of overflow in the system would probably be less than that predicted by the model.

Probability of the queue length is:

$$\pi_i = P\{l = i\} = P\{s = i+1\} = \sum_{j=0}^{N} p_{i+1,j}$$

(2-2)

where  $p_i = [p_{i,0}, p_{i,1}, ...., p_{i,N}]$

N is the number of active sources, s is the number of packets in the system and i is the queue length.

### 2.3.4 Uniform Arrival and Service Model (UAS)

The active voice source is generated in the buffer at a uniform rate and the buffer removes the packet at a rate not to exceed the link capacity. The approximation of this model is to ignore "high frequency" variations in buffer content as it compares to the real system. That is, in the real system, information does not enter the transmission buffer, and therefore it cannot be transmitted, until a particular active source completes the generation of a packet. In the UAS model, it is possible for the information to be transmitted while it is being received. It would appear that the effect of this

approximation on the UAS model's accuracy would be slight since the difference between the behavior of this model and that of the real system is greatest only when the buffer content is low and the number of active sources is below the server's capacity.

Define the complementary queue length distribution for this system, P(l>i), to be probability that the buffer occupancy exceeds  $(\alpha/V)i$  units of information. Then, the complementary queue length distribution is:

$$P\{l > i\} \equiv G(\frac{\alpha}{V}i) \tag{2-3}$$

where V = packet generating rate,  $\alpha$  is the frequency of the active period and G(x) is the complementary occupancy distribution.

A thorough discussion of the details of the implementation of the solution is given in [11].

It shows that SMP and UAS models are reasonable for the engineering purposes.

It can use to predict the buffer capacity needed to ensure that the fraction of packets lost due to buffer overflow is less than some maximum value.

### 2.3.5 Markov Modulated Poisson Process Model (MMPP)

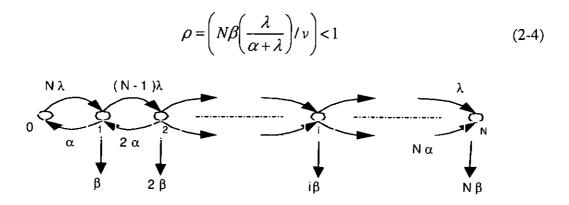

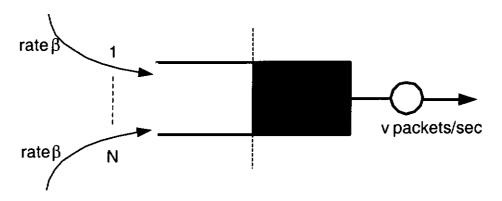

This is the most common model to simulate voice packet queue. Since the RFCM assumes such model as the voice packet source, the explanation on this model will be given.

This model is defined to be one having n states in general, with the process, while

in any state i, 1 < i < n, behaving as a Poisson Process with a state-dependent rate parameter  $\lambda$ . Transitions between states are governed by an underlying continuous-time Markov chain. In packet voice modeling, MMPP is used to analysis the characterization, modeling, and analysis of N voice sources multiplexed at the buffer.

Figure 2-2 shows the MMPP model for N multiplexed voice source with infinite buffer.  $\lambda$  represents the rate of transition from the silent state to talk spurt, and  $\alpha$  be the rate in the reverse direction. Also, a utilization parameter  $\rho$ , the condition of capacity  $\nu$  and Poisson average arrival rate  $\beta$  is defined. In Figure 2-3, it is easy to find out that the average number of cells per second entering the queue is  $N\beta/(\lambda/\alpha + \lambda)$ . This must be less than the capacity  $\nu$ , so that:

Figure 2-2 MMPP Model, N Multiplexed Voice Sources

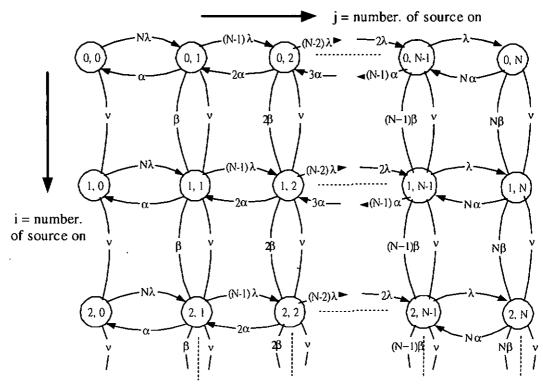

Now, the probability distribution of buffer occupancy can be found. Let the integer value i > 0 represents the queue state; j represents the number of sources in talk spurt. Also,  $p_{ij}$  is defined as the joint probability that the queue length is i with j sources

on  $p_{ij} = P[\text{queue length} = i, j \text{ source on}]$

Figure 2-3 Statistical Multiplexer for Input Model

Figure 2-4 Two-dimensional State Space

Figure 2-4 shows the two-dimensional state space for  $p_{ij}$ . Three two-dimensional balance equations for this state space.

$$p_{00} = (1 - N\lambda)p_{00} + \alpha p_{01} + \nu p_{10}$$

(2-5)

$$p_{0j} = [N - (j-1)]\lambda p_{0j-1} + [1 - (N-j)\lambda - j\alpha - j\beta]p_{0j+1} + \nu p_{1j}$$

(2-6)

$$p_{0N} = \lambda p_{0N-1} + [1 - N\alpha - N\beta] p_{0N} + \nu p_{1N}$$

(2-7)

Then, the equivalent compact matrix vector equation can be written as:

$$P_i = P_a B_a + P_1 B_1 (2-8)$$

$$B_{0} = \begin{bmatrix} 1 - N\lambda & N\lambda & 0 & \dots & 0 \\ \alpha & [1 - \alpha - (N - 1)\lambda - \beta] & (N - 1)\lambda & \dots & 0 \\ 0 & 2\alpha & [1 - 2\alpha - (N - 2)\lambda - 2\beta] & \dots & 0 \\ 0 & 0 & 3\alpha & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \dots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \dots & \dots & \lambda \\ 0 & 0 & \dots & \dots & \dots & \lambda \end{bmatrix}$$

(2-9)

$$B_1 = diag[v, v, \dots v] \tag{2-10}$$

$$P_{i} = [P_{i,0}, P_{i,1}, P_{i,2}, \dots, P_{i,N}]$$

(2-11)

$P_i$  is a set of (N+1)-element row vector.

From above calculation, it shows that the characteristic of voice source depend on several factor - number of source, buffer length, arrival rate of each source and service rate on each server.

To determine the voice characteristic and the convergence of queue length of the integrated data/voice in separated queue for today's packet switch network, such model should be studied so as to adjust the service rate on servers and define the queue length of voice source in feedback control mechanism and can be enhanced to provide traffic prediction in further analysis.

### **CHAPTER 3**

# System Consideration and Performance Requirement

In previous chapters, a numbers of QoS measurement parameters and theoretical description on packet voice are introduced. The characteristic of packet voice can be known through this model. On the other side, network products design technology and implementation algorithm must be in consideration because it affects actual overall performance of whole networking system. Nowadays, the complexity of system networking design requires system level point of view to analysis the network. Highly integrated networking design can provide high efficient and also can fully utilize network resource. Also, the challenge on packet switching network and traditional circuit switching network is on how to interconnect PSTN (circuit switching) and Internet (packet switching) together to provide multimedia application including voice, video and data. For this reason, signaling, addressing and routing technique need to be enhanced such that it provides highly efficient bandwidth utilization and traffic management.

Before designing packet voice network, specifying QoS requirement of performance is needed such that system performance can be measured based on those QoS performance requirements. In this section, it mentions what requirement is needed in packet voice network service, how to defined desired voice quality and how to measure performance. The last topic of this chapter will provide some information about the system architecture on the most common used packet voice networking equipment.

### 3.1 Performance Requirement for Internet Telephony

Comparing with PSTN, packet voice transmission has to share its bandwidth with other users. In social point of view, the fundamental performance requirement is that the end user can listen voice clearly and they can communicate with each other smoothly. But this requirement is not enough to satisfy our desire and it is not acceptable from technology point of view. In fact, the purpose of using packet voice communications is to reduce bandwidth utilization to deliver higher quality of voice. In other word, it has to use the lowest cost to get high quality of voice communications service. In fact, it has some conflict on resource and quality requirement. There are some questions are raised in performance requirement definition.

### 3.1.1 How Much Bandwidth Should be Assigned for One Channel

Bandwidth can be defined as a number of bits per second that is available on network. It is a main variable resource in network communications. For those

applications, it needs to determine how much bandwidth it desires to provide the appropriate QoS. But on the other hand, bandwidth is a limited resource. The main concern in packet voice application is on how to share limited bandwidth to one or more voice channels. In traditional circuit switching network, the data transmission rate for each voice channel is 64kbps. If the rate is used in packet switching network, the bandwidth utilization in term of channel is very high and inefficient. In fact, there is not need to transmit voice signal at silence period. The first thing need to do is to reduce unnecessary bandwidth consumption for each channel. Two common methodologies are adopted to reduce bandwidth utilization for voice channels - silence detection and voice compression. In silence detector, most of systems are equipped with Speed Activity Detectors (SAD) at each user node such that packets are only generated while users are in a talkspurt period. Since the typical mean duration of the talkspurt and silence period is about the same [10], SAD can potentially double channel utilization. Also, voice compression is another types of method to minimize voice traffic. By applying voice compression, bandwidth utilization can be reduced from 64kbps to lower data rate depending on the applied algorithm. Different compression algorithms can provide different compression ratio. Since bandwidth utilization for each voice channel is based on compressed ratio, one has to choose appreciate voice compression algorithm to give desired OoS.

Currently, the most popular methods for voice compression is G.723.1, G.729 and G.729A. Table 3-1 shows some figures on different types of codec. G.729 and G.729A with the smallest frame size allowing low-latency encoding but a significant overhead are added if only one frame is encapsulated in as RTP packet. This implies that G.723.1 would be favorable to home PC users, who must share what little bandwidth they have with data traffic. Corporate users with direct access to Ethernet or T1 media may refer to G.729A for its favorable delay characteristics.

| CODEC            | G.723        | G.729   | G.729A  |

|------------------|--------------|---------|---------|

| Bit rate         | 5.3/6.4 kb/s | 8 kb/s  | 8 kb/s  |

| Frame Size       | 30ms         | 10ms    | 10ms    |

| Processing Delay | 30ms         | 10ms    | 10ms    |

| Lookahead delay  | 7.5ms        | 5ms     | 5ms     |

| Frame Length     | 20/24 bytes  | 10bytes | 10bytes |

**Table 3-1 Codec Bit Rates, Delays**

### 3.1.2 How to Define Desired Quality

There are three main factors that affect voice quality - loss (transmission error), delay and jitter (delay variance).

The statistical measurement and analysis carried out by Guy Almes[12] and Sanghi et. al., [13] showing that the losses in the current Internet are in the range of 2%-10%. Losses have a direct correlation with delay.

Also, experiments conducted at Bellcoe show that the busy hour average packet

loss rate on random cross- Internet connections can be as high as 16%. In busy hour, the round trip delay between well-connected sites varies within 100 to 300ms

The above statistical factors reflect the general characteristics of the current Internet.

On the other side, there are some expected performance requirements [14] for Internet Telephony. Telephony applications can be described as relatively tolerant to a small amount of packet losses (about 1% to 2%), but it depends on a small network delay.

For end to end delay, lower than 100 or may be 150 ms is generally deemed compatible. If end-to-end delay is between 150 and 350 ms, it is generally considered mediocre. On the other hand, it is not acceptable if end-to-end delay is larger than 350ms. The delay factor included coding and packetization delays, network transmission delays, jitter compensation delay, decoding and play out delay.

### 3.1.3 How to Measure Performance

In [15], it encloses some approach to measure network performance such as service/transmission approach, call-phase approach, ad hoc approach and combinational approach.

In call-phase approach, it considers each call with three phases - access phase, information exchange phase and disengagement phase. By dividing the call period into separate phases, this approach attains completeness in the criteria as well as network

independence from user's viewpoint.

In service/transmission phase, it considers the offer and the actual transmission quality. It associated with the supply, support, and the operation of the service which are separated from the quality of the actual received information. It considers under the functions required at the particular time.

In Ad Hoc approach, it is similar to the call-phase approach but it concern on the non-technical user. In user point of view, they do not concern all the technical knowledge to so how to do that. So the difficult is the satisfaction of user desired.

In Combinational approach, it combined all the above three approaches. The problem of this approach is that the number of criteria may increase significantly, the combining or cross listing gives the resulting criteria less generality, and the criteria may still not encompass all user concerns.

### 3.2 Architecture and Network Solution on IP Phone

Nowadays, several types of network architectures are interconnecting together to provide data communications service. Some of them are standardized but some of them are not. Providing real time data transmission in packet switching network is one of difficult task to achieve. When designing a high efficiency network, it has to forecast its maximum channel utilization and loading. Besides, scalability is one of main factor to increase the functionality and the processing power. Moreover, the system has to

interconnected network equipments have to provide the services including to convert packet header format, signaling and handshaking. As a result, traffic management must be considered and implemented in order to manage data transmission and monitor network performance. In fact, processing power of board design and system architecture determines the overall system performance and limited its functionality. In general, when considering real time network design, some factors should be noticed:

- a . Connectivity It is an important factor when determining how to design stable network in order to support a number of terminal or connection in real time network. Intranet estimation of network connection is easier than Internet. Most of network designs are limited by number of port and addressing scheme.

- b. Channel capacity the maximum bandwidth of each path should be known in between source and destination. In general, network is divided into Wide Area Network (WAN), Local Area Network (LAN) and Metropolitan Area Network (MAN). Most likely, WAN is a backbone of the network; it needs high channel capacity because it has to provide high speed of traffic and support huge amount of data transmission. LAN is a small network with a small group of user such as a small company up to 30 people. So bandwidth is not too high but it is important to interconnect with different LANs and enter into WAN. The MAN is the

intermediate between LAN and WAN. The covered area may be within a building or a country. To determine channel capacity, maximum loading of the channel should be well known. It is just like a water pipe in our life.

- c. Supporting protocol Different types of protocols has their own network design topology. For instance, Ethernet can support more than 500m in a segment. For Internet, it uses gateways and routers to separate the subnet. protocol design restricts network topology design and limit the overall network performance. Also, WAN and LAN has own specific protocols to support different traffic rate. On the other side, routing algorithms are another types of protocol used to determine the path of packet. Intelligence routing can be used for load balancing to against overloading in real time applications.

- d. Service integration There are a number of service that the network has to provide.

It can classify into two different categories real time and non-real time. Real time applications are time critical data that cannot tolerate much delay but it can accept certain amount of loss ratio. The requirement of these types of service is highly depend on the demand of bandwidth. But, on the other hand, most of non-real time applications have to reliable data transmission. It can tolerate much of delay but the error rate must be kept much low. Packet re-transmission is one of the most popular methods to compensate packet loss. A systematic design of

network and proper traffic management mechanism is needed to integrate such types of data.

### 3.3 Gateway Architecture on VoIP

Gateway, router and switch are three major networking equipments in the Internet. They have their own functionality and definition. In order to handle packet voice traffic, additional functions are needed in these types of equipments such as voice compression, protocol conversion. The architecture of such network equipments directly affects network performance, functionality and quality. Currently, a number of network architecture solutions are provided. Here shown a common used architecture of packet voice transmission system solution in both server side and client/terminal side.

### 3.3.1 Common Packet Voice Gateway Solution on Server Side

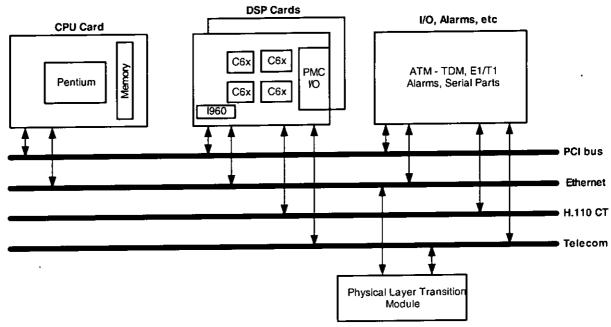

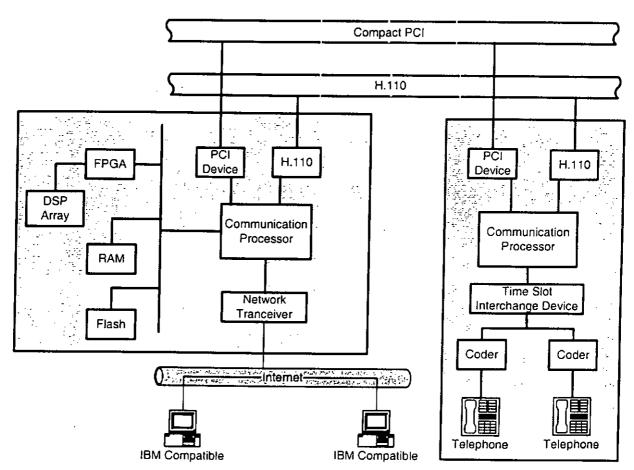

Figure 3-1 shows a common used system architecture for multimedia communications in server side. The system controller in this architecture is a processor based on embedded computer, capable of hosting a real time operating system such as PSOS and VxWork. The combination of hardware and operation system is open, powerful and easily able to host applications available in the desktop computing world.

The gateway design based on Compact PCI architecture. Besides the main PCI bus, the system has the H.100 bus for Time Division Multiplexing (TDM) traffic. This bus is capable of carrying a number of PCM channels. Also, the other bus hosts the

non-bused I/O for E1/T1, etc. Besides, another bus is meant for user I/O and Ethernet can be routed on this.

The DSP boards are Compact PCI boards based on several DSP processors and also have a PCI bridge and for hosting networking protocol. The boards have PCI Mezzanine Connector slots on the secondary PCI bus which can host daughter cards for E1/T1, Ethernet or ATM I/O processing. In addition to the PCI bus, these connectors also have connectivity with the TDM bus and Telecom I/O.

Figure 3-1 Server Side Solution for Voice over IP Gateway

### 3.3.2 Common Packet Voice Solution on Client/Terminal Side

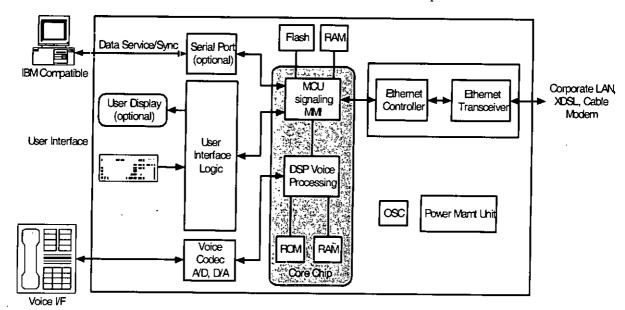

Figure 3-2 shows a block diagram of a reference design of an IP telephone. It divided into hardware and software design. In hardware design, it consists of the following components

- 1. User Interface It provides the traditional user interface functions of a telephone

- 2. Voice Interface It provides the conversion of analog voice into digital samples.

Speech signals from the microphone are sampled at a rate of 8kHz to create a digitized 64kbps data stream to the processor via a pulse code modulation.

- Network Interface It allows transmission and reception of voice data packets from/to the telephone.

- 4. Processor Core It performs voice processing, call processing, protocol processing, and network management software functions of the telephone

Figure 3-2 IP Telephony Reference Design on Client Side

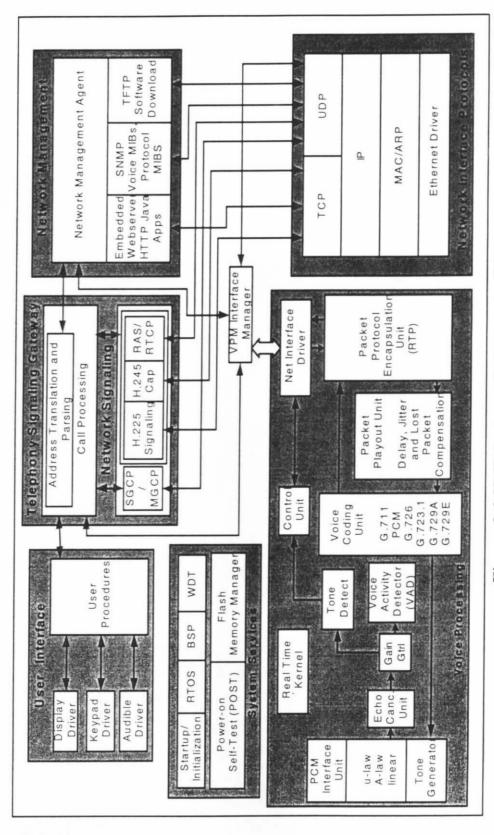

Besides the reference design for IP telephony, it concerns on the software architecture on IP telephony including system service, signaling gateway, network management, voice processing and network interface protocol. Figure 3-3 shows how these modules are interactive with each other and their functions.

Figure 3-3 IP Telephone Software Architecture

- 1. User Interface It provides the software components that handles the interface to the user of the IP telephone and consists of display driver, keypad driver, audible driver and user procedure. User procedures control the information displayed by the display driver and process user key inputs and converts them into primitives for call processing.

- Voice Processing It consists of PCM interface unit, tone generator, line echo canceller unit, acoustic echo canceller, Voice Activity Detector (VAD), voice codec unit, packet playout unit, packet protocol encapsulation unit, voice encryption and control unit. These entire modules are used to control and perform voice-processing function. The main function of these modules is to perform voice compression and echo cancellation.

- Telephony Signaling Gateway It contains call processing, address translation and parsing, network signaling and H.323 protocols. Most of these functions are to establish, maintain and terminate a call.

- 4. Network Management It supports remote administration of the IP telephony by a network management system. It consists network management agent, embedded web server, Simple Network Management Protocol (SNMP) and Trivial File Transport Protocol (TFTP).

- Network Interface Protocol It supports communications over the LAN and the module consists of TCP, UDP, IP, Media Access Control (MAC), and Ethernet Driver.

- 6. System Service It consists of startup, Power-On Self-Test (POST), Real Time Operating System (RTOS), Board Support Package (BSP), watchdog timer driver, flash memory manager and DSP interface manager. Most of these functions are directly interactive with hardware. It isolates the hardware and upper layer function. Though this function, upper layer function becomes hardware independent.

### **CHAPTER 4**

## Deficiencies on

### Current Method

Nowadays, there are so many algorithms to provide traffic management in order to support different types of multimedia applications in packet switching network. Such algorithms have their pros and cons. But, in general, most of them cannot provide systematic and realistic approach to handle real time packet transmission. In this chapter, two realistic and systematic approaches are studied to handle real time traffic - Direct Adjustment Algorithm (DAA) and Adaptive Transmission Scheme (ALT).

### 4.1 Direct Adjustment Algorithm (DAA)

### 4.1.1 Theoretical Description

The direct adjustment algorithm is based on both additive increase and multiplicative decrease approach as well as directly using the bandwidth to share a TCP connection under the same round trip delay, packet size and loss ratio. This scheme

achieves high bandwidth utilization, low loss and a fair distribution of the available bandwidth among connections with the same round trip times, but it is unfair with longer round trip times.

During a RTP session, each receiver reports the percentage of lost data to its control packets since sending the last control packet. At the sender site, the RTCP packets are processed depending on the loss values reported within the RTCP packets, the sender can increase or decrease its sending rate. With the reception of each RTCP packet the sender needs to do the following:

1. Calculate the round trip delay to the reporting receiver and determine the propagation delay. The RTCP receiver report includes the timestamp of the last received report from this sender and the time elapsed since receiving this report and sending the corresponding receiver report. Knowing the arrival time T of the RTCP packet, the end system can calculate the round trip time (RTT).

$$RTT_i = T - DLSR - LSR \tag{4-1}$$

where LSR is last received report from sender and DLSR is the processing time between the receiving the sender report and sending the corresponding receiver report.

2. In the RTCP receiver report, it contains the value of the average packet loss measured for the sender in the time between sending two consecutive RTCP

packets at the reporting receiver. To avoid reactions to sudden loss peaks in the network, the sender maintains a smoothed loss ratio  $L_s$  for each receiver.

$$L_{c} = (1 - \alpha)L_{c} + \alpha L \tag{4-2}$$

with L as the loss value reported by RTCP packet and  $\alpha$  as a smoothing factor.

Using the smoothed loss ratio and round trip delay, the sender can calculate the maximum bandwidth R<sub>TCP</sub> share by using [16] and [17]

$$R_{TCP} = \frac{1.22xMTU}{RTTx\sqrt{L_s}} \tag{4-3}$$

with MTU as the maximum packet length

4. If the smoothed loss ratio smaller then 16% (simulations run in [16] show that it only applies up to loss ratio of 16%), the sender sets its transmission ratio to  $(\min[R_m, R_A])$  with

$$R_{A} = R + \frac{AIF}{m} \tag{4-4}$$

with AIF as the additive increase factor, R as the current transmission rate and m is set to (min[members, h]). The number of members in a session can be determined using the RTCP packets and the scaling threshold (h) can be calculated as

$$h = \frac{\min. \text{Interval x B}_{R}}{\text{RTCP Packet Size}}$$

(4-5)

with  $B_R$  as the bandwidth dedicated for RTCP and is set to 5% of the bandwidth used by the session.  $R_m$  is the minimal  $R_{TCP}$  calculated for all receivers.

5. With smoothed loss ratio greater than 16%, the sending ratio is reduced by half.

For the reduction to take effect, all RTCP packets are ignored for five seconds, which is approximately the minimum interval between the sending of two consecutive RTCP packets or until another RTCP packet from the receiver, who reported the loss is received.

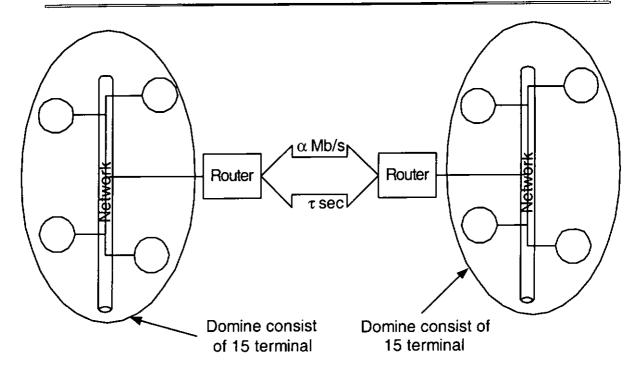

### 4.1.2 Performance Measurement on Direct Adjustment Algorithm

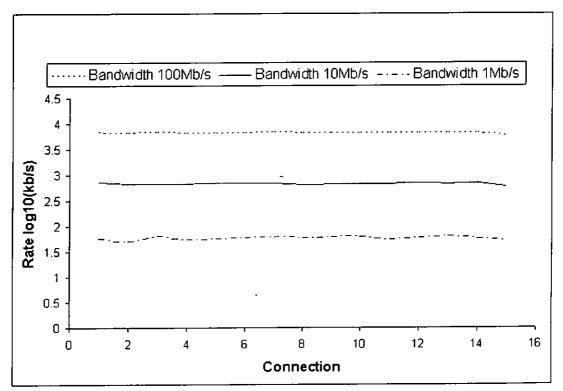

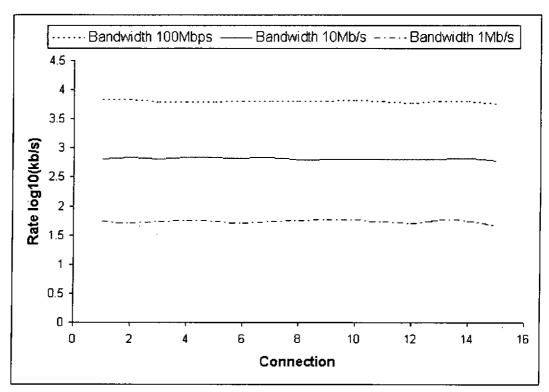

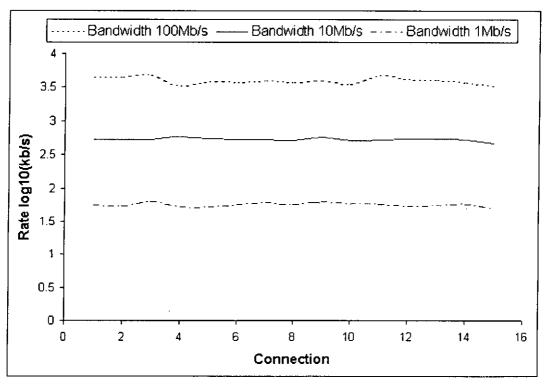

The topology in Figure 4-1 is setup to measure the performance of the Direct Adjustment Algorithm (DAA). The model consists of 15 connections sharing a bottleneck router. All connections deploy the direct adjustment algorithm and are persistent sources. That is, they always have data to send with the maximum allowed rate. They all have the same round trip times and are similar in their requirements and characteristics. The router contains 200kbytes of buffer size. In all simulations, it has to set the packet size to 1kbyte, which is typical voice packet size. Table 4-1 shows the average utilization results achieved for different round trip times and different link bandwidth. The results shown in Table 4-1 and Figure 4-2 reveal that using direct adjustment algorithm, bandwidth utilization between 60% and 99% is possible and the bandwidth is equally distributed among all connections sharing the same link. Also, while connection 15 starts 100 seconds later than the other connections it soon reaches the same bandwidth level.

Figure 4-1 Direct Adjustment Algorithm Performance Testing Topology

Figure 4-2a Rate of Single Connection of DAA under 5µ Second Round Trip Times and Link Bandwidth

Figure 4-2b Rate of Single Connection of DAA under 5m Second Round Trip Times and Link Bandwidth

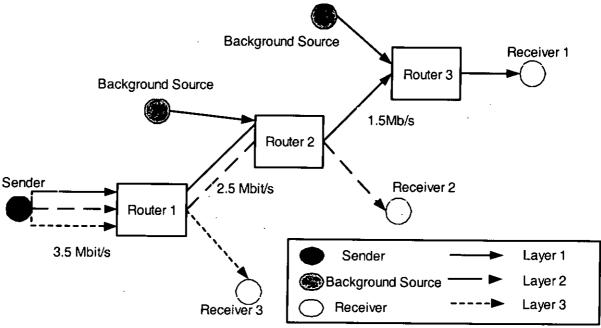

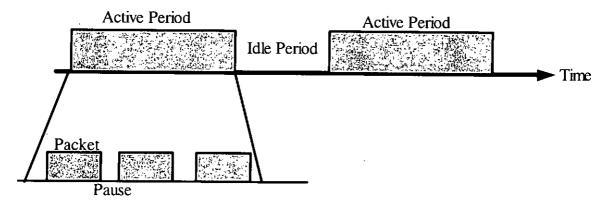

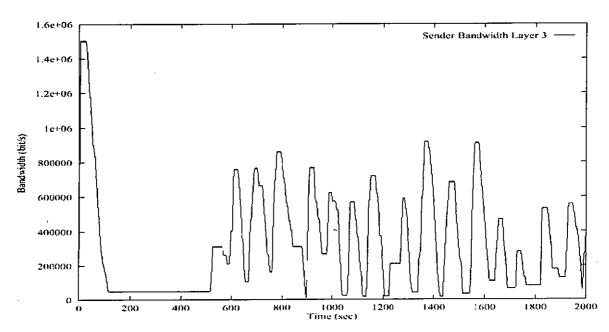

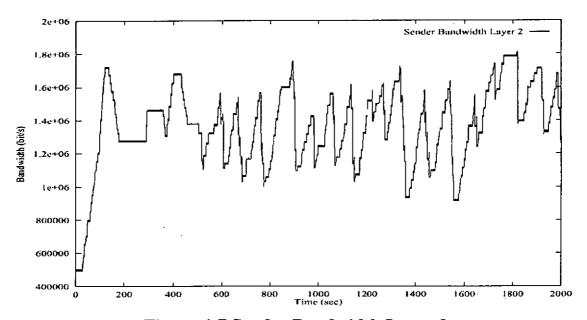

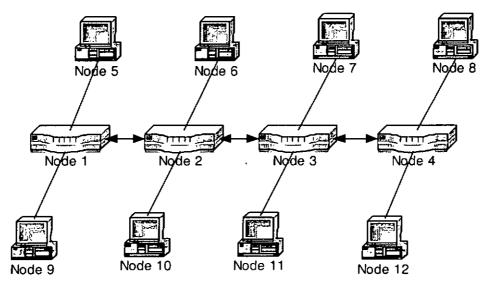

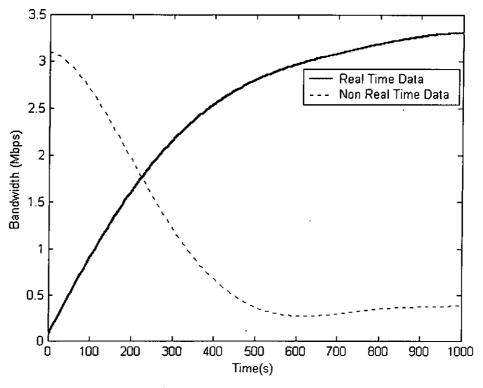

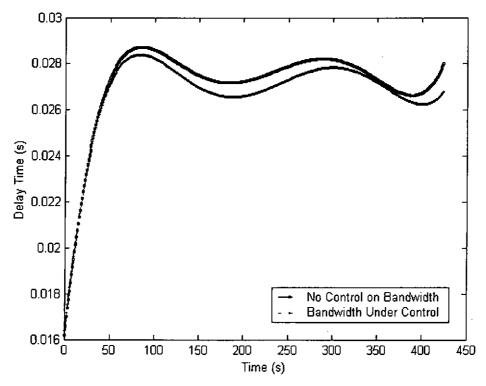

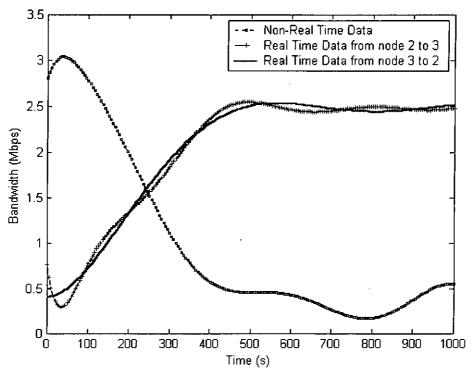

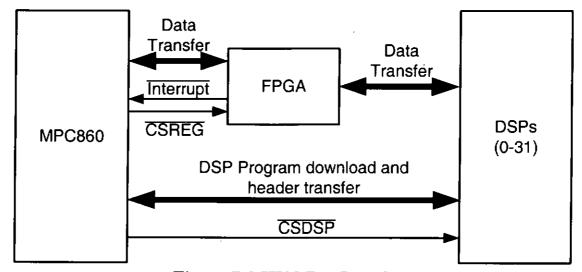

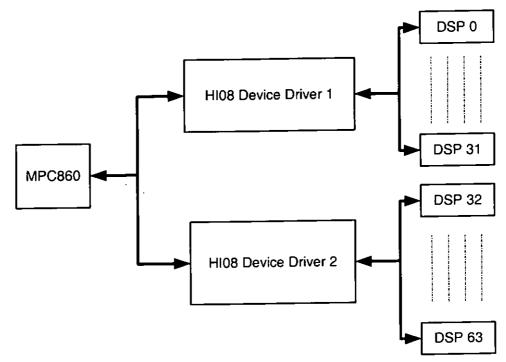

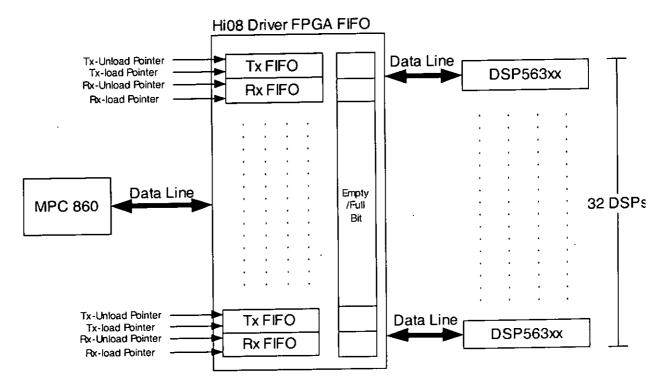

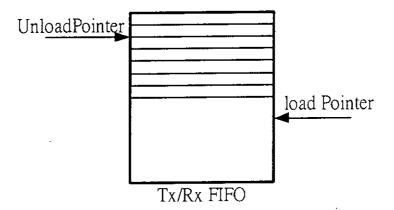

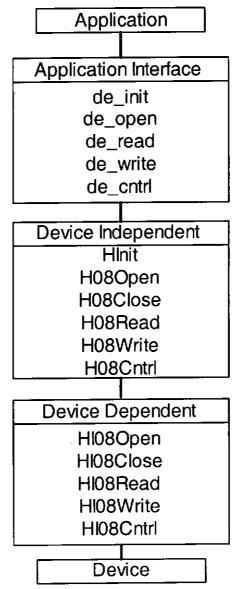

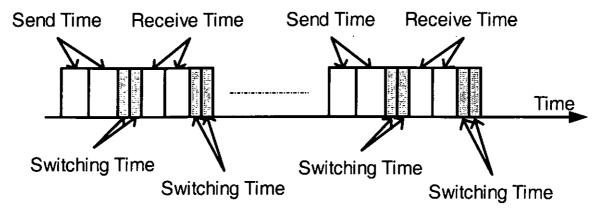

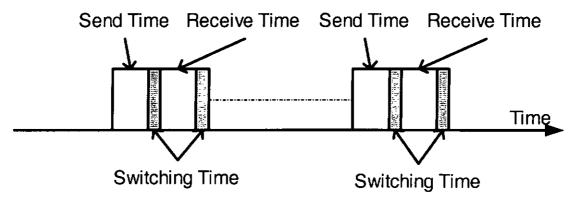

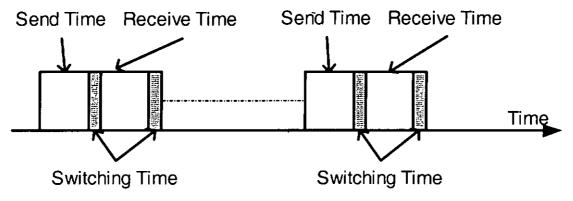

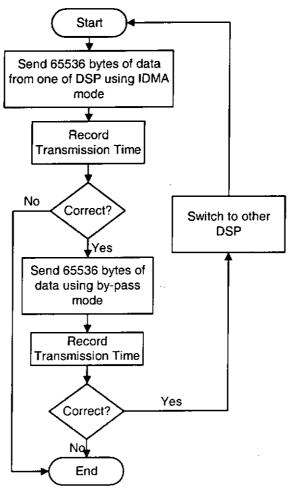

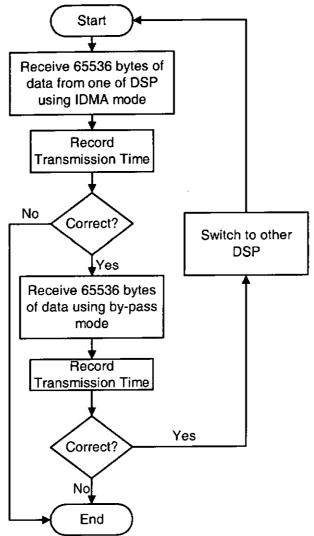

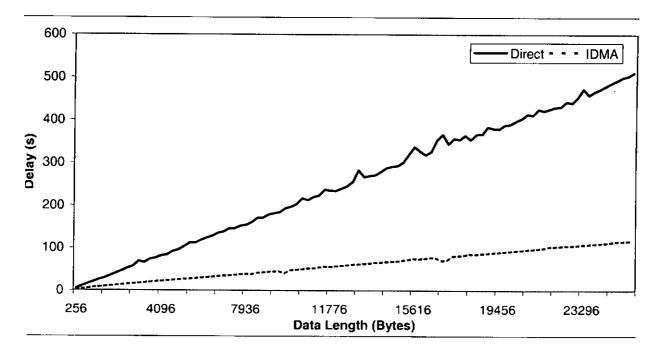

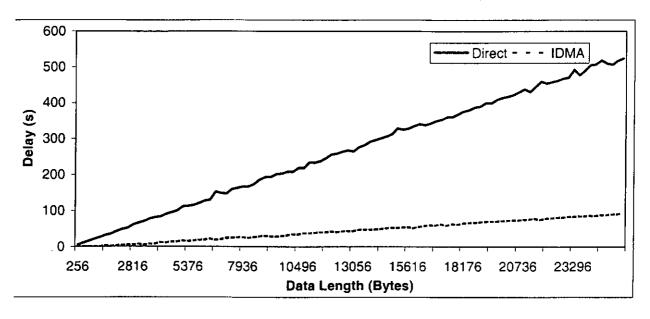

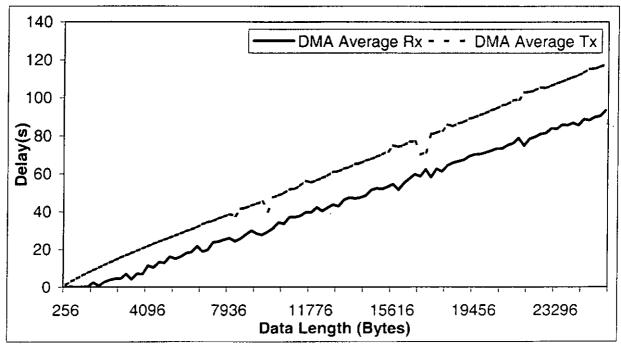

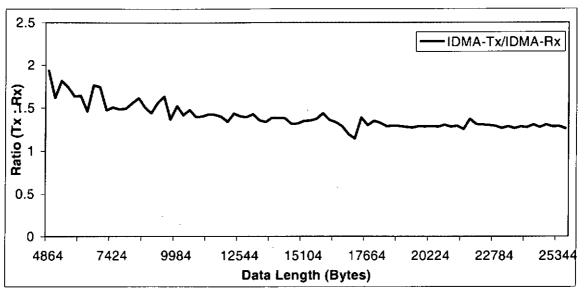

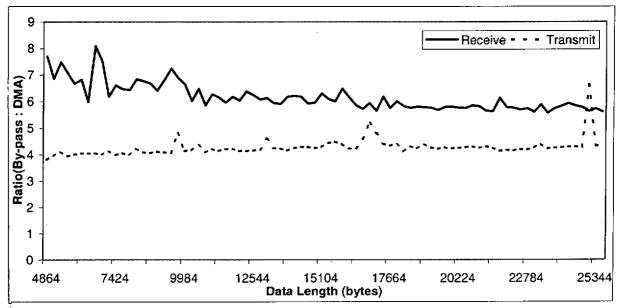

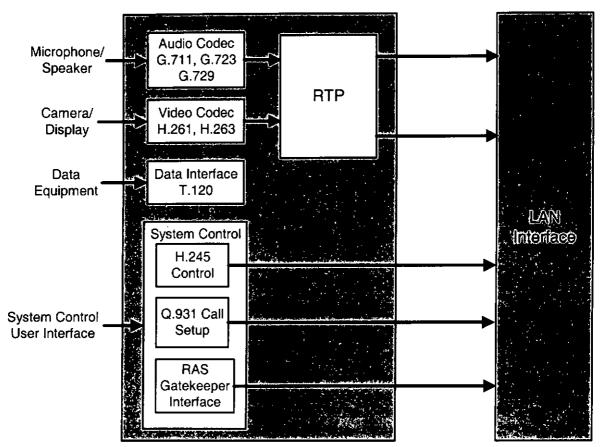

Figure 4-2c Rate of Single Connection of DAA under 100m Second Round Trip Times and Link Bandwidth