#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

# A Study of Copper Thickness Distribution in Electroplating of Printed Circuit Boards

By Tony H.T. Chow

May 2004

**Master of Philosophy**

Department of Industrial and System Engineering

The Hong Kong Polytechnic University

A thesis submitted in partial fulfillment of the requirement for the

Degree of Master of Philosophy

A Study of Copper Thickness Distribution in Electroplating of Printed Circuit Boards

## Certificate of Originality

I hereby declare that this thesis is my own work and that, to the best of my knowledge and belief, it reproduces no material previously published or written, nor material that has been accepted for the award of any other degree or diploma, except where due to acknowledgement has been made in the text.

Chow, Hin Tung Tony

## **Abstract**

Copper electroplating is a very critical process for the printed circuit board (PCB) industry and it is increasingly important to maintain an even copper deposition over the PCB surface as circuitry design gets finer and denser. Although there has been considerable amount of research efforts to enhance plating quality of PCBs over the last few decades, most of the studies still rely on relatively small or laboratory scale experimental set-up. With the collaboration of a local PCB manufacturer, the project has made an important attempt to study the copper deposition behaviour in an industrial tank with a plating window of 144 inches. An industrial copper electroplating tank was designed and set up in the project such that seven hardware factors can be varied and their effect on copper deposition distribution can be examined.

In the study, the Taguchi methodology was employed to examine the effect of plating tank design and configuration including anode geometry, anode distribution, electrode separation, relative size of the electrodes, cathode oscillation velocity, eductor orientation, eductor flow rate, and the current density on copper thickness distribution. Two consecutive sets of Taguchi design of experiment (DOE) were carried

out for both planner and pattern substrates PCBs, in which a total of 58 industrial scale experiments were carried out. The mean response of each factors were examined, and the experimental results showed that the copper deposition evenness can be improved using the enhanced hardware settings for current densities commonly used in the PCB industry. Strong interactions demonstrated that previous result or models based on a laboratory scale set-up may not be applicable to full scale production. The Copper thickness distribution along the 144" PCB cathode was also studied from top to bottom and from one end to the other, and the edge effect was examined. The significance of the findings to the PCB industry was discussed and the outcomes of the project have led to a good foundation for further theoretical investigations.

# List of Publication

- 1. H.T. Chow and K.C. Chan, "Enhancement of hardware factor for industrial PCB electroplating process", *Journal of Electronics Manufacturing*, to be Submitted

- 2. **H.T. Chow** and **K.C Chan**, "Deposition Behaviour of Copper in Electroplating Industrial Printed Circuit Boards", *Transactions of Institute of Metal Finishing*, to be submitted.

Page 3

# Acknowledgement

It is very much appreciated for all the supports provided by Topsearch Printed Circuit (Shenzhen) Ltd. Special thanks are given to the staffs and operators of R&D and outer layer production department.

# **Table of Content**

| ABSTRACT                                                       | 1  |

|----------------------------------------------------------------|----|

| LIST OF PUBLICATION                                            | 3  |

| ACKNOWLEDGEMENT                                                | 4  |

| TABLE OF CONTENT                                               | 5  |

| LIST OF FIGURE                                                 | 9  |

| LIST OF TABLE                                                  | 12 |

| 1. INTRODUCTION                                                | 15 |

| 1.1 Copper Plating Problems in PCB Industry and Topsearch      | 15 |

| 1.2 Research Collaboration with PCB Manufacturer               | 16 |

| 1.3 Objectives of the Project                                  | 18 |

| 2. LITERATURE REVIEW                                           | 19 |

| . 2.1 Industrial Copper Electroplating Process of PCB Industry | 19 |

| 2.1.1 Panel Plating and Pattern Plating                        | 19 |

| 2.1.2 Copper Electroplating Hardware                           | 20 |

| 2.2 Research on Copper Electroplating                          | 22 |

| 2.2.1 Modeling of Current Density Distribution                | 25 |

|---------------------------------------------------------------|----|

| 2.2.1.1 Work Piece Level Modeling                             | 26 |

| 2.2.1.2. Pattern Level Modeling                               | 31 |

| 2.2.1.3 Feature level Modeling                                | 35 |

| 2.2.2 The Effect of Anode on Electroplating                   | 39 |

| 2.2.3 The Effect of Agitation on Electroplating               | 41 |

| 2.2.3.1 The Use of Eductor                                    | 42 |

| 2.2.3.2 Other Forms of Agitation                              | 43 |

| 2.2.4 Pulse Current Electroplating                            | 45 |

| 2.2.5 Electrolyte – Chemical Additive and Conductivity        | 47 |

| 2.2.6 Copper Electroplating Optimization for the PCB Industry |    |

|                                                               |    |

| 2.3 Taguchi Methodology and Development                       | 52 |

| 2.3.1 Introduction to the Taguchi Methodology                 | 52 |

| 2.3.2 Progress and Case studies of the Taguchi Methodology    | 55 |

| 3. RESEARCH METHODOLOGY                                       | 56 |

|                                                               |    |

| 3.1 Introduction                                              | 56 |

| 3.2 Taguchi experiment setup                                  | 57 |

| 3.2.1 Definition of Hardware Factors                          | 59 |

| 3.2.2 Choice of Process Factors for the experiment            | 60 |

| 3.3 Experimental setup                                        |    |

| оо дарогиновии эспир                                          | 04 |

| 4. RESULT                                                     | 68 |

| 4.1 Enhancement of Plating Process Factors with Taguchi Methodology – Phase I    | 68 |

|----------------------------------------------------------------------------------|----|

| 4.1.1 Taguchi Mean Response Analysis                                             | 68 |

| 4.1.1.1 Anode Geometry                                                           | 69 |

| 4.1.1.2 Anode Distribution                                                       | 69 |

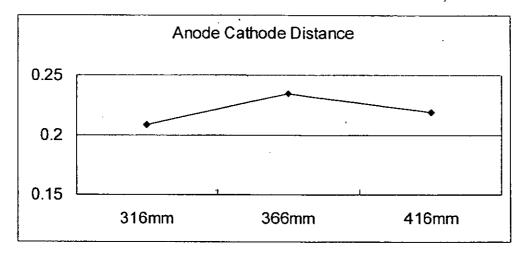

| 4.1.1.3 Anode Cathode Distance                                                   | 70 |

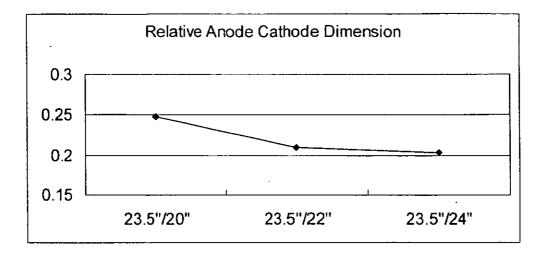

| 4.1.1.4 Relative Anode Cathode Dimension                                         | 71 |

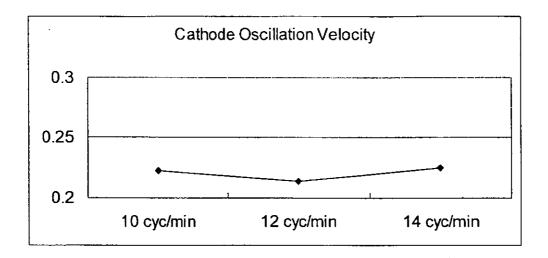

| 4.1.1.5 Cathode Oscillation Velocity                                             | 72 |

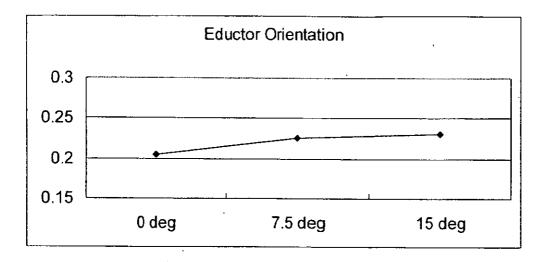

| 4.1.1.6 Eductor Orientation                                                      | 73 |

| 4.1.1.7 Eductor Flowrate                                                         | 74 |

| 4.1.1.8 Current Density                                                          | 75 |

| 4.1.2 Enhanced Hardware settings                                                 | 77 |

| 4.2 Plating Performance of Enhanced Hardware Settings under Different Current    |    |

| Densities                                                                        | 79 |

| 4.3 Process Factor Enhancement – Taguchi Analysis Phase II                       | 83 |

| 4.3.1 Enhanced Hardware settings for Pattern Plating from First DOE              | 83 |

| 4.3.2 Comparison of the Enhanced Hardware Settings from Phase I & II             | 84 |

| 5. DISCUSSION                                                                    | 88 |

| 5.1 Hardware factors and Current density                                         | 88 |

| 5.2 Difference in Deposition Behaviour between Pattern Plating and Panel Plating | 90 |

| 5.2.1 Enhancement of factors – Taguchi Analysis Phase I                          | 90 |

| 5.2.2 Enhancement of Factors – Taguchi Analysis Phase II                         | 93 |

| 3.3. Deposition Behaviour across the Cathode9             |

|-----------------------------------------------------------|

| 5.3.1 Top to Bottom9                                      |

| 5.3.2 Side to Side102                                     |

| 5. CONCLUSIONS 10°                                        |

| SUGGESTED TOPICS FOR FURTHER INVESTIGATION109             |

| S. STATEMENT OF ORIGINALITY AND CONTRIBUTION TO KNOWLEDGE |

| 11                                                        |

| APPENDICES113                                             |

| 0. REFERENCES                                             |

# **List of Figure**

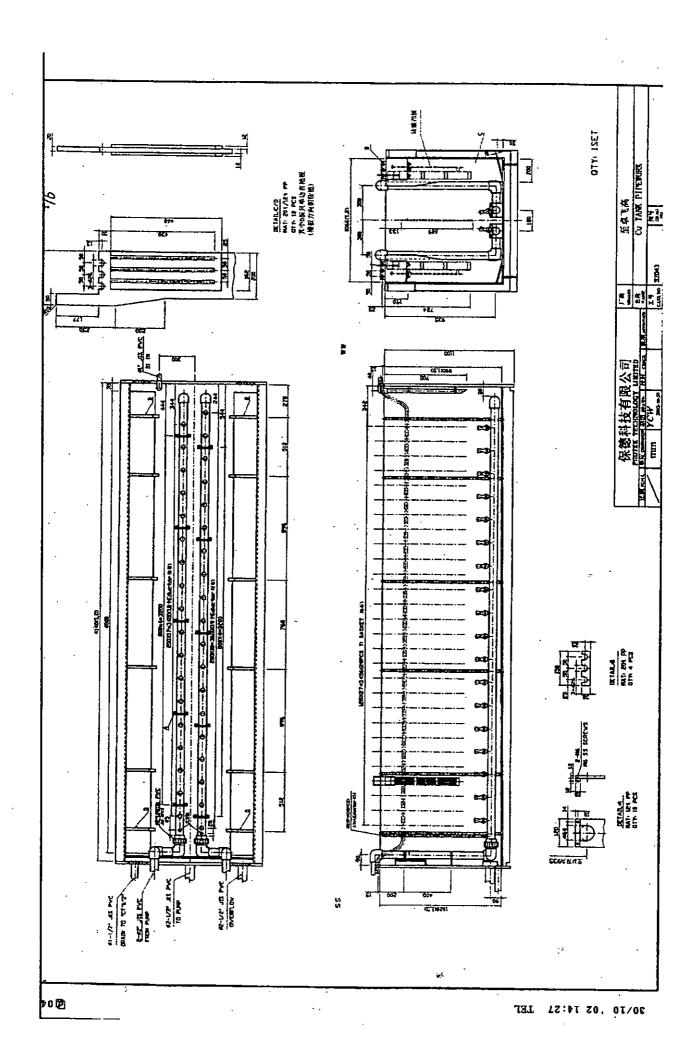

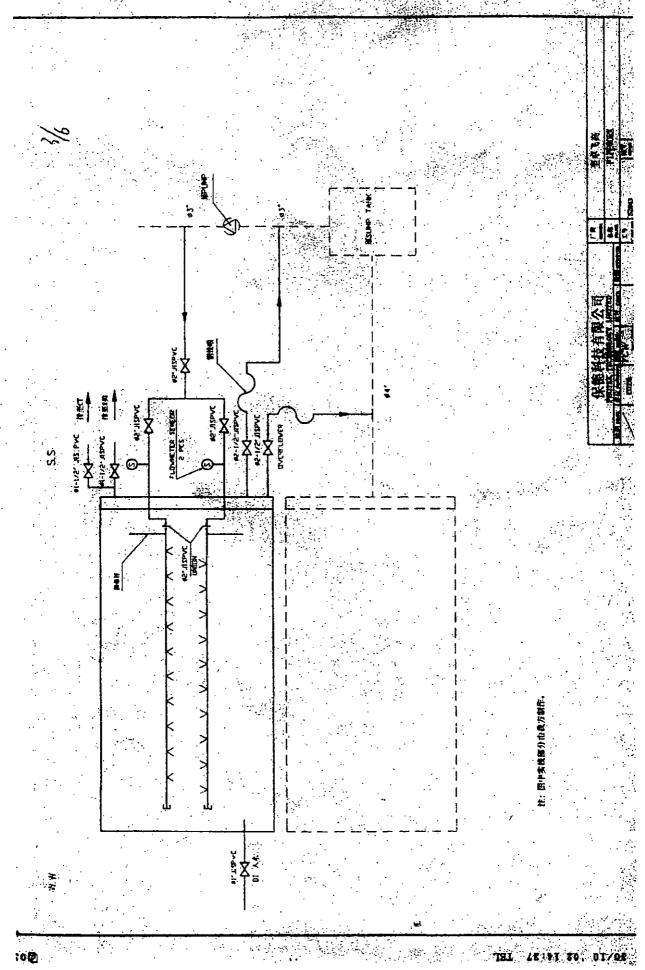

| Figure 3.1 The Protek Pulse Plating Line 64                                    |

|--------------------------------------------------------------------------------|

| Figure 3.2 Dutch Reverse Pulse Plating Rectifier                               |

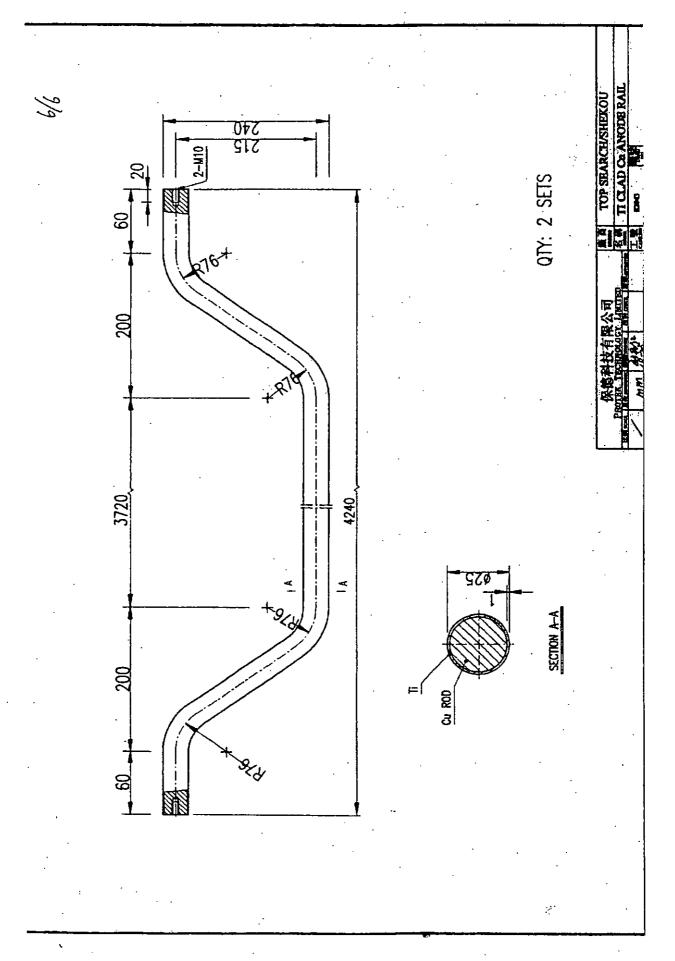

| Figure 3.3 Drawing of the Plating Tank                                         |

| Figure 4.1 Mean Response of Hardware Factor – Anode Geometry                   |

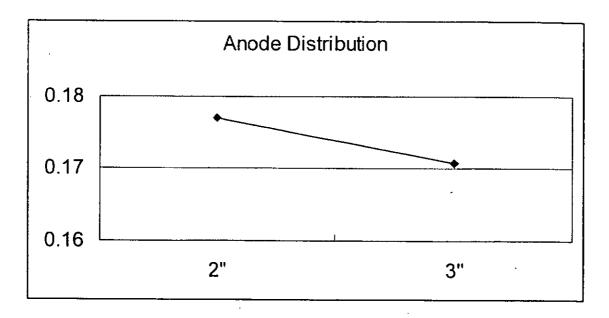

| Figure 4.2 Mean Response of Hardware Factor – Anode Distribution               |

| Figure 4.3 Mean Response of Hardware Factor – Anode Cathode Distance 71        |

| Figure 4.4 Mean Response of Hardware Factor - Relative Anode Cathode Dimension |

|                                                                                |

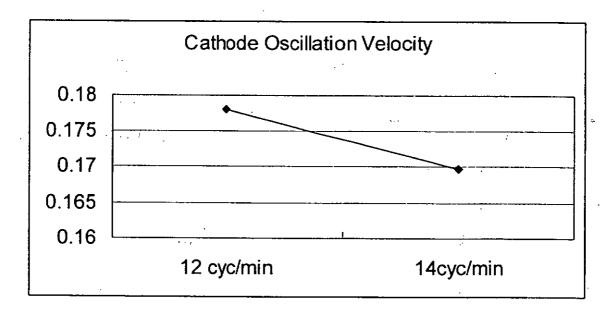

| Figure 4.5 Mean Response of Hardware Factor - Cathode Oscillation Velocity     |

|                                                                                |

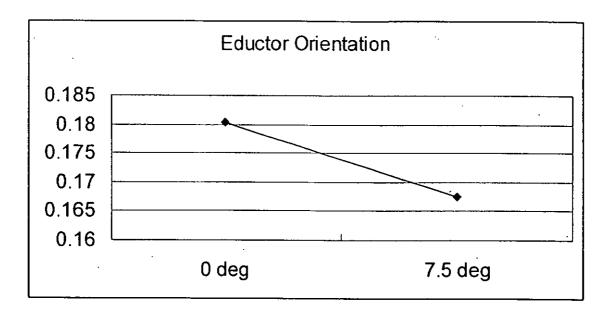

| Figure 4.6 Mean Response of Hardware Factor – Eductor Orientation              |

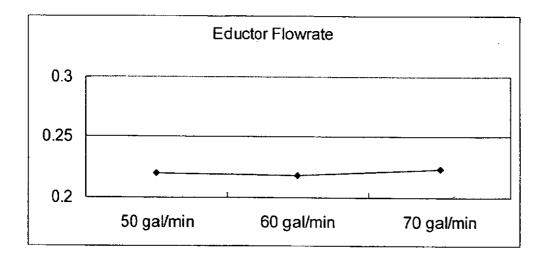

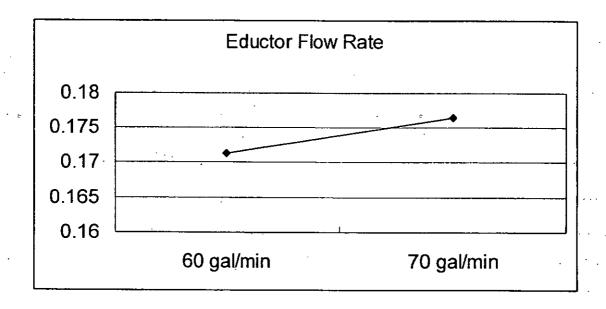

| Figure 4.7 Mean Response of Hardware Factor – Eductor Flowrate                 |

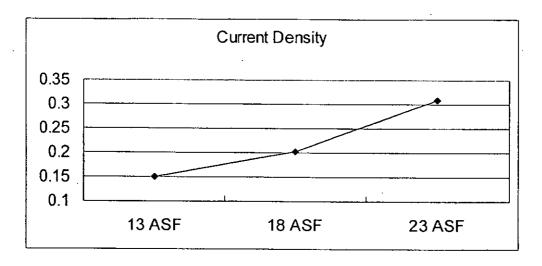

| Figure 4.8 Mean Response of Hardware Factor – Current Density                  |

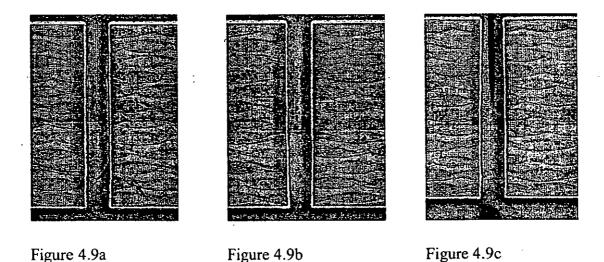

| Figure 4.9a – c Example of Cross Section Photos from Experiments with 13ASF 79 |

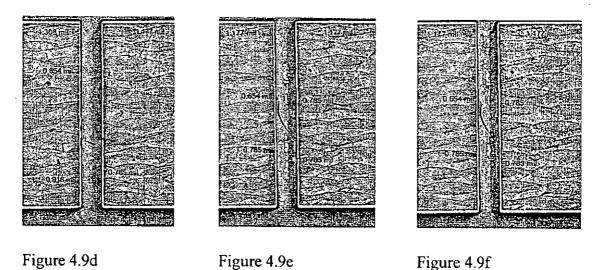

| Figure 4.9d – f Example of Cross Section Photos from Experiments with 23ASF 80 |

| Figure 4.10 Anode Distribution Mean Response of L <sub>8</sub> DOE             |

| Figure 4.11 Cathode Oscillation Velocity Mean Response of L <sub>8</sub> DOE      |

|-----------------------------------------------------------------------------------|

| Figure 4.12 Eductor Orientation Mean Response of L <sub>8</sub> DOE               |

| Figure 4.13 Eductor Flow Rate Mean Response of L <sub>8</sub> DOE                 |

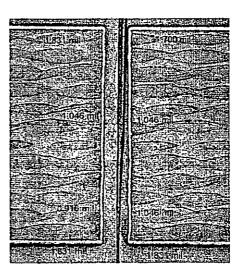

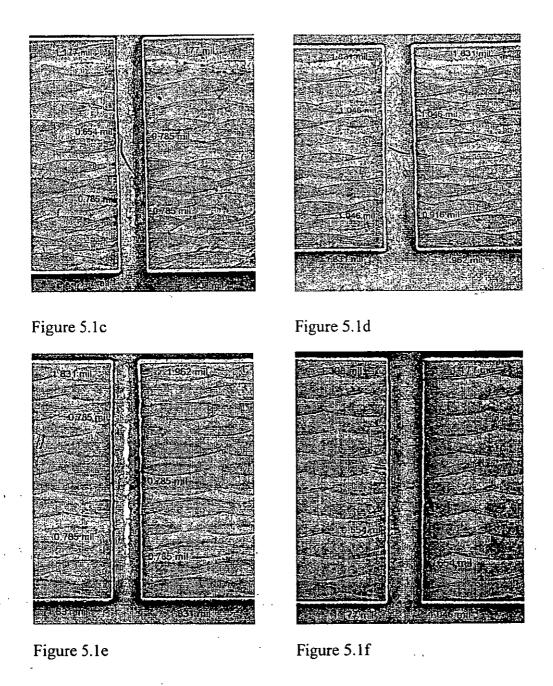

| Figure 5.1a – f Sample Cross Section Photos from DOE experiments 91-92            |

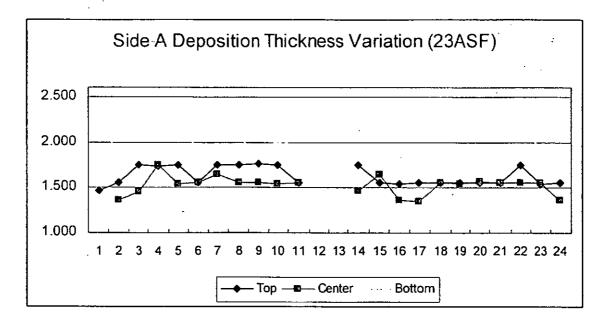

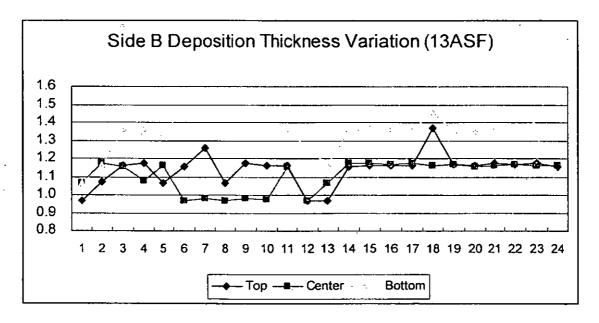

| Figure 5.2a Deposition Behaviour over the 144" Cathode - with Enhanced Hardware   |

| and Current Density settings – A                                                  |

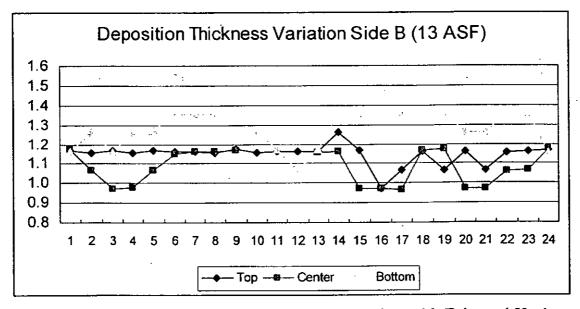

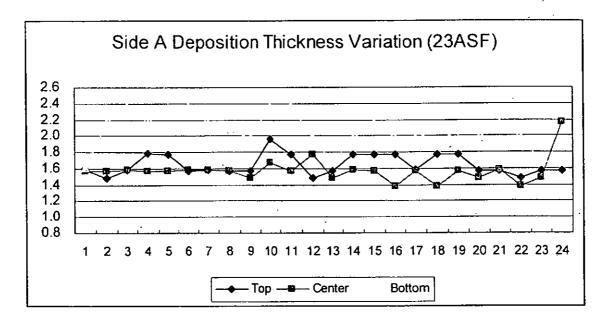

| Figure 5.2b Deposition Behaviour over the 144" Cathode - with Enhanced Hardware   |

| and Current Density settings – B                                                  |

| Figure 5.3a Deposition Behaviour over the 144" Cathode - with Enhanced Hardware   |

| settings and 23ASF – A                                                            |

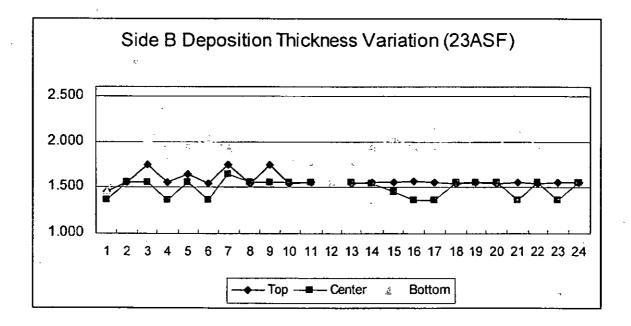

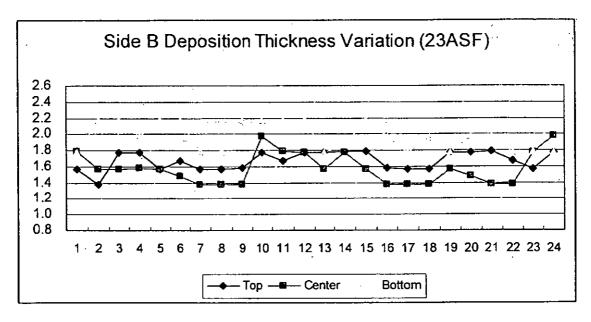

| Figure 5.3b Deposition Behaviour over the 144" Cathode - with Enhanced Hardware   |

| settings and 23ASF – B 97                                                         |

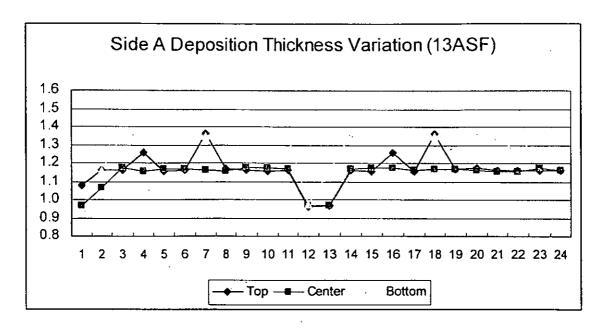

| Figure 5.4a Deposition Behaviour over the 144" Cathode - with Production Hardware |

| settings and 13ASF – A                                                            |

| Figure 5.4b Deposition Behaviour over the 144" Cathode - with Production Hardware |

| settings and 13ASF – B                                                            |

| Figure 5.5a Deposition Behaviour over the 144" Cathode - with Production Hardware |

| settings and 23ASF – A                                                            |

| Figure 5.5b Deposition Behaviour over the 144" Cathode – with Production Hardware    |

|--------------------------------------------------------------------------------------|

| settings and 23ASF – B                                                               |

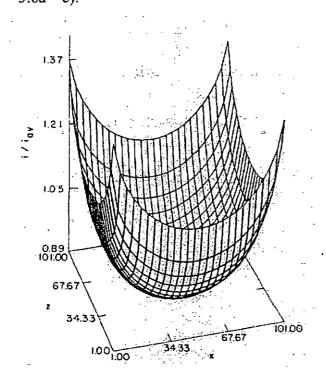

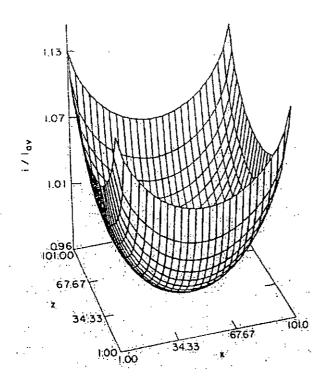

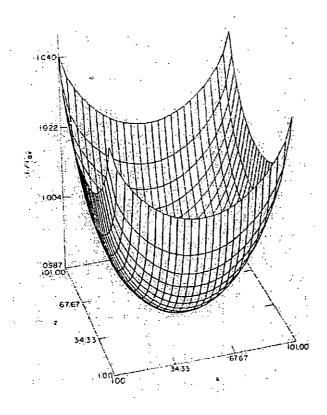

| Figure 5.6a Three dimensional Current Distribution over Cathode surface at Domain of |

| k <sub>c</sub> /A=0.5                                                                |

| Figure 5.6b Three dimensional Current Distribution over Cathode surface at Domain of |

| k <sub>c</sub> /A=2.5                                                                |

| Figure 5.6c Three dimensional Current Distribution over Cathode surface at Domain of |

| kc/A=10104                                                                           |

# List of Table

| Table 3.1 Taguchi DOE L <sub>18</sub> (2 <sup>1</sup> x3 <sup>7</sup> ) Matrix 62  |

|------------------------------------------------------------------------------------|

| Table 3.2 Parameter Levels Summary                                                 |

| Table 3.3 Taguchi L <sub>8</sub> (2 <sup>4</sup> ) Matrix                          |

| Table 4.1 Comparison of Recent Production and Enhanced Process Settings for Copper |

| Electroplating Tank                                                                |

| Table 4.2 Comparison of Deposition Evenness between Recent production and          |

| Enhanced Hardware Settings                                                         |

| Table 4.3a Comparison of Deposition Behaviour with Enhanced Hardware Setting with  |

| 13 and 23 ASF Current Density – Trial 1                                            |

| Table 4.3b Comparison of Deposition Behaviour with Enhanced Hardware Setting       |

| with 13 and 23 ASF Current Density – Trial 2                                       |

| Table 4.4a Comparison of Deposition Behaviour with Production Hardware Setting     |

| with 13 and 23 ASF Current Density – Trial 1                                       |

| Table 4.4b Comparison of Deposition Behaviour with Production Hardware Setting     |

| with 13 and 23 ASF Current Density – Trial 2                                       |

| Table 4.5 Comparison of Deposition Evenness for Production and Enhanced Setting    |

| Table 4.6 Comparison of Enhanced Process Factors of Panel and Pattern Plating from |

|------------------------------------------------------------------------------------|

| DOE Phase I                                                                        |

| Table 4.7 Comparison of Enhanced Hardware Settings from First and Second Phase     |

| Taguchi DOE85                                                                      |

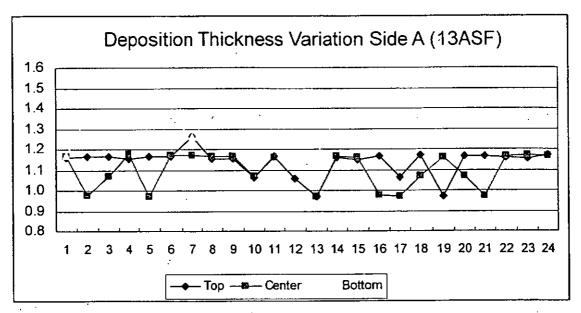

| Table 5.1 Deposition Thickness Behaviour from Top to Bottom - with Enhanced        |

| Hardware Setting and 13ASF                                                         |

| Table 5.2 Deposition Thickness Behaviour from Top to Bottom - with Enhanced        |

| Hardware Setting and 23ASF                                                         |

| Table 5.3 Deposition Thickness Behaviour from Top to Bottom - with Production      |

| Hardware Setting and 13ASF                                                         |

| Table 5.4 Deposition Thickness Behaviour from Top to Bottom - with Enhanced        |

| Hardware Setting and 23ASF                                                         |

| Table 5.5 Deposition Thickness Behaviour from Side to Side - with Enhanced         |

| Hardware Setting and 13ASF                                                         |

| Table 5.6 Deposition Thickness Behaviour from Side to Side - with Enhanced         |

| Hardware Setting and 23ASF                                                         |

| Table 5.7 Deposition Thickness Behaviour from Side to Side – with Production       |

| Hardware Setting and 13ASF             | 106                                     |

|----------------------------------------|-----------------------------------------|

| Table 5.8 Deposition Thickness Behavio | our from Side to Side - with Production |

| Hardware Setting and 23ASF             | 106                                     |

### 1. Introduction

### 1.1 Copper Plating Problems in PCB Industry and Topsearch

Electro-plating is a very critical process in printed circuit boards (PCBs) industry. As the geometry of PCBs and integrated circuit is becoming smaller, the copper plating distribution over the PCB surface is becoming more important. An evenly distributed surface copper deposition is critical for the fine features manufacturing for the chemical etching after the electroplating process. The deposition evenness over the PCB surface is directly related to etch rate, thus the shape and width control of the circuitries created. The shape and line width control, which are directly related to the electrical performance of the end products, are of significant importance especially when recent advance PCB features are downsized to 2mil (50μm) in mass production.

In order to meet the market demand, PCB shops need to improve the plating process so that fine lines and circuitries can be manufactured in mass production.

Academic researches have been carrying out in different areas of the copper electroplating process. These include the effect of chemistry, hardware design as well

as the nature of the current application on the deposition behaviour. However, most of the results reported were based on the studies of a limited number of process factors in relatively small scale equipment, which might not be well applied due to the complexity of the industrial process. The interactions between process factors also limit the application and integration of these academic findings into the industrial arena. There is a need to conduct a systematic study to examine the effect of hardware design factors on the plating quality using industrial plating tanks. This can help provide a better understanding of the copper electroplating process in industrial scale and to provide verification or integration of the results and efforts from academic researches.

#### 1.2 Research Collaboration with PCB Manufacturer

This research was a collaboration project between Industrial and Systems

Engineering Department of the Hong Kong Polytechnic University and Topsearch

Printed Circuits (HK) Ltd. The funding of the research was supported by the Topsearch

and the University-Industry Collaboration Program (UICP) of Innovative Technology

Fund of the Industrial Department of the Hong Kong Special Administrative Region

(HKSAR).

The UICP aims at stimulating private sector interest in R&D through leveraging the knowledge and resources of universities. The emphasis is on close collaboration between private companies and universities in Hong Kong. The Teaching Company Scheme of the program aims at fostering university-industry partnership by supporting local companies to take graduate students from local universities to assist in proprietary R&D work.

Topsearch Printed Circuits Company Ltd is one of the leading Hong Kong based

PCB manufacturers. The manufacturing facility of Topsearch is set up in Shenzhen,

China while headquartering in Hong Kong. Topsearch invests on research and

development in different areas of the PCB industry and is collaborating different

research programs with the universities. These include the set up of a joint

environmental research center with the Beijing Tsing Hua University as well as PCB

technology research programs with the Hong Kong Polytechnic University.

Experiments were carried out in an industrial plating tank in the Shenzhen factory of

Topsearch.

# 1.3 Objectives of the Project

Tally with 12 Supplement

The prime objective of the project is to study the effect of different hardware settings on the copper electroplating quality of the PCB industry in terms of copper deposition evenness. The specific objectives of the project are:

- 1. To develop a copper plating tank set-up in industrial scale for experimental investigations

- 2. To apply the Taguchi method to study the effect of different electroplating process factors on the copper deposition evenness

- 3. To examine the copper deposition evenness on the PCB substrate across the cathode in the PCB industrial electroplating process

## 2. Literature Review

# 2.1 Industrial Copper Electroplating Process of PCB Industry

#### 2.1.1 Panel Plating and Pattern Plating

Traditional copper plating process in PCB industry consists of panel plating and pattern plating. In panel plating, copper is deposited onto the entire PCB surface of a thin layer of base copper and through holes. From industrial point of view, panel plating can provide a more uniform copper deposition over the entire PCB surface. However, the cost of panel plating is relatively higher due to the cost of copper is relatively more expensive. An evenly thickened copper layer will also increase the difficulties for the subsequent etching process control to provide well-defined circuitries.

In pattern plating, copper is deposited onto the desired circuitries and features by electroplating over an organic protective mask laminated on the PCB surface. Tin plating, after copper plating, is also required to protect the desired circuitries and features from the subsequent chemical etching process. From industrial point of view,

pattern plating can provide a more precise control of circuitry dimension and minimize the waste of copper which is relatively expensive. However, a greater variation in copper deposition thickness would always be found due to the localized current effect induced by the conductive circuitry pattern. Over building of copper and tin may also increase the difficulties in removing the organic protective mask before the etching process.

#### 2.1.2 Copper Electroplating Hardware

The hardware of the copper electroplating process of the PCB industry is one of the critical concerns in production of reliable PCB products. It will affect the copper deposition thickness on the PCB surface while a specified thickness of hole wall copper is required to be plated. The electrochemical process includes a pair of anode and cathode in a well-agitated electroplating cell. In traditional PCB electroplating process, copper pallets contained in metallic anode baskets would be employed as the anodes while the PCB itself would be employed as the cathode. The anode baskets are distributed along an anode bar while the PCB will be attached to the cathode bar, both running across the width of the plating cell.

Good agitation for the electroplating process ensures that the electrolyte in the process can be well stirred, thus enhances the mass transfer for the electrochemical reaction. This is important, especially in large scale industrial plating cell, as the mass transfer of chemicals in the electrolyte is always one of the major limitations of copper deposition for the process, especially within through holes. Air sprinkling, vibration or/and oscillation of cathode bar as well as eductor circulations are the common agitation system used for traditional PCB electroplating process.

# 2.2 Research on Copper Electroplating

Works on and basics of electroplating factors were reported widely in previous literatures [1-4]. The effect of different copper electroplating process factors, such as the effect of chemicals, on plating performance was also investigated and studied [5, 6]. The importance of uniformity of plating thickness of plate through holes (PTHs) over the entire work piece (PCB) was discussed by Kessler and Alkire [7]. It is important to obtain an even copper plating thickness over the surface of PCBs. There have been considerable amount of efforts to investigate the relationship of various plating parameters and their corresponding effects on PCBs. Although good attempts have been made to use pulse current, hardware design parameters and new plating bath composition to enhance plating process, design of plating tanks as a whole which is known to significantly affect plating quality is still based on previous experiences and industrial rules of thumb. Literatures were reported extensively (for example [8]), however, only in laboratory scales on the relationship between few design factors and the plating thickness variation, although the technology of through mask plating had been used for the electroplating of PCBs for more than 20 years [9].

Computer softwares were also developed for simulation of the industrial

electroplating process including the design of plating tanks. Simulation and design tools for electroplating were also updated by Druesne and Afzali [10]. In the report, the computer software ACIS® was described and introduced. The software was developed based on boundary element analysis. In the studies, the modeling of plating a rack with zinc and full optimization of hard chromium plating of valves were carried out with ACIS® computer software. The results of the simulation of the electroplating process generated by the computer software were in close agreement with the measurements taken from the plating cell. Other studies also reported that the reliability of computer simulation for electroplating design could be verified by different industrial applications [11, 12].

Design of experimental (DOE) will be a practical tool to provide an insight into the multi-parameter nature of the electroplating process. Numerical techniques, such as boundary element methods, were reported but few have been published in experimental approach for problem solving [13]. Numerical methods are constrained due to complexity of surface feature for PCB electroplating. Poon et al., [9, 13] reported the relationship of plating thickness variation and various plating parameters recently with experimental approach but only few plating tank design factors were

considered.

Although it is well known that the deposition thickness will be thicker at lower pattern density, such as isolated traces and PTHs on PCBs, it was only first described by Romankiw et al., until the 70's [14]. Horkans and Romankiw [15] also reported and discussed such effect in their later studies. The hypothesis of "crowding" of flux at isolated features was suggested. Yung et al. [16] also reported similar observations in their work. Theoretical and mathematical modeling of such effect on patterned features was also carried out by Mehdizadeh et al. with potential-theory for electroplating [17, The active-area-density (AAD) was introduced in their work which defined a 18]. fractional electro-active area within a particular region of interest. The AAD concept was also employed by other researchers including Choi and Kang [19] and Poon et al. In the study by Poon et al., the concept of active area density ratio was further elaborated which provided a more detailed study of effect of plating parameters on the variation of deposition thickness in the PCB plating process.

### 2.2.1 Modeling of Current Density Distribution

Models of current density distribution in acid copper electro-deposition were reported by researchers with mathematical treatment. However, these numerical models are limited by the correctness of the physiochemical description of the system and the precision in which the process parameters are known. The nonlinear electrode kinetics and mass transfer characteristics of electrolyte also make analytical solutions impractical even for the simplest geometries [20, 21]. Current distribution is critical for the deposition thickness because the deposition rate is proportional to the current density at a location. It is also worthwhile to note that other factors, for example the chemical component mass transfer at the boundary layer, can also affect the plating distribution.

A review of current distribution modeling was carried out by Poon and Williams [8] based on studying how the deposition uniformity was affected and optimized by the various process and product parameters of the system. A study by Dokovic [22] is particularly appropriate to the PCB electroplating. These size scales includes:

1. Work piece scale - current distribution over the whole object under

- electrodeposition such as PCB panel.

- Pattern scale current distribution among the patterns on the surface of the work

piece with different densities of features such as the lithographic patterns over a

PCB panel.

- 3. Feature scale current distribution within an individual feature of a pattern such as the through hole, blind-via or conductor wire in a circuit pattern on a PCB.

- 4. Roughness scale the microscopic roughness or asperities of an individual feature.

The work piece level, pattern level and feature level modeling will be discussed in detail since the objective of this project is to study the quality of plating in a macro-scale point of view. Work piece and pattern level modeling are of particular interest because they resemble the panel and pattern plating of the PCB industry.

### 2.2.1.1 Work Piece Level Modeling

The nature of analytical methods has limited early investigations to flat surface and simple geometries. Numerical analysis developed later has enabled studies to be

carried out for more complex geometries. For the electroplating process in the PCB industry, electrodes are set up in a parallel planar geometry and two and three dimensional models have been proposed by researchers based on a similar setting.

Moulton [23] presented a classical solution for the primary current distribution for two electrodes placed on the boundary of a rectangle. Wagner [24] proposed with formal mapping of the parallel electrode to solve the primary current distribution. His study concluded that the primary current density is infinite at both ends of the electrode and decreases exponentially and symmetrically until a minimum value at the centre of the electrode. This implies that the deposition rate at both end of the electrode will be much faster than that in the middle.

$$\frac{i}{i_{avg}} = \frac{2}{\pi \sqrt{1 - (x/m)^2}}$$

(1)

where x = the distance measured from the center of the electrode,

$i \text{ (mA/cm}^2)$  = current density at a point of distance x from the center of the electrode,

$i_{\text{avg}}$  (mA/cm<sup>2</sup>) = the average current density over the electrode and 2m = the length of the cathode (cm)

In the study carried out by Hine et al. [25], the effect of the ratio of electrode size, the separation of electrodes as well as the gap between the electrode and the insulating side wall was studied. It was concluded quantitatively that the larger the electrodes and the smaller the gap width, the more uniform the current distribution would be.

However, the current distribution was not shown explicitly as their focus was placed on the relative share of current at the two sides of the electrode under different cell geometries.

Yoshida et al. [26] and Koseki et al. [27, 28] reported the effect of unequal electrode length, different electrode separations and different gaps between the electrode and the insulating side wall on current density distribution. Their studies concluded that current uniformity could be enhanced when:

- 1. The anode is narrower than the cathode,

- 2. The electrode separation is smaller than half-length of the cathode, and

- 3. The edges of the cathode are in contact with the side walls, although only a weak

influence was observed.

The minimum electrode separation, however, was not defined in their study although it is of particular importance for the plating tank design. The practical application of their model was also criticized by Poon and Williams [9, 13] – the assumption of negligible polarization has restricted the current density used in their experiments to a very low value of 5 mA/cm<sup>2</sup>.

Choi and Kang [19] also reported a three dimension model to predict the current... distribution on a uniformly patterned cathode with an auxiliary electrode. The concept of active-area-density (AAD), developed by Mehdiazdeh et al. [17, 18], was used and they concluded that a smaller AAD will lead to a more uniform current distribution. It was further concluded that uniform current distribution could be obtained by proper combination of auxiliary electrode and the ADD. However, there was no comparison with experimental data in the paper. It is also worthwhile to notice that the study was carried out with electrodeposition of permalloy (80% Ni – 20% Fe) instead of copper, although the study may be applicable and applied to electroplating of copper.

Other studies of current distribution based on the work piece level were also reported by various researchers. Hull cell work piece modeling was carried out by Matlosz et. al., [29] and the DIN standard [30] offers an empirical formula for the primary current distribution in a Hull cell panel (cathode):

$$\frac{i(z)}{i_{avg}} = 2.331 \cdot \log \frac{1}{1-z} - 0.08 \qquad (2)$$

where i(z) is the local current density of a point at a normalized distance z measured from the low current density edge and 0.186 < z < 0.941. Researchers including Moulton [23], Hine et al. [25] and Yoshida et al. [26] also reported by similar methods in solving the primary distribution problem. The current distribution estimated as:

$$\frac{i(z)}{i_{avg}} = \frac{z^{1.273}}{(1-z)^{0.359}} (1.733 - 0.736z)$$

(3)

was found to be in good agreement with the empirical solution offered in the Norm DIN standard [30].

#### 2.2.1.2. Pattern Level Modeling

As mentioned, PCB pattern plating is a typical example of this pattern level category. Although PCB pattern plating has been widely used in the industry for more than 20 years, little was reported literarily until a formal mathematical treatment in 1988 according to Poon and Williams [8]. The two possible reasons are:

- i. the significant amount of work reported for work piece and feature modeling, particularly through-hole plating, suggests that problems in these two domains are of sufficient complexity to demand the effort of the most researchers in this areas

- ii. the numerical technique required to solve the pattern scale problem, notably the boundary element method (BEM), has evolved as a viable tool only after its successful application in solving problems at the other scales

It is well known in the PCB industry that the distribution of patterns (design feature and circuitries) is having a significant effect on the resulting current distribution, thus the electrodeposition thickness in the through mask plating process.

The effect was first described by Romankiw et al. [32]. In the study, the use of on-board "current thieves" which utilizes dummy patterns on the board surface was introduced to even out the current distribution. Other approaches described by researchers to solve the problem of uneven electrodeposition due to the pattern effect included employing an auxiliary cathode with separate galvanostatic control as off-board current thief [33, 34]. The on-board and off-board "current thieves" have been widely applied in nowadays PCB industry nowadays.

Mehdizadeh et al. [17] proposed the first theoretical model of current distribution over a patterned substrate using the potential theory model for electrodeposition. The expression active area density (ADD) was introduced in their paper in 1992 [18]:

$$AAD = \frac{A_{act}}{A_{sup}} \tag{4}$$

where  $A_{act}$  is the active area exposed to electrode-position over a particular region, e.g. the actual area of circuitry patterns over a PCB, and  $A_{sup}$  is the superficial area of that region, e.g. the geometric area of the PCB.

According to the AAD concept, they concluded that the pattern-induced nonconformity can be reduced by:

- 1. Increasing the bath conductivity,

- Application of a smaller average superficial current density over the cathode;

This, however, will reduce plating rate,

- 3. Reducing the ADD contrast among different regions on the substrate,

- 4. Reducing the size of the zone over which the AAD contrast occurs, and

- 5. Reducing the average AAD over the entire substrate.

The findings in their work, however, did not provided a practical solution for the PCB plating process from the perspective of production efficiency and product design criteria.

The model was further elaborated later by the same author in Mehdizadeh et al.

[18]. The modified model gives better deposition thickness prediction, especially in the case of application of high current density such as that in commercial plating process, than the previous model by introducing an enhancement factor. The model

shows that both active area density effect and the pattern driven mass transfer effects are contributing to the non-uniform current distribution over lithographic patterns. In their study, the "edge effect" of non-uniform current distribution was also reported numerically. They found that the primary current distribution is a step profile in inverse proportion to the active-area-density ratio. In order to prevent the concentrating of current density into the patterned region, they introduced the use of "current thief", or appropriate auxiliary electrodes to reduce the non-uniformity of current distribution.

Other studies of current distribution based on the pattern level were also reported by various researchers. Horkans and Romankiw [15] described the "crowding" of current lines into isolated pattern and Yung et al. [16] mentioned the effect of circuit layout on the macro-scale thickness uniformity.

### 2.2.1.3 Feature level Modeling

Good examples for feature level scale are the through holes and rectangular trench of a polymeric mask on a PCB. The influence of mass transfer and concentration over-potential as well as the evolution of the electrode shape during the deposition process become highly important [22] in feature scale modeling.

The effect of various plating factors on plating uniformity was reported by Alkire and Mirarefi [35]. Their study was regarded as the first mathematical analysis of through-hole problem [16]. The mathematical analysis was later confirmed experimentally by Engelmaier and Kessler [36]. They also found that the process window can be enlarged by adding organic additives, which is appropriate for both the PCB and chemical supplying industry.

Middleman [37] also showed that, although his assumption was considered controversial [22], periodic flow reversal was much more effective in promoting uniform reaction rate along the hole length than steady flow in one direction.

Experimental approach modeling was also recently carried out by Poon et al. [13] to study the effect of various factors on the variability in blind-via electroplating. It was verified experimentally that the optimum combination of the average current density and the electrode separation respect to minimum thickness variability across the whole work piece.

Theoretical analysis of the plating of high aspect ratio (HAR) through-holes was carried out by Lanzi and Landau [38]. The limiting current due to mass transfer and ohmic resistance effect was calculated and two expressions were developed:

Mass transfer:

$$\bar{i}_{L,avg} = \frac{FD_{iCb}}{R_0} \{ 1.15 A^{\frac{1}{3}} - 1.2 - 0.65 A^{-\frac{1}{3}} \}$$

(5)

Ohmic resistance:

$$i_{c,\Omega} = \pi^2 RTR_{0\kappa} / \alpha_c FL^2 \qquad (6)$$

where  $i_{L,avg}$  is the average current density at the limiting mass transfer rate (mA/cm<sup>2</sup>);

Di is the diffusion coefficient of cupric ion (cm<sup>2</sup>/s);

A is a convection variable jointly determined by hole/bath geometry and electrolyte characteristic;

$i_{c,\Omega}$  is the upper limit of the (secondary) current density at the center of the hole imposed by ohmic resistance (mA/cm<sup>2</sup>).

It was concluded from the study that the ohmic resistance imposed the critical limitation on the current density within the through holes. The dominant effect of ohmic resistance on current density within a through hole was also reported by Yung et al. [16]. Alkire and Ju [39] also suggested improving the plating uniformity in HAR. holes by reducing the effect of ohmic resistance by

- 1. increasing the electrolyte conductivity,  $\kappa$ ,

- 2. reducing the hole length, L, and increasing the radius,  $R_0$ ,

- 3. miniaturizing the hole for a given aspect ratio, thus reducing  $L^2/R_0$ ,

- 4. reducing  $\alpha_c$  by altering the reacting kinetics with organic additives.

The recommendations were also rectified by the general model of Hazlebeck and

Talbot [40] for the case of ohmic-limited plating.

Other experimental approaches to study the current distribution on feature scale were also reported by various researchers. Barringer and Carano [41] used a 2<sup>3</sup> full factorial design to study the effects of bath temperature, leveling agent and the acid/copper ratio on electrodeposition evenness. Haluzan and Reichenbach [42] employed a Taguchi L<sub>18</sub> orthogonal array to study the effect of the concentration of copper, formaldehyde, caustic soda, temperature and deposition time on the electroless deposition rate and coverage. Forrest and Reed [43] investigated the effects of the same set of parameters on the S/H ratio of electroplated copper in HAR through-holes using a replicated D-optimal design of 32 runs. Bokisa and McFarland [44] employed a general factorial design to study the influence of aspect ratio, current density and copper sulphate concentration upon the S/H ratio of plated-through holes.

# 2.2.2 The Effect of Anode on Electroplating

Until recent years anodes have been amongst the least considered factors in electroplating process and in early textbooks very little space was given to their use and design etc. However, anode related process parameters (e.g. shape of anodes [45]) are well known of having significant effect on plating efficiency and quality. Cobley and Gabe [46] presented the application of different types of anode and the future developments for more efficient anodes. Soluble copper anode is commonly used in the PCB industry for copper electrodeposition but few studies have been carried out to report the effect of anode related parameters on the electrodeposition thickness variation at work-piece-level. The usage and performance of insoluble anodes, however, were reported by different researchers. Sriveeraraghavan et al. [45] performed a study on the effect of different shapes of insoluble and soluble anodes on plating thickness distribution and porosity. It was reported that soluble anodes of square, circular and rectangular shape with equal area to the cathode can be used. Soluble anode of triangular shape with 50% lesser area as that of the cathode can be used and may also reduce the cost of anodes and minimizing the impurities build up while maintaining similar current efficiency and metallic plating distribution. It is

also worthwhile to note that the plating thickness variation in their study was not optimized based on the experimental data. Further verification of the experimental result was not reported.

Cobley et al. [47] also reported and summarized the application of insoluble anode. A set of criteria was established, which an insoluble anode material should meet if it is to be successfully employed in an acid copper horizontal electroplating machine in their studies

# 2.2.3 The Effect of Agitation on Electroplating

Agitation is a critical process factor in the electroplating process but received relatively little investigation over the 150 years of electroplating process development [48]. It is well known that appropriate agitation can have significant effects including:

- 1. Avoiding stagnation by dispersing products and transport reactants,

- 2. Increasing deposition rates through stirring to reduce electrode diffusion layer thickness,

- 3. Removal of heat from the interface and equilibrate the deposit or coating,

- 4. Incorporating particles in the deposit (composite coating production), and

- 5. Modify the deposit properties of grain size, hardness etc. [48]

One of the major effects of agitation is to provide a thin and uniform layer, the diffusion layer, for a restricted concentration variation of chemistry of the electrode surface, which was reported by Lyons [49].

Air bubbling is still being used in the PCB electroplating process due to its simplicity, relative effectiveness and reasonably low cost. The relative importance of

air sparging in comparison with mechanical board oscillation and their effects on the mass transfer rate over the entire board surface as well as in the interior of the through-hole was also reported [50]. However, research [48] showed that a 20-30% loss in conductivity of the plating solution can be induced by air bubbling and the loss over the plating process tank is not uniform. It is concluded that in the electrodeposition process where good throwing power is required, the performance of electroplating is related to the type and degree of agitation used. The significance and importance of solution conductivity for electrodeposition solutions and their efficient used were discussed by Guvendik and Gabe [51]. This significant loss in solution conductivity is important from the efficiency of plating point of view and is critical for the PCB industry. Among the different forms of agitation, the use of eductors in the electroplating process for PCB industry is becoming popular.

#### 2.2.3.1 The Use of Eductor

The use of eductors, which are available in many proprietorial forms, is in principle old technology but has recently been adapted to use in electroplating application. One of the pioneers reporting the effect of educator on PCB

electroplating is Ward et al. [48]. In their study, the effect of eductor on the deposition thickness variation across 18"x24" copper boards was reported. The effect of a single, 4, 6 and 8 eductors for agitation was investigated. A comparison was also made between educators and air bubbling as an agitation mean for copper electroplating process. It was concluded based on their experimental result that a faster deposition rate, reduction in variation of deposition thickness across the panels as well as minimization of the 'edge effect' on large panels can be achieved by using educators for agitation. The author also commented that the geometry of eductor is believed to be a significant feature of its effectiveness.

In another study, Ward and Gabe [52] reported the used of eductor agitation and showed its importance in the contest of surface heat dispersal of the electrodes, thus improvement on deposition properties that are temperature sensitive can be achieved.

## 2.2.3.2 Other Forms of Agitation

Studies were also carried out at an earlier time by Gabe et al. [53-55] to investigate the effect of vibratory agitation for electrodeposition. The characterization

of vibratory agitation, together with the effect of vibration on deposition rate and composite plating were reported. The study [54] found that the rate of electrodeposition could be enhanced by 5-20 times.

In the study carried out by Duchanoy and Lapicque [56], the effect of flow pattern on current distribution was discussed. Velocity and flow characteristic of the fluid flow across the substrate were reported to be directly related to the current distribution.

# 2.2.4 Pulse Current Electroplating

The use of pulse current electroplating in different industries and academic research have been developing and reported extensively over the pass few decades. Pulse plating has been regarded as a better deposition mode than DC electroplating since the relaxation period during the reverse plating and/or rest enables larger currents to be applied during the pulse-plating period without the concentration depletion of reactants [57]. The anticipated advantages of pulse plating [58] based on previously reported work can be enumerated:

- i. improved physical properties including increased hardness [59-61] as a result of finer grained structure [62], reduced porosity [63-67], and also increased density, ductility and electrical conductivity [68, 69];

- ii. increased deposition current density, and hence plating rate, by virtue of operating nearer the instantaneous limiting current density [70, 71];

- iii. improved adhesion of the deposit to the substrate, possibly due to oxide film reduction [70], and

- iv. improved plating distribution and thickness uniformity especially in relation to recesses [70, 71].

Bai and Hu [72] reported the effects of five plating modes, including DC potentio-static and galvanostatic, pulse-rest and pulse-reverse plating and cyclic voltammetry, on the morphology and roughness of Copper deposits. Kalantary and Gabe [58] also investigated the cathode efficiency and coating properties in pulse plating. They concluded that the cathode efficiency can be increased under certain unipolar pulse conditions. The coating properties including the microhardness, tensile strength and elongation are directly affected by the pulse technique used.

In a later study by Hu and Wu [73], the delectrodeposition of various copper deposits was also carried out by means of cyclic voltammetric, potentiostatic, galvanostatic, pulse-rest and pulse reverse plating modes. It was report in the study that either cyclic voltammetry or reverse plating rendered the significant dissolution of grain peaks and resulted in a relatively smooth electroplating surface

# 2.2.5 Electrolyte - Chemical Additive and Conductivity

The potential gradients in solution, the electrolyte composition and the influence of organic additives are of major concern for copper electrodeposition and have been studied for over 50 years [74]. The significance of solution conductivity for electrodeposition solutions and their efficient usage were discussed by Guvendik and Gabe [51]. In the report, the conductivity data for copper, tin, iron, nickel, zinc as well as other plating solutions were presented and reviewed. Chemical additives in electrolyte solutions also play important roles in copper electroplating [75]. It is of great importance in the PCB industry as the demand of integrated circuit and via hole filling is increasing. In the research by Gau et al [75], it was found that the addition of thiourea and polyethylene glycol, which are usually added in PCB electroplating chemistry to influence nucleation, could help in forming of smooth copper film but did not promote copper filling ability. Hydroxyl amine sulphate was purposed for use as a gap filling promoter in helping copper electroplating. It was demonstrated in their study that copper could be electroplated into fine trenches without void when hydroxyl amine sulfate was presented in the plating solution.

Reid [74] reported the dependence of IC filling processes upon plating bath

chemistry and polarization characteristics. In the study, it was found that filling is most readily achieved by using additives containing a polymer suppressor and a mercapto accelerator. Highly polarized electrolytes which maintain strong current suppression on the wafer surface and aid in uniform nucleation within features are beneficial to high aspect ratio feature filling.

In the research carried out by Miura and Honma [76], via-filling for build up process of PCBs and the ultra large scale integration (ULSI) wiring formation without void and over plate has been examined. Acid cupric sulfate bath containing chloride, polyethylene glycol, bis (3-sulfopropyl) disulfidedisodiu, Janus Green B and thiourea was employed as the electroplating electrolyte in the study. It showed that void-free filling can be achieved in the range of 0.18-180 µm via holes and trenches by the selection of these additives.

# 2.2.6 Copper Electroplating Optimization for the PCB Industry

Over the pass few decades, many studies were reported based on laboratory scale investigation to evaluate the effect of different factors on copper electroplating for the PCB industry. Researchers [41-44] studied the through hole plating process of the PCB industry with statistical experimental design and empirical modeling. These studies were focused on feature scale but had shown obvious directions of process improvement in the form of a set of recommended factor settings.

Poon et al. reported the effect of various plating parameters on plating distribution [8-9, 13]. In their studies, fractional factorial and central composite designs experiments were carried out sequentially to model empirically the main effects. Possible interactions of the major process parameters on the average plating thickness and its variations in a blind via electroplating process were also reported. The effect of active current density, electrode separation, aspect ratio and the depth of the via-holes on the deposition uniformity were studied. It was identified that the significant process parameters affecting the work piece level uniformity are the average current density and the electrode separation [8]. The effect of the interaction between active current density and electrode separation is also significant to the variation of the work piece

level electrodeposition thickness [9]. Empirical models were developed in the studies to describe the effect of electrode separation, current density and active area density ratio on the deposition evenness in terms of the thickness standard deviation. The interactions between these factors were also described in their studies and reported in the models.

In a recent report by Tan and Lim [20], experiment was carried out in laboratory with experimental approach. The relationship of uniformity of electrodeposition and various factors was studied and reported. The factors involved in the study were offset voltage, bath agitation, temperature, anode-cathode separation and bath concentration. The effect of the factors were investigated and reported in a one-at-a-time basis. The research employed the wire beam electrode (WBE) which has been developed recently into a means of simulating the conventional one-piece electrode surface under electroplating and of measuring the distribution of electroplating current [21]. It was found that the offset voltage, bath agitation, temperature, anode cathode separation and bath concentration were having effects on the copper deposition evenness. Combination of the best values of each factor, however, did not provide any further improvement on the plating deposition evenness. This implied there were significant

interactions between the factors studied.

Other researches were also carried out to perform studies on the deposition behaviour of the electroplating process [77-82].

# 2.3 Taguchi Methodology and Development

# 2.3.1 Introduction to the Taguchi Methodology

The Taguchi methodology originated from Japan, introduced by G Taguchi, is a common tool employed by engineers for process enhancement/optimization. It should be seen as a very good engineering method rather than a philosophy. However, it does have a philosophical basis which is often excessively emphasized [83]. The Taguchi Method carries the major features of:

- 1. Pushing quality back to the design stage since quality control or statistical process control can never fully compensate for a bad design,

- 2. Routine optimization of product and process design prior to manufacture,

- 3. Initial emphasis on design not inspection (off-line),

- 4. To produce robust products with intrinsic quality and reliability characteristics,

- 5. It is a prototype methodology, primarily involving real physical prototypes,

- 6. Statistics is not the main point, and

- 7. Operational methodology with a philosophical basis in the "loss-to-society".

The Taguchi methodology is always introduced by similar guidelines of

### application. These include:

- 1. Brainstorming,

- 2. Statement of objectives,

- 3. Identification of factors Control, signal, output as well as the noise factors,

- 4. Definition of the Signal to Noise Ratio,

- 5. Selection of appropriate orthogonal array, and

- Experiment and analysis mean response and signal to noise graphical analysis.

The orthogonal array and signal to noise analysis are the major features of the Taguchi application. The orthogonal array, a fractional factorial design, provides an experimental approach to investigate the process with a minimal number of experiments. The signal to noise ratio, which is a major source of criticism of the methods, is:

- 1. A performance measure to choose control levels that best cope with noise,

- 2. adapted to improve statistical properties, and

- 3. constructed so that the maximum is optimum (since intuitively we wish to maximize the signal relative to the noise) [83].

The signal to noise ratio  $(S/N_N)$  depends on the criterion for response [84]:

#### 1. Nominal is best

$$S/N_N = 10 Log \frac{\frac{1}{n}(S_m - V_e)}{V_e}$$

(7)

where

$$S_m = \frac{(\sum y_i)^2}{n}$$

, .....(8)

$$V_{e} = \frac{\sum y_{i}^{2} - \frac{(\sum y_{i})^{2}}{n}}{n-1}$$

(9)

### 2. Smallest is best

$$\frac{S}{N_N} = -10 Log \frac{1}{n} (\sum y_i) \tag{10}$$

### 3. Biggest is best

$$\frac{S}{N_N} = -10Log(\frac{1}{n}\sum_{i=1}^{n}\frac{1}{y_i}) \qquad (11)$$

## 2.3.2 Progress and Case studies of the Taguchi Methodology

The rapid growth of the interest in Taguchi Methodology in Europe and United States in the 1980's has led to a great expansion in the number of published case studies [83, 84]. Conferences of the Taguchi Methods [83], for example, were held by researchers to share the experience of experimental approaches for industrial quality control. The method was applied to different industrial sectors including electronics, information technology, process industry, automotive and plastics for process improvement as early as the design stage. Many of these case studies were published as industrial journal, conference papers and technical paper collections of private companies [85–92]

The development in the Taguchi methodology has also been taking place worldwide. In a recent study by Huang [93], he developed the classical Taguchi quality selection model to the general. The classical Taguchi method considers the case there is one input characteristic and one output characteristics and it aims at selecting the best input mean to minimize the loss of quality. Huang developed the case of there are n input characteristics and m output characteristics.

# 3. Research Methodology

### 3.1 Introduction

In order to provide an understanding of the effect of eight process factors on the copper electrodeposition behaviour, the Taguchi methodology was used. This enabled the study to be carried out with feasible number of experiments in an industrial scale. The evolutionary nature of the Taguchi DOE approach, which always allows further elaboration of subsequent DOE to be carried out based on the results of the previous, has also made hardware factor settings enhancement feasible and practical.

Although the Taguchi approach was employed, the complexity of the PCB industrial plating process was introducing limitations in the study in terms of time and resources. Experiments of the Taguchi DOE were carried out with both substrates (PCB) with and without pattern – namely the pattern and panel electroplating respectively. Analysis was focused on the panel plating result while the pattern plating result was regarded as a control or reference. A second Taguchi DOE was setup based on the result of the first one. A total of 58 industrial experiments were carried out

### 3.2 Taguchi experiment setup

A seven three levels and one two levels factors DOE was set up according to Taguchi method. The  $L_{18}(2^1x3^7)$  experimental set was set up in which a total of eight factors can be examined at the same time. The  $L_{18}(2^1x3^7)$  matrix was listed in table 1 for reference. A total of 18 experiments would be done for each DOE set to study the effect of the eight factors on copper plating quality and efficiency.

The upper, (nominal) and lower levels of each parameters were listed in table 2.

The DOE were repeated with two sets of cathode substrates including:

- 1. Substrates (PCBs, panel plating) without pattern

- Substrate (PCBs, pattern plating) with circuitry design which are subjected to a larger deposition thickness variation based on mass production experiences.

Result analysis was based primarily on substrates without pattern to minimize any current crowding effect for simplicity. Control experiments were carried out with the substrates with pattern from an industrial point of view. While optimizing the hardware factors with the DOE with substrate without pattern, the general industrial specification should be met for both types of substrate. This ensured a requested minimal throwing power to be achieved, thus adequate copper thickness in through

hole from the industrial point of view.

The second set of Taguchi experiment was carried out based on the finding of the first set of DOE result. In the second set of experiment, hardware factors that could be modified in practice were analyzed. A DOE of 4 factors, two level of each were layout by a  $L_8(2^4)$  Taguchi orthogonal matrix (Table 3).

Experiment was repeated with the optimized hardware setting for verification, and simulation experiment with production hardware setting were also carried out for reference. This provided a verification, comparison and contrast of the plating performance before and after the hardware factors optimization.

#### 3.2.1 Definition of Hardware Factors

The hardware factors examined in the experiment are:

- 1. Anode cathode distance: the distance between the center line of anode bar (anode baskets) and that of the cathode bar (PCB).

- Anode distribution: the distance or spacing between each pair of adjacent anode baskets along the anode bar.

- 3. Relative anode cathode dimension: the ratio of the length of anode basket to the length of the PCB. Since the length of anode baskets was fixed, PCBs of different length were used in the experiment.

- 4. Anode geometry: the shape of the copper pallets. Copper pallets of shape that are commonly available in the market were used in the experiment.

- 5. Oscillation velocity of cathode: the oscillation frequency of cathode bar along the direction of the bar.

- Eductor orientation: the perpendicular vertical angle of the eductor jet that hit the

PCB plane.

- 7. Eductor flow rate: the flow rate of electrolyte that pumped through and magnified by the eductors.

8. Current density: the computer controlled current density of the plating equipment

## 3.2.2 Choice of Process Factors for the experiment

Although the Taguchi method was employed in the project to study the multi-factor nature PCB copper electroplating process, only eight process factors were chosen due to the limitations of the experimental set up and the project duration. These eight factors were reported to have significantly effect on copper thickness distribution and could be controlled in the newly designed industrial plating system. The total number of experiments carried out based on the eight process factors was 58. Pulse plating parameters (such as current waveform and duty cycle) are known to be other important factors affecting the plating quality, but the number of experiments will be increased tremendously if they are considered, and it is unable to finish the experiments within the project period. Eductor agitation is also an important factor affecting the quality of plating deposition, and there are continuous research efforts in the PCB manufacturing industry to improve the eductor design. In this project, the design of the new industrial tank only allows the change of eductor orientation at the bottom of the plating tank and the flowrate. A new plating tank must be designed if

other eductor agitation parameters have to be studied.

| Н      | H  | H2 | H3   | Н3 | HI   | H2  | НЗ | HI | H2         | H    | H2 | H3   | H2 | Н3 | H    | H2 | H3 | HI |

|--------|----|----|------|----|------|-----|----|----|------------|------|----|------|----|----|------|----|----|----|

| 9      | GI | G2 | G3   | G3 | G1   | G2  | G2 | 63 | <u>G</u> 1 | . G2 | 63 | G1   | 63 | 15 | G2   | Gl | G2 | G3 |

| F      | F1 | F2 | F3   | F2 | F3 . | F1  | F3 | F1 | F2         | F2   | F3 | F1   | F1 | F2 | F3   | F3 | F1 | F2 |

| 3      | 13 | E2 | E3 . | E2 | E3   | E1  | 13 | E2 | E3         | E3   | El | E2 . | E3 | EI | E2   | E2 | E3 | El |

| Q      | IQ | D2 | D3   | DI | D2   | D3  | D2 | D3 | DI         | D3   | DI | D2   | D2 | D3 | DI   | D3 | DI | D2 |

| С      | CI | C2 | ည    | CI | C2   | £2. | C1 | C2 | C3         | Ü    | C2 | .C3  | Cl | C2 | C3   | CI | CZ | C3 |

| В      | B1 | B1 | B1   | B2 | B2   | B2  | B3 | ВЗ | B3         | B1   | B1 | B1   | B2 | B2 | B2   | B3 | B3 | B3 |

| А      | Al | Al | Al   | A1 | A1   | A1  | Al | A1 | Al         | A2   | A2 | A2   | A2 | A2 | A2 · | A2 | A2 | A2 |

| Factor | -  | 2  | 3    | 4  | 5    | 9   | 7  | 8  | 6          | 10   | 11 | 12   | 13 | 14 | 15   | 16 | 17 | 18 |

Table 3.1 Taguchi DOE L<sub>18</sub>(2<sup>1</sup>x3<sup>7</sup>) Matrix

|                    | Level              |                    |                   |  |  |  |  |

|--------------------|--------------------|--------------------|-------------------|--|--|--|--|

| Factors            | 1                  | 2                  | 3                 |  |  |  |  |

| A. Anode           | A1 - Spherical     | A2 – cylindrical   | /                 |  |  |  |  |

| Geometry           |                    | /12 Cylliditeal    |                   |  |  |  |  |

| B. Anode           | B1 – 2"            | D2 2"              | B3 - 4"           |  |  |  |  |

| Distribution       | D1 - 2             | B2 - 3"            |                   |  |  |  |  |

| C. Anode Cathode   | C1 –12"            | C2 12"             | C3 – 14"          |  |  |  |  |

| Distance           | C1 -12             | C2 - 13"           |                   |  |  |  |  |

| D. Relative Anode- |                    |                    |                   |  |  |  |  |

| cathode            | D1 - 23.5"/20"     | D2 - 23.5"/22"     | D3 - 23.5"/24"    |  |  |  |  |

| Dimension          |                    |                    |                   |  |  |  |  |

| E. Oscillation     | E1 – 10 cycles/min | F2 121/i           | E3 – 14cycles/min |  |  |  |  |

| Velocity           | 151 – 10 cycles/mm | E2 – 12 cycles/min |                   |  |  |  |  |

| F. Eductor         | F1 – 0°            | F2 (7.5%)          | F3 – 15°          |  |  |  |  |

| Orientation        | F1 - U             | F2 - (7.5°)        |                   |  |  |  |  |

| G. Eductor Flow    | G1 50 gal/min      | G2 60 col/esi-     | C2 701/ :         |  |  |  |  |

| rate               | G1 – 50 gal/min    | G2 – 60 gal/min    | G3 – 70 gal/min   |  |  |  |  |

| H. Current Density | H1 - 13ASF         | H2 - 18ASF         | H3 - 23ASF        |  |  |  |  |

Table 3.2 Parameter levels summary

|          | Anode<br>Distribution | Cathode Oscillation | Eductor     | Eductor Flow |  |

|----------|-----------------------|---------------------|-------------|--------------|--|

| <u> </u> | Distribution          | Velocity            | Orientation | rate         |  |

| 1 .      | B1                    | E2                  | F1          | G2           |  |

| 2        | B1 .                  | . E2                | F1          | G3           |  |

| 3        | B1                    | E3                  | F2          | G2           |  |

| 4        | B1                    | E3                  | F2          | G3           |  |

| 5        | B2                    | E2 .                | F2          | G2           |  |

| 6        | B2                    | E2                  | F2          | G3           |  |

| 7        | B2                    | E3                  | F1          | G2           |  |

| 8        | B2                    | E3                  | F1          | G3           |  |

Table 3.3 Taguchi L<sub>8</sub>(2<sup>4</sup>) Matrix

### 3.3 Experimental setup

Experiments were carried out in the copper electroplating line in Topsearch Printed Circuit (Shenzhen) Ltd. The plating line (Figure 3.1) was manufactured by Protek Technology Ltd. and the production line is equipped with the Dutch Reverse Pulse Rectifiers (Figure 3.2). The cross section design drawing of the electroplating cell is also presented in Figure 3.3.

The experiments were carried out with MacDermid pulse plating chemical PPR1 and the bath components were maintained and measured according to the specification of the chemical from MacDermid in Topsearch.

Figure 3.1 The Protek Pulse Plating line

Figure 3.2 Dutch Reverse Pulse Plating Rectifier

The chemical bath was processed with carbon treatment to remove organic chemical by-products for every 54 experiments, or on a weekly basis, whichever

come first.

The experimental copper electroplating tank was designed and integrated at the end of the production line in such a way that:

- 1. The position of the anode bar can be manually relocated; Marking was used on the tank walls in order to define the anode-cathode distance.

- 2. The anode baskets attached on the anode bar can be manually relocated for testing different anode distribution/separation along the anode bar.

- 3. The two series of eductors at the bottom can be adjusted in a planar rotational motion to provide different emerging angle of chemical 'jets' from the eductors to the cathode.

- 4. A pump with adjustable flow rate was installed and connected to the eductors to provide different eductor flow rates, and flow-meters were connected to the eductors to measure the eductor flow rate.

- 5. Frequency controller was installed to the motor responsible for cathode oscillation to vary the cathode oscillation velocity.

Both micro-sectioning and Coating Measuring Instrument (CMI, Model CMI 500 series) technique were employed to collect deposition thickness data. Three

the copper deposition thickness. The copper thickness data obtained from cross section analysis was used primarily in the study while the CMI data was collected for reference. Hole wall copper thickness data was also collected in order to provide a reference from industrial process point of view. The cross sections were inspected and measurements were taken with a Leica microscope (Model DMIRM) with 25 to 200x magnification, equipped with measuring software (DC100 and IM50).

Draw NO. 1:20 lookdown main view Ħ Metambal Scale Unit ₹.C view 4 S Ø Cu Pletting Tapk Drawing NO. 9 9 9 8.02 Number Ð Abode Spray Tenk NO. Name Draw NO. Approved By: ⊟₽ Checked By: Drawing By: Design III): 血 Ð Ф PVC. EEC.B ф 몺 F 2. Anode materials is copper ball in Ti beakets in 101.6mm;

2. Anode material is copper ball in Ti beaket;

3. Anode-Cathode Distince is 316mm;

4. Oscilitation Frequency of Cathode is 14cycles per minute;

5. Relative Anode-Cathode Dimension is 23.5inches/24/schee;

6. Eduction Orientation is 7.54eg;

7. Eductor Orientation is 7.54eg;

8. Current Density is ; 血 ⊕\_⊕\_⊕\_⊕\_⊕\_⊕\_ Ф  $19 \times 203$ 20 x 164.5 -- 18 x 203 37 4 - 4140 -Drein pipe ф Ti Beskot Bductor cathode φ Ф **□** cuitaway view ф 285 0901

Figure 3.3 Drawing of the Plating Tank

## 4. Result

Although the Taguchi methodology was employed for the study, the number of experiments carried out was large because a total of eight process factors were studied together. In order to provide a better understanding and validity, the evolution nature of the Taguchi method was employed and the investigation was divided into two different phases

4.1 Enhancement of Plating Process Factors with Taguchi Methodology – Phase I

# 4.1.1 Taguchi Mean Response Analysis

The effect of each factor could be more clearly investigated and reported by the mean response analysis according to the Taguchi methodology. The mean response of the hardware factors in the experiment was studied according to the standard deviation of the thickness across the cathode (PCB substrates) bar. The mean response of each factor was resulted from the average of the respond of the sample factor levels under the same experimental conditions.

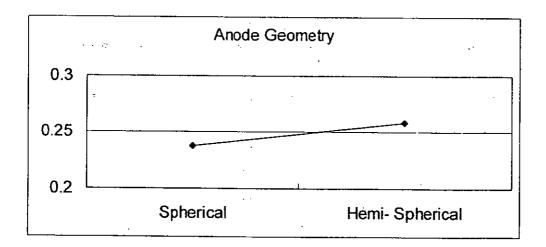

#### 4.1.1.1 Anode Geometry

It was found from the experiment that the two different anode geometries levels were having a significant effect on the deposition evenness (Figure 4.1). Spherical copper pallets in anode basket for electroplating resulted in a smaller standard deviation of deposition thickness. The mean response standard deviation was improved from 0.2585 to 0.2374 mil when spherical copper pallets were used instead of hemi-spherical copper pallets as the anode material.

Figure 4.1 Mean Response of Hardware Factor - Anode Geometry

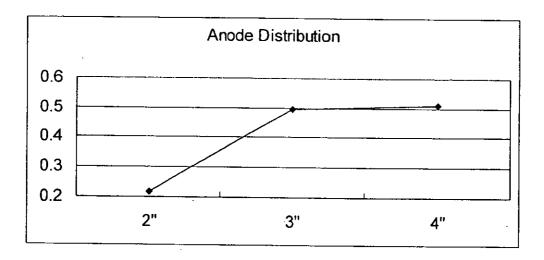

#### 4.1.1.2 Anode Distribution

It was found from the experiment that the mean response of anode distribution differed significantly between the factor levels. The best response was located at when the anode baskets were distribution by 2 inches from each other. The mean standard

Page 69

deviation was reduced from about 0.5mil when 3 and 4 inches anode basket separation were used to 0.2085mil when the anode basket separation was reduce to 2 inches (Figure 4.2).

Figure 4.2 Mean response of hardware factor - Anode Distribution

# 4.1.1.3 Anode Cathode Distance

It was found from the experiment that the smallest mean standard deviation of deposition thickness was located when the anode-cathode distance was at 12.44 inches (316mm) (Figure 4.3). This was a setting which is very close to that of the mass production 12.99 inches (330mm). The smallest standard deviation was 0.2085mil when the anode-cathode distance was set at 12.44 inches (316mm). The standard deviation then increased to 0.2342mil when the distance increased to 366mm. It decreased back to 0.2185mil when the distance was further increased to 416mm.

This was very interesting since it was believed commonly in the industry that deposition evenness can be improved when the distance between anode and cathode increases.

Figure 4.3 Mean response of hardware factor - Anode Cathode Distance

# 4.1.1.4 Relative Anode Cathode Dimension

It was found from the experiment that when the length of cathode was similar to that of the anode, the mean response standard deviation of deposition thickness was the smallest among the three different settings. The standard deviation of deposition thickness decreased from about 0.25mil to0.2033mil when the length of the cathode was increasing and approaching the length of the anode.

Figure 4.4 Mean response of hardware factor – Relative Anode Cathode Dimension

## 4.1.1.5 Cathode Oscillation Velocity

It was found from the experiment that an optimal point was located when the oscillation velocity of the cathode bar was at 12 cycles/min. However, the differences between the three mean standard deviations were not significant. The smallest standard deviation when the oscillation velocity was at 12 cycles/min was 0.2137 mil while the maximum found among the three settings was 0.2248mil.

Figure 4.5 Mean response of hardware factor – Cathode Oscillation Velocity

## 4.1.1.6 Eductor Orientation

It was found from the experiment that when the perpendicular emerging angle of the eductor jet to the cathode was set at 0 degree, the mean standard deviation of deposition thickness was the smallest. The smallest deviation value at 0 degree was found to be 0.2048mil. The standard deviation increased while the emerging angle to the cathode increased. The mean response deposition thickness standard deviation at 15 degree was 0.2308mil.

Figure 4.6 Mean response of hardware factor – Eductor Orientation

#### 4.1.1.7 Eductor Flowrate