#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

## THE HONG KONG POLYTECHNIC UNIVERSITY THE DEPARTMENT OF APPLIED PHYSICS

# STUDY OF HfAIO HIGH-k GATE DIELECTRIC THIN FILMS ON COMPRESSIVELY STRAINED Si<sub>1-x</sub>Ge<sub>x</sub>

CURREEM, SALMAN KIN KEE

#### A THESIS SUBMISSION IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF PHILOSOPHY IN PHYSICS

August, 2006

#### **CERTIFICATE OF ORGINALITY**

I hereby declare that this thesis is my own work and that, to the best of my knowledge and belief, it reproduces no material previously published or written nor material which has been accepted for the award of any other degree or diploma, except where due acknowledgement has been made in the text.

#### Abstract

To find a suitable high-k dielectric material in replacing SiO<sub>2</sub> as gate dielectric is an urgent demand in the advanced complementary metal-oxide-semiconductor (CMOS) technology. However, the carrier mobility degradation due to the high-k gate dielectric induced phonon and Coulomb scattering effect limits the application of high-k gate dielectric materials. Compressively strained Si<sub>1-x</sub>Ge<sub>x</sub> (SiGe) surface channel may serve as a solution to the carrier mobility degradation problem. However, interfacial reaction, in particular the GeO<sub>x</sub> formation and Ge diffusion that result in large amount of interfacial traps and charge traps in the dielectric, is a main issue. On the other hand, HfAlO is a promising high-k gate dielectric as substitute for SiO<sub>2</sub> due to its thermodynamic stability and low leakage current. In this project, synthesis and characterizations of HfAlO thin films on SiGe are studied. The reactions at the film-SiGe interface and the corresponding electrical properties of the MOS capacitors are investigated.

The HfAlO high-k gate dielectric thin films were grown on compressively strained Si<sub>1-x</sub>Ge<sub>x</sub> (x=17%) by pulsed-laser deposition (PLD) technique. Structural and electrical properties of the films were investigated by x-ray photoemission spectroscopy (XPS), high-resolution transmission electron microscopy (TEM), and measurements of high-frequency (1MHz) capacitance-voltage (C-V), conductance-voltage (G-V) and leakage current-voltage (G-V).

The ratio of Hf/Al in the HfAlO films, oxygen partial pressure and substrate temperature during film growth, and post-growth thermal annealing temperature are important factors to the film and interfacial properties. The results revealed that the ratio of Hf/Al affects the flat-band voltage shift of the MOS capacitors, and thus the density of fixed charges and charge traps in the dielectric films. Low oxygen partial pressure results in extremely thin interfacial layer, while high oxygen pressure results in thicker

I

interfacial layer. The post-growth thermal annealing is also found to be critical to the interfacial reaction. The optimized condition for the HfAlO film growth has been achieved.

In order to study the merit of HfAlO compared to HfO<sub>2</sub>, interfacial reactions and electrical properties of HfO<sub>2</sub> and HfAlO high-k gate dielectric films on strained SiGe fabricated by PLD are investigated. It is found that HfAlO films can reduce GeO<sub>x</sub> formation and reduce Ge segregation at the interfacial layer during the film annealing process. Such suppression effect is attractive since it can reduce defects and degradations, and thus improve the carrier mobility. In addition, the suppression of GeO<sub>x</sub> formation by utilizing the Si-cap on SiGe layer is investigated, and it revealed a more significant suppression effect when both HfAlO dielectric and Si-cap were associated.

### List of Publications

#### Journal Paper:

1 K. K. S. Curreem, P. F. Lee, K. S. Wong, J. Y. Dai, M. J. Zhou, J. Wang, and Q. Li, "Comparison of interfacial and electrical characteristics of HfO<sub>2</sub> and HfAlO high-k dielectrics on compressively strained Si<sub>1-x</sub>Ge<sub>x</sub>" Appl. Phys. Lett. 88, 182905 (2006).

#### Conference Paper:

2 K. K. S. Curreem, P. F. Lee, J. Y. Dai, "Effects of oxygen partial pressure on structural and electrical characteristics of HfAlO high-k gate dielectric grown on strained SiGe by pulsed-laser deposition" (accepted for publication to Materials Science in Semiconductor Processing on June 2006)

### Acknowledgements

I would like to thank my chief supervisor, Dr. J.Y. Dai for his constant guidance, support and patience throughout the course of the research work, and for establishing the project which I found interested and useful. I would also like to acknowledge Dr. Q. Li from the Department of Physics at the Chinese University of Hong Kong who have contributed valuable advice and resources to the success of this project. Special thank is extended to Mr. P.F. Lee, who is my fellow worker and good friend, for his extremely helpful assistance and valuable discussion in the period.

Sincere thanks must be given to many good friends (in no particular order). Mr. W.F. Wong (Sam), Mr. C.H. Ho (Michael), Mr. S.W. Cheung (Wai), Mr W.L. Shin (Stephen), Mr. T.L. Chen (Lam 2), Miss W.Y. Chung (Winnie), Miss P.S. Liu (Bessie), Mr. W.K. Tam (Leo), Mr. K.S. Wong (Sun), Mr. H. Li (Henry) and Mr. H.T. Wong (Kobe) gave me the spiritual support and provided me constant assistance and encouragement.

I gratefully acknowledge the financial support from Hong Kong Research Grants Council grant (No. B-Q722).

I struggled so long if I should insert His name in this thesis because I afraid this work may disgrace His name. Nevertheless, I finally decided to do so because I have tried my best. My heavenly Father, the greatest shepherd, the Lord of the lords and the King of the kings, thank you for your constant guidance and protection in all of the time. May your name be glorified as you are deserved! In Jesus name I pray. AMEN!

The last but not least, I would like to express my great appreciation to my beloved one, Miss K.W. Hau (*Gloria*) and our parents, without their patient support and endless love, completion of this thesis would not have been possible.

### Table of Content

| AbstractI                                                               |

|-------------------------------------------------------------------------|

| List of PublicationsII                                                  |

| AcknowledgementsIII                                                     |

| Table of ContentIV                                                      |

| List of Figure CaptionsV                                                |

| List of Table CaptionsVI                                                |

| Chapter 1 Introduction1                                                 |

| 1.1 Why high-k gate dielectrics? 1                                      |

| 1.2 High-k dielectrics as alternatives gate oxide4                      |

| 1.3 Why compressively strained SiGe7                                    |

| 1.4 Literature review and motivation 10                                 |

| 1.5 The scope of the thesis15                                           |

| References17                                                            |

| Chapter 2 Background Knowledge and Research Methodology 22              |

| 2.1 Deposition technique22                                              |

| 2.1.1 Ablation24                                                        |

| 2.1.2 Plasma expansion24                                                |

| 2.1.3 Deposition of ablated species on a substrate with subsequent film |

| growth25                                                                |

| 2.2 MOS physics26                                                       |

| 2.2.1 Ideal MOS structure26                                             |

| 2.2.2 Practical MOS structure 33                                                  |

|-----------------------------------------------------------------------------------|

| 2.2.2.1 Effect of interface states 34                                             |

| 2.2.2.2 Effects of surface charges and space charges35                            |

| 2.2.3 Equivalent oxide thickness (EOT) 37                                         |

| 2.2.4 Material properties consideration 38                                        |

| 2.2.4.1 Permittivity and barrier height39                                         |

| 2.2.4.2 Thermodynamic stability ······ 41                                         |

| 2.2.4.3 Interface quality43                                                       |

| 2.2.4.4 Film morphology44                                                         |

| 2.3 Research methodology44                                                        |

| 2.3.1 Structural characterizations45                                              |

| 2.3.2 Electrical characterizations48                                              |

| References49                                                                      |

| Chapter 3 Film characteristics of HfAlO gate dielectric on compressively strained |

| SiGe 51                                                                           |

| 3.1 Introduction 51                                                               |

| 3.2 Experimental details 52                                                       |

| 3.3 Results53                                                                     |

| 3.3.1 Effects of Al content in HfAlO film on its structural and electrical        |

| characteristics53                                                                 |

| 3.3.2 Effects of oxygen partial pressure on structure and electrical              |

| characteristics oh HfAlO films grown on compressively strained                    |

| SiGe58                                                                            |

|                                                                                   |

| 3.4 Discussion on electrical characterizations 69                              |

|--------------------------------------------------------------------------------|

| 3.5 Summary 70                                                                 |

| References72                                                                   |

| Chapter 4 Comparison of interfacial and electrical characteristics of HfO2 and |

| HfAlO high-k dielectrics on compressively strained SiGe                        |

| 4.1 Introduction                                                               |

| 4.2 Experimental details 75                                                    |

| 4.3 Results76                                                                  |

| 4.3.1 Suppression effects of HfAlO on GeO <sub>x</sub> formation               |

| 4.3.2 Electrical property study80                                              |

| 4.3.3 Suppression effects of Si-cap layer on GeO <sub>x</sub> formation 83     |

| 4.4 Summary 90                                                                 |

| References91                                                                   |

| Chapter 5 Conclusion and future work                                           |

### List of Figure Captions

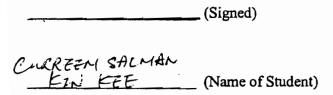

| Figure 1.1 Schematic energy band diagram of a MOS structure illustrating an      |

|----------------------------------------------------------------------------------|

| example for direct tunneling of an electron from the Si substrate                |

| through the gate oxide and reaches the gate. CB and VB are denoted as            |

| conduction band and valance band, respectively. $E_F$ is the Fermi energy        |

| of the gate electrode 2                                                          |

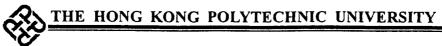

| Figure 1.2 Schematic diagram of a typical n-MOSFET (where n is denoted as        |

| n-channel in p-type semiconductor), illustrating the behavior of the             |

| MOS structure when a voltage $V_g$ is applied to the gate. The inset shows       |

| that the MOS structure can be illustrated as a parallel plate capacitor. • 3     |

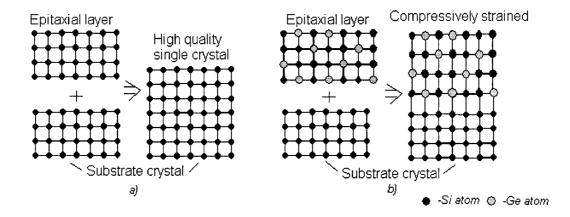

| Figure 1.3 Schematic representation of compressively strained SiGe layer 7       |

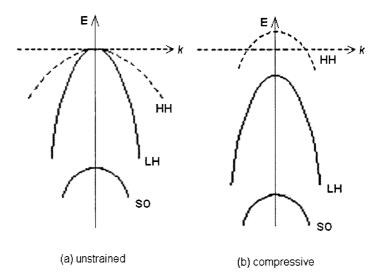

| Figure 1.4 E-k diagrams for the Si valence band under two strain conditions. The |

| shifts and deformations are schematic only and are exaggerated for               |

| emphasis 8                                                                       |

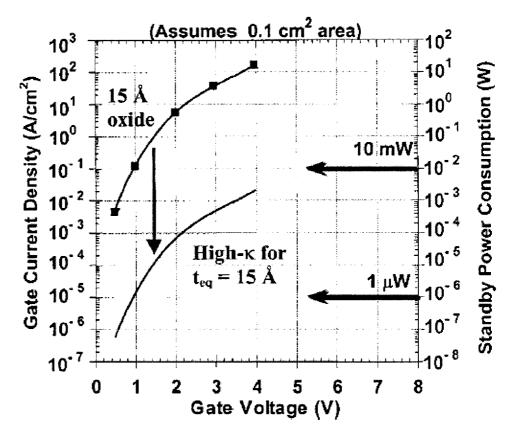

| Figure 1.5 Power consumption and gate leakage current density for a chip which   |

| has a 15 Å-thick SiO $_2$ gate dielectric compared to the potential reduction    |

| in leakage current by an alternate dielectric exhibiting the same                |

| equivalent oxide thickness. Assumes at total gate area of 0.1 cm <sup>2</sup> 11 |

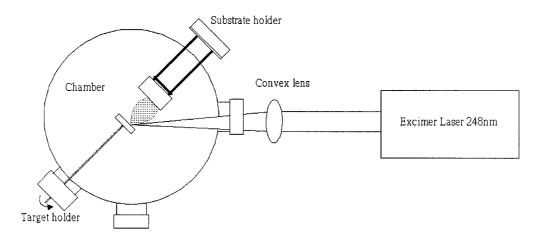

| Figure 2.1 Schematic diagram of the PLD system23                                 |

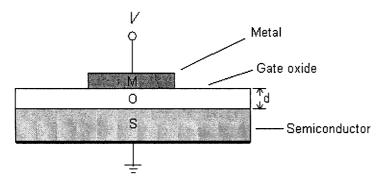

| Figure 2.2 Metal-oxide-semiconductor (MOS) structure27                           |

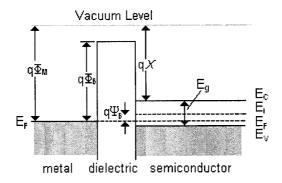

| Figure 2.3 Energy-band diagram of an ideal MOS capacitor at V=0 for p-type       |

| semiconductor 28                                                                 |

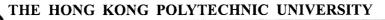

| Figure 2.4 Three different cases of the energy band diagrams for an ideal MOS       |

|-------------------------------------------------------------------------------------|

| structure when $V \neq 0$ for p-type semiconductor30                                |

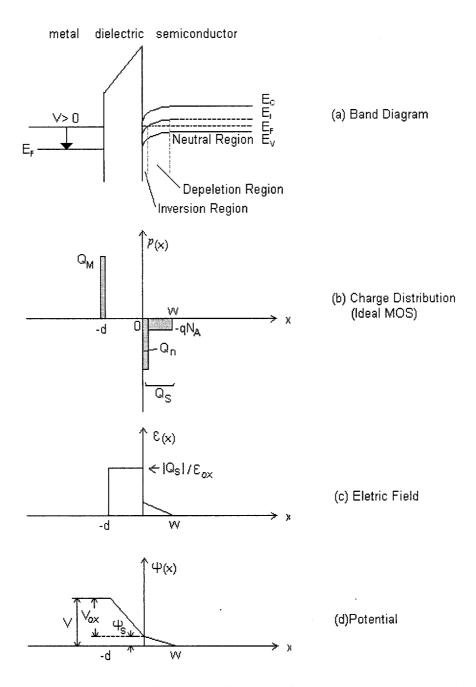

| Figure 2.5 Schematic diagram of (a) band alignment of an ideal MOS structure, (b)   |

| charge distribution under inversion condition, (c) electric field                   |

| distribution and (d) potential distribution31                                       |

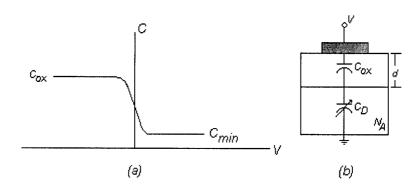

| Figure 2.6 Schematic diagram shows (a) typical MOS C-V curve sketch, (b) the        |

| equivalent circuit of series combination of the gate oxide capacitance,             |

| $C_{o\infty}$ with constant thickness d, and the semiconductor space charge         |

| capacitance C <sub>D</sub> 33                                                       |

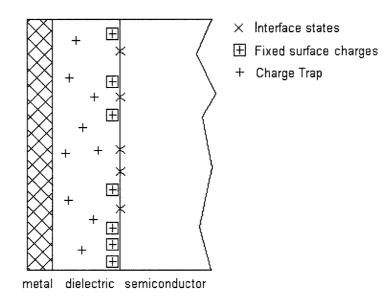

| Figure 2.7 Basic classification of states and charges in the non-ideal MOS          |

| structure 34                                                                        |

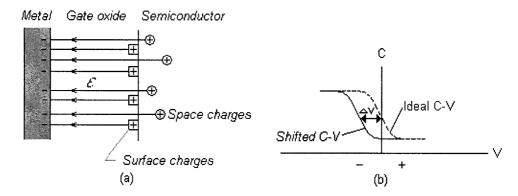

| Figure 2.8 Effect of surface charge on MOS curve36                                  |

| Figure 2.9 Schematic diagram of two parallel capacitors with different dielectrics, |

| $SiO_2$ and high-k dielectric, respectively to offer the same total                 |

| capacitance 38                                                                      |

| Figure 2.10 Band offset calculations for a number of potential high-k gate          |

| dielectric materials ······ 40                                                      |

| Figure 2.11 Ternary phase diagram for Hf-Si-O compound42                            |

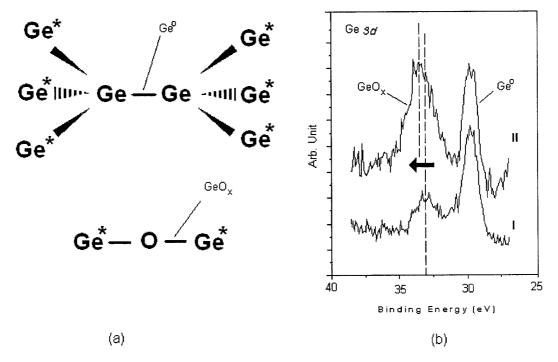

| Figure 2.12 Schematic diagram shows (a) compositions of elemental form of Ge°       |

| and $GeO_x(x<2)$ where terminating atoms, $Ge^*$ , represent the next shell         |

| of Ge atom or O atom, and (b) the corresponding peaks in the Ge 3d                  |

| core level obtained from the sample of (I) as-grown and (II) annealed, of           |

| HfAlO on SiGe by XPS47                                                              |

| Figure 2.13  | Typical MOS structure. (Identical to Fig. 2.2 with the name of the                  |

|--------------|-------------------------------------------------------------------------------------|

| di           | ifferent parts added.) ······ 48                                                    |

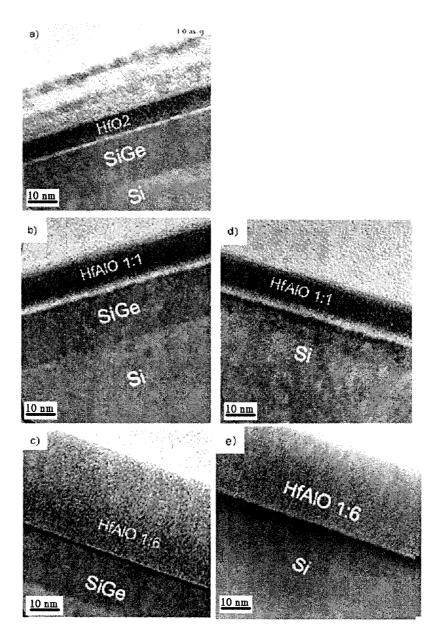

| Figure 3.1 H | IRTEM images for (a) Pure HfO $_2$ on SiGe, (b) HfAlO (1:1) on SiGe, (c)            |

| H            | IfAlO (1:6) on SiGe, (d) HfAlO (1:1) on Si, and (e) HfAlO (1:6) on Si               |

| aı           | t high vacuum before thermal annealing 54                                           |

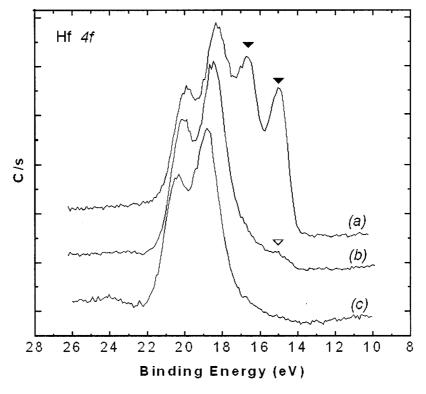

| Figure 3.2 X | XPS spectra for Hf 4f core level of as-grown samples of (a) Pure HfO <sub>2</sub> , |

| (b           | o) HfAlO (1:1) and (c) HfAlO (1:6) on SiGe. ······ 56                               |

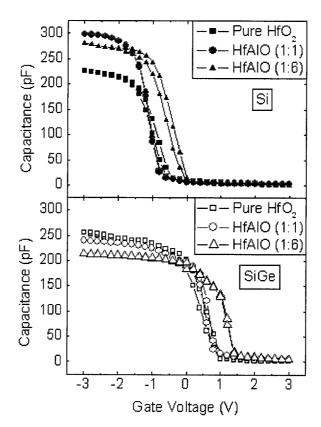

| Figure 3.3 C | C-V measurements at 1MHz of the samples of pure HfO2, HfAlO (1:1)                   |

| aı           | nd HfAlO (1:6) on Si (upper) and SiGe/Si (bottom) substrates. All                   |

| sa           | amples have been thermal annealed in $N_2$ at 650 $^{o}C$ for 45 min 57             |

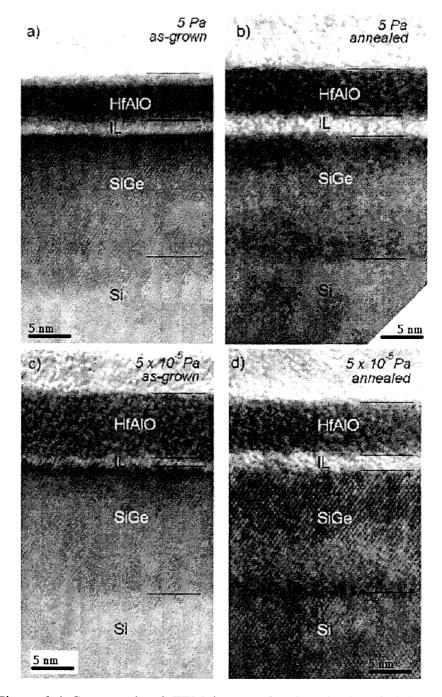

| Figure 3.4   | Cross-sectional TEM images showing the interfacial structures of                    |

| H            | fAlO (Hf:Al=1:1) films grown on SiGe/Si of (a) and (c) as-grown                     |

| sa           | imples with oxygen partial pressure of 5 Pa and $5x10^{-5}$ Pa, respectively,       |

| aı           | nd (b) and (d) are their annealed samples. ····· 59                                 |

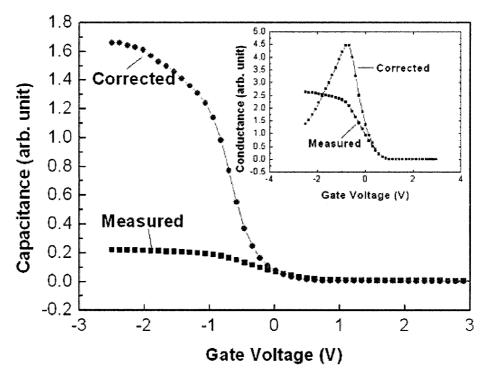

| Figure 3.5   | High frequency C-V and G-V characteristics (inset) of the MOS                       |

| st           | ructure. C-V and G-V characteristics were corrected with series                     |

| re           | sistance consideration. ······ 61                                                   |

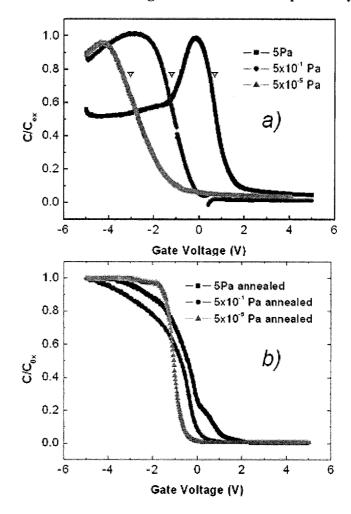

| Figure 3.6 C | C-V plots show the C-V characteristics of as-grown (a), and annealed                |

| H            | fAlO (1:1) (b), samples grown with various oxygen partial pressures. 63             |

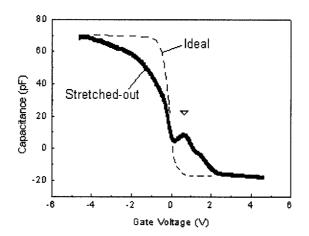

| Figure 3.7 C | -V characteristic curve affected by interface traps located at the bottom           |

| pa           | art of the SiGe bandgap ······ 66                                                   |

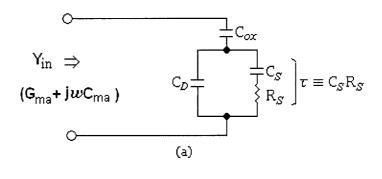

| Figure 3.8 E | Equivalent circuits include interface states effect where $C_s$ and $R_s$ are       |

| as           | sociated with surface state densities67                                             |

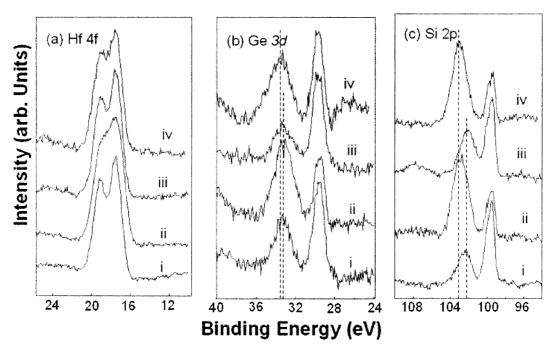

| Figure 4.1 XPS spectra of (a) Hf 4f, (b) Ge 3d and (c) Si 2p binding energies for the        |

|----------------------------------------------------------------------------------------------|

| films of (i) as-grown HfO2, (ii) annealed HfO2, (iii) as-grown HfAlO and                     |

| (iv) annealed HfAlO grown on compressively strained SiGe 77                                  |

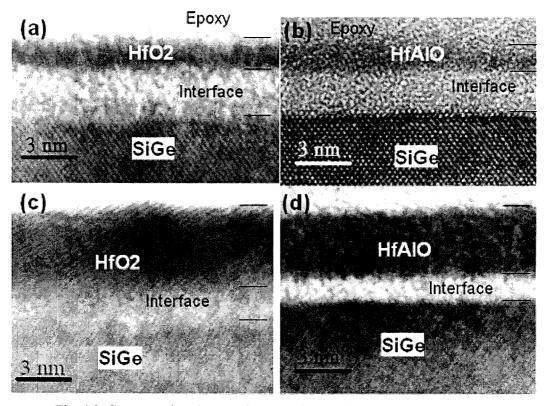

| Figure 4.2 Cross-sectional TEM images showing the interfacial structures for the             |

| annealed samples of (a) thin $HfO_2$ , (b) thin $HfAlO$ , (c) thick $HfO_2$ and (d           |

| thick HfAlO 79                                                                               |

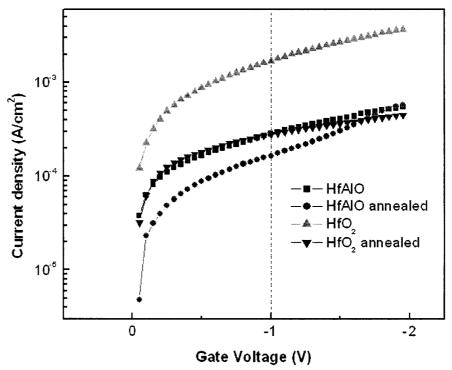

| Figure 4.3 J-V characteristics for the HfO2 and HfAlO films before and after                 |

| thermal annealing in $N_2$ ambient at 600 °C for 45 min $\cdots \sim 80$                     |

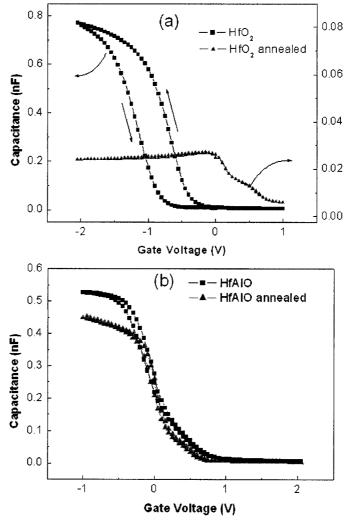

| Figure 4.4 High-frequency (1MHz) C-V characteristics for (a) HfO2 and (b) HfAlO              |

| films before and after thermal annealing81                                                   |

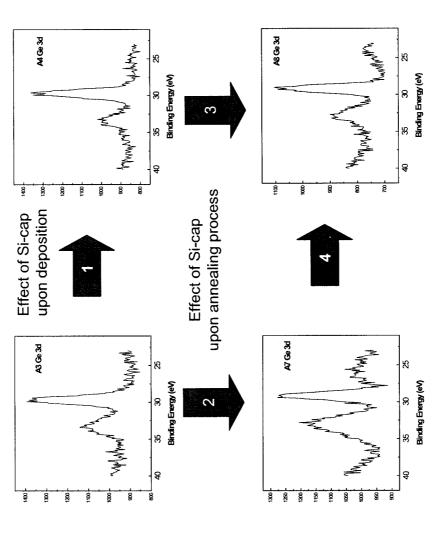

| Figure 4.5 XPS spectra of Ge 3d: (a) as-grown in oxygen gas ambient (5 Pa) of                |

| HfAlO dielectric without Si-Cap, (b) as-grown in oxygen gas ambient (5                       |

| Pa) of HfAlO dielectric with Si-Cap, and their corresponding samples                         |

| annealed at 600 °C in $N_2$ for 45 min.: (c) annealed HfAlO dielectric                       |

| without Si-Cap, and (d) annealed HfAlO dielectric with Si-Cap,                               |

| respectively 86                                                                              |

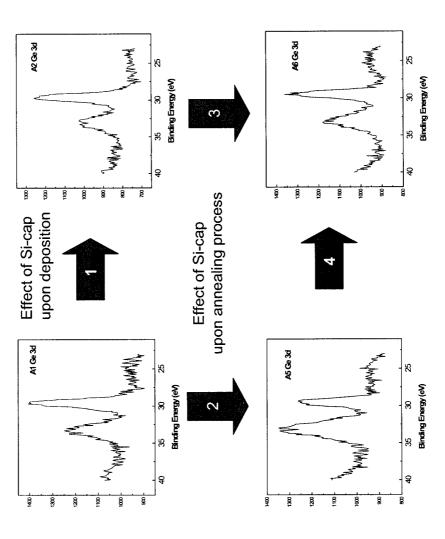

| Figure 4.6 XPS spectra of Ge 3d: (a) as-grown in oxygen gas ambient (5 Pa) of                |

| HfO2 dielectric without Si-Cap, (b) as-grown in oxygen gas ambient (5                        |

| Pa) of HfO <sub>2</sub> dielectric with Si-Cap, and their corresponding samples              |

| annealed at 600 °C in $N_2$ for 45 min.: (c) annealed $HfO_2$ dielectric                     |

| without Si-Cap, and (d) annealed HfO <sub>2</sub> dielectric with Si-Cap,                    |

| respectively 87                                                                              |

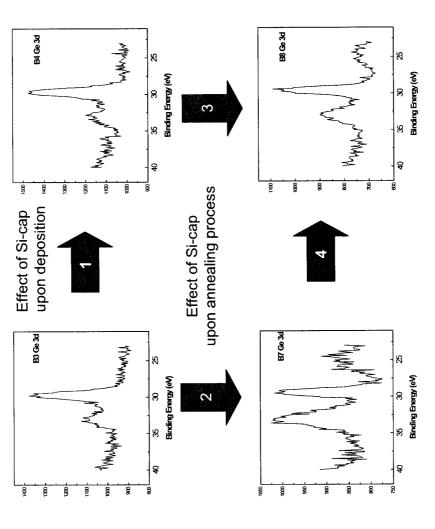

| Figure 4.7 XPS spectra of Ge 3d: (a) as-grown in oxygen gas deficient (2×10 <sup>4</sup> Pa) |

|            | of HfAlO dielectric without Si-Cap, (b) as-grown in oxygen gas ambient             |

|------------|------------------------------------------------------------------------------------|

|            | (2×10 <sup>-4</sup> Pa) of HfAlO dielectric with Si-Cap, and their corresponding   |

|            | samples annealed at 600 °C in $N_2$ for 45 min.: (c) annealed HfAlO                |

|            | dielectric without Si-Cap, and (d) annealed HfAlO dielectric with Si-Cap           |

|            | respectively 88                                                                    |

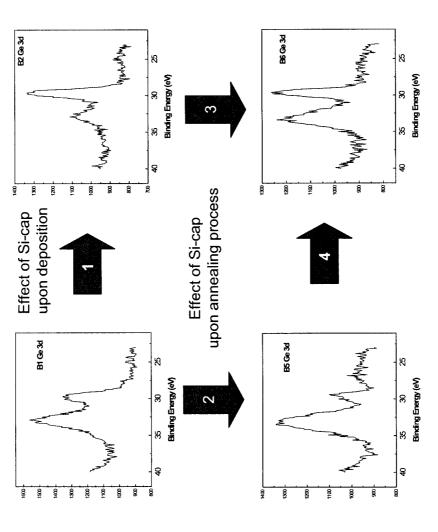

| Figure 4.8 | XPS spectra of Ge 3d: (a) as-grown in oxygen gas deficient (2×10 <sup>-4</sup> Pa) |

|            | of HfO2 dielectric without Si-Cap, (b) as-grown in oxygen gas ambient              |

|            | $(2\times10^4\ Pa)$ of $HfO_2$ dielectric with Si-Cap, and their corresponding     |

|            | samples annealed at 600 $^{o}C$ in $N_{2}$ for 45 min.: (c) annealed $HfO_{2}$     |

|            | dielectric without Si-Cap, and (d) annealed HfO2 dielectric with Si-Cap,           |

|            | respectively                                                                       |

List of Table Captions

### List of Table Captions

| Table 1.1 Comparison of relevant properties of high-k candidates      | 13 |

|-----------------------------------------------------------------------|----|

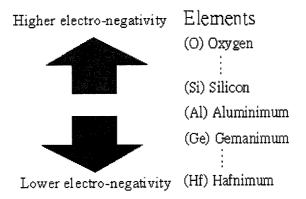

| Table 2.1 Reference of electro-negativity on various elements. ······ | 18 |

#### Chapter 1

#### Introduction

#### 1.1 Why high-k dielectrics?

The success of semiconductor industry relies on continues improvement of integrated circuit performance since the late of 1970's and the rapid progress since the late of 1980's. This improvement is achieved by continues shrinking the metal-oxide-semiconductor field effect transistor (MOSFET) in size. Indeed, the reduction of the device dimensions allows higher density of devices being integrated on Si chip, providing higher speeds and lower cost <sup>1</sup>.

One of the key elements that allowed the successful scaling of silicon-based MOSFETs is the excellent material and electrical properties of the gate dielectric in these devices: SiO<sub>2</sub>. This material indeed gives several important features that have allowed its use as gate insulator. First of all, amorphous SiO<sub>2</sub> can be thermally grown on silicon with excellent control in thickness and uniformity, and naturally forms a very stable interface with the silicon substrate. Secondly, SiO<sub>2</sub> presents an excellent thermal and chemical stability, which is essential for the complementary MOS (CMOS) process that includes annealing processes at high temperature (up to 1000 °C). A remarkable note should be pointed out is that the band gap of SiO<sub>2</sub> is very large (~9 eV), which offers excellent electrical isolation properties with large energy band offsets with the conduction and valence bands of Si. Furthermore, in modern CMOS processing, the

defect charge densities are in the order of  $10^{10}$  /cm<sup>2</sup>, and interface state densities of  $\sim 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> are routinely obtained<sup>1</sup>. All these superior properties allow the fabrication of properly working MOSFET with SiO<sub>2</sub> gate dielectric layers in past decades.

Nevertheless, as will be discussed in the next section, the improvement achieved by further aggressive down scaling of MOSFET can not withstand for the advanced CMOS technology due to the unacceptable excessive leakage current flowing through the MOS structure. In ultrathin SiO<sub>2</sub> gate dielectric, charge carriers can flow through it by direct tunneling mechanism as illustrated in Fig. 1.1.

Fig 1.1 Schematic energy band diagram of a MOS structure illustrating an example for direct tunneling of an electron from the Si substrate through the gate oxide and reaches the gate. CB and VB are denoted as conduction band and valance band, respectively.  $E_F$  is the Fermi energy of the gate electrode<sup>2</sup>.

From the electrical point of view, the MOS structure behaves like a parallel plate capacitor: when a gate voltage V is applied to the gate, the charges on the metal gate are compensated by opposite charges in the semiconductor; while the latter charges form the surface channel connecting the source (S) and drain (D) of the transistor. Figure 1.2 illustrates the typical MOSFET structure.

Fig 1.2 Schematic diagram of a typical n-MOSFET (where n is denoted as n-channel in p-type semiconductor), illustrating the behavior of the MOS structure when a voltage  $V_g$  is applied to the gate. The inset shows that the MOS structure can be illustrated as a parallel plate capacitor<sup>3</sup>.

The capacitance C of this parallel plate capacitor is given by

$$C = \frac{A\varepsilon_r}{d} (\equiv \frac{Ak\varepsilon_o}{d}),$$

1.1

where A is the capacitor area,  $\varepsilon_r$  is the permittivity of gate oxide, d is the gate thickness, k is the dielectric constant and  $\varepsilon_o$  is the permittivity of free space  $(8.85 \times 10^{-14} \text{ Fcm}^{-2})$ . From the equation (1.1), it appears that decreasing of thickness d allows us to

increase the capacitance of the parallel capacitor, and hence increase the number of charges in the surface channel for a fixed value of V. However, as pointed out above, the  $SiO_2$  layer thickness is approaching its limit which means that it can not contribute the increment of capacitance anymore. Therefore, in order to achieve the goal, an alternative way of using a gate oxide with a relatively higher dielectric constant (so-called high-k material) than that of  $SiO_2$  is proposed. As a result, one can then use a substantially thicker (physical thickness) gate layer for reduced leakage and improved gate capacitance.

#### 1.2 High-k dielectrics as alternative gate oxides

Among the potential candidates HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub> and ZrO<sub>2</sub>, etc, HfO<sub>2</sub> is considered as one of the most promising high-*k* gate dielectrics to replace SiO<sub>2</sub> due to its favorable properties including high-*k* value (*k*=25), good thermodynamic stability on Si, low leakage current (at amorphous phase) and large band gap (5.7 eV) <sup>4.7</sup>. Therefore, the HfO<sub>2</sub>/Si system has received tremendous attention. Nevertheless, it has been found recently that, pure amorphous HfO<sub>2</sub> exhibits crystallization during thermal annealing (>550 °C) and it induces grain boundaries enhanced leakage current which is unfavorable for the application. More importantly, it acts like a transparency to oxygen atom at elevated temperature<sup>8-11</sup>. Upon thermal annealing in oxygen gas ambient, oxygen atom can fast diffuse through the gate oxide and react with Si substrate forming an uncontrollable relatively low-*k* interfacial layer. This interfacial layer limits the further scaling of the equivalent oxide thickness (EOT) of HfO<sub>2</sub>.

Indeed, there is a systematic consideration (will be presented in more details in Chapter 2) of the required properties of gate dielectric, which are the key guidelines for selecting an alternative gate dielectric. Upon the examinations, almost all of the investigated high-k dielectrics, including HfO<sub>2</sub>, turned out to be favorable in some of these areas, but so far, there is almost no candidate can satisfy all respects to the guidelines. As a result, it initiates the research of other encouraging alternatives which are pseudobinary alloy systems such as  $(ZrO_2)_x(SiO_2)_{1-x}$  and  $(HfO_2)_x(SiO_2)_{1-x}$  where  $(0 \le x \le 1)^1$ . By this purpose, combination of two oxides is possible to combine the desirable properties from two different oxides and eliminate the undesirable properties of each individual material.

Several research groups (including our work) have demonstrated that HfO<sub>2</sub> alloyed with Al<sub>2</sub>O<sub>3</sub> (alumina) grown on Si is one of the potential pseudobinary system which can improve the properties<sup>8-13</sup>. They show that the new system can increase the crystallization temperature considerably which can stabilize the HfAlO dielectric in an amorphous structure up to a temperature of 1000 °C <sup>9</sup>. As Al<sub>2</sub>O<sub>3</sub> is a good barrier of oxygen, it brings this desirable property to HfAlO dielectric. Furthermore, regarding to the combination offering a reasonable value of dielectric constant (9~25) and large band offset values to Si, HfAlO is considered as a very attractive and promising alternative candidate.

Nevertheless, serious degradation of carrier mobility has been found for almost all high-k dielectrics when applied on MOSFET. It is believed that such degradation is

induced by phonon and Coulomb scattering effect upon utilizing such high-k materials grown on Si substrate<sup>14-16</sup>. It degrades the carrier mobility considerably and therefore, becomes an important issue and challenge on utilizing high-k materials into MOS transistor.

There are several approaches to solve the high-*k* material induced channel mobility degradation problem, such as utilizing Ge and strained-Si channel <sup>17,18</sup>. Compressively strained-SiGe channel (the merit of this high mobility channel will be presented in next section) is considered as another approach toward the solution. For this reason, the system of high-*k* gate dielectric of HfO<sub>2</sub> grown on compressively strained-SiGe has been considered to be a novel system, and the study on its characteristics has attracted a great deal of attention. Nevertheless, the HfO<sub>2</sub>/SiGe system meets another problem of Ge segregation and diffusion from the SiGe substrate <sup>19,20</sup>. This problem greatly affects the electrical performance because of the formation of Ge-rich layers and uncontrollable formation of GeO<sub>x</sub> inside the dielectric film and at the interface<sup>19</sup>. Such characteristics lead to high interface state density, large amount of interfacial traps, charge traps and high fixed charge density at the SiGe based MOS transistors and they should be solved.

#### 1.3 Why compressively strained SiGe?

To know the meaning of compressively strained SiGe, an illustration is given in Fig. 1.3. When an epitaxial Si film is grown on a Si substrate, Fig. 1.3(a), because there is a natural matching of the crystal lattice, it results in a high quality single crystal layer. On the other hand, when an epitaxial SiGe film is grown on a Si substrate, Fig. 1.3(b), because there is a large difference of lattice constants (lattice mismatch between Ge and Si is ~4.17 %), it forms a compressively strained SiGe layer.

Fig 1.3 Schematic representation of compressively strained SiGe layer<sup>21</sup>.

Indeed, the degree of the compressive strain depends on the size of lattice mismatch, and the size of lattice mismatch depends on the fraction of Ge in the  $Si_{1-x}Ge_x$  layer. In this thesis, compressively strained  $Si_{1-x}Ge_x$  with a fraction x equal to 0.17 was used. For convenient reason, strained SiGe will be simply used in the following

Chapters.

The merit of compressively strained SiGe channel which can offer an enhancement on hole mobility is attributed to its intrinsic electronic properties: difference in band structure (bandgap) between unstrained and strained states. Although, compressive strain in the effective channel region alters its energy level on conduction band is small (not shown), the effect on the near band edge of valence band is significantly large as illustrated in Fig.1.4. This effect has a very strong correlation to the basic property of the hole mobility.

Fig 1.4 E-k diagrams for the Si valence band under two strain conditions. The shifts and deformations are schematic only and are exaggerated for emphasis<sup>22</sup>.

Figure 1.4 is two exaggerated schematic diagrams showing the effect of compressive strain on the shift of the band alignment and the shape deformation. In unstrained material, Fig. 1.4(a), the valence band maximum is composed of three bands:

the degenerate heavy-hole (HH) and light-hole (LH) bands at k=0, and the split-off (SO) band which is slightly lower in energy. Very close proximity (44 meV) of the SO band to the top of the valence band is one of the reasons for poor hole transport properties in Si. It should be noted that the "heavy" and "light" refer to the effective masses of the holes in each band notated in Fig. 1.4.

In compressively strained material, in Fig. 1.4(b), it shows that the strain not only alters the energy bands shift but also deforms the shape of bands. The latter effect reduces the effective mass in the bands considerably and is the origin of hole mobility enhancement offered by compressively strained SiGe.

There are two points need to be noticed. First, since there is a critical thickness of strained SiGe on Si, beyond that thickness, the strain will be relaxed by forming misfit dislocations at the SiGe/Si interface. Therefore, the thickness we selected is 15 nm which is less than the critical thickness and there is no interfacial dislocations found. Second, the compressive strain in SiGe can be relaxed when it is subjected to thermal annealing at a temperature higher than 800 °C. Therefore, the process temperature in the project should be much lower than 800 °C. In addition, it is not an easy task to fabricate a high quality epitaxy SiGe film on Si without defects in the past. However, advanced fabrication techniques make this possible nowadays. In my project, the SiGe/Si wafers were fabricated by *IQE silicon compounds Co. Ltd.* based on our design.

#### 1.4 Literature review and motivation

In semiconductor industry, it is highly desirable to find a suitable high-k material to replace the currently used SiO<sub>2</sub> as the gate dielectrics in future advanced CMOS technology. Muller *et al.*<sup>23</sup> found that the full band gap of SiO<sub>2</sub> can only be obtained after at least two mono-layers of SiO<sub>2</sub>. This indicates that within two mono-layers of the Si channel interface, oxygen atoms do not have the full arrangement of oxygen neighbors and therefore can not form a full band gap that exists in the "bulk" of the SiO<sub>2</sub> film. Tang *et al.*<sup>24</sup> even set an *absolute physical thickness limit* of SiO<sub>2</sub> of 7 Å. Furthermore, with this rapid shrinking, excess leakage current becomes a serious problem. Chin *et al.*<sup>25</sup> reported that the leakage current of a Al<sub>2</sub>O<sub>3</sub> film on Si substrate with a thickness of 48 Å, which equals to an equivalent oxide thickness of 21 Å, exhibited a leakage current of  $10^{-8}$  A/cm<sup>-2</sup> at 1 V gate bias. Compared to ~ $10^{-1}$  A/cm<sup>-2</sup> for 21 Å of pure SiO<sub>2</sub>, it is seven orders of magnitude lower.

Furthermore, Fig. 1.5 shows an interesting plot reported by Brar *et al.* which demonstrates a comparison of  $SiO_2$  and high-k dielectric with respect to the current density and the power consumption as a function of gate voltage  $^{26}$ . The  $SiO_2$  curve is measured while the curve representing the high-k dielectric is calculated. The curve for a high-k film has shown about four orders of magnitude reduction on leakage current and four orders of magnitude lower power consumption than that of  $SiO_2$ . They clearly suggested the essential calling of a gate dielectric with a permittivity higher than that of  $SiO_2$  to meet the low-power application requirements.

Fig. 1.5 Power consumption and gate leakage current density for a chip which has a 15 Å-thick  $SiO_2$  gate dielectric compared to the potential reduction in leakage current by an alternate dielectric exhibiting the same equivalent oxide thickness. Assumes at total gate area of  $0.1 \text{ cm}^2$  <sup>26</sup>.

Recent publications proposed that  $HfO_2$  is a very promising alternative dielectric material to work with Si substrate<sup>4,6,27</sup>. However, poor interfacial stability induced degradation of the channel mobility in  $HfO_2/Si$  system was reported. This poor interfacial stability was interpreted to be caused by the incapable properties of  $HfO_2$ , nearly transparency to oxygen and low crystallization temperature were suggested to be two of those  $^{13,28,29}$ .

In year 2000, J. Robertson and his co-workers have reported one of the most influencing theoretical calculations on the electrical and relevant properties of various potential high-k materials (as illustrated in Table 1), and some of the most fundamental and crucial requirements for the selection guidelines were provided with clear explanations. One of the most important requirements they have emphasized is that, the electron barrier or conduction band (CB) offset is one of the key criteria in the selection of a gate oxide, and it must be over 1 eV in order to give adequately low leakage current. Those guidelines directly eliminate most of the high-k materials.

It agitates, however, an increasing interest to use multilayer or compounds of two-oxide dielectric of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> in order to improve the dielectric properties and interfacial stability with Si <sup>30</sup>. Al<sub>2</sub>O<sub>3</sub> is probably the only material that has a band gap (~8.8 eV) and band alignment similar to those of SiO<sub>2</sub>, and it is a good barrier to oxygen and ionic transport. On the other hand, HfO<sub>2</sub> has a relatively high-*k* value of ~25 and relatively small band gap (~5.7 eV). Compensative characteristics for the composite of HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> were well studied by various groups <sup>9,29,31,32</sup>. They have demonstrated that the adding of Al<sub>2</sub>O<sub>3</sub> into HfO<sub>2</sub> can retard the crystallization of pure HfO<sub>2</sub> up to 1000 °C and evidenced that the composite is thermodynamic stability on Si interface. Li and his co-worker found that both the thermal stability and the resistance to oxygen diffusion of HfO<sub>2</sub> are improved by adding Al, and they stated that the improvement is closely correlated with the Al percentage in the films <sup>9</sup>. The finding from M.H. Cho and his co-workers also suggested that the thermal stability of HfAlO films is largely depended on the incorporation of Al<sub>2</sub>O<sub>3</sub> into the HfO<sub>2</sub> film<sup>33</sup>. Therefore, it is possible to

achieve high-k dielectric oxide with high thermal stability as well as high band gap using a composite of these two oxides.

Table 1.1 Comparison of relevant properties of high-k candidates

| Material                       | Dielectric constant (k) | Band gap<br>E <sub>g</sub> (eV) | $\Delta E_{c}$ (eV) to Si | Crystal structure(s)          |

|--------------------------------|-------------------------|---------------------------------|---------------------------|-------------------------------|

| SiO <sub>2</sub>               | 3.9                     | 8.9                             | 3.2                       | Amorphous                     |

| Al <sub>2</sub> O <sub>3</sub> | 9                       | 8.8                             | 2.8                       | Amorphous                     |

| $Y_2O_3$                       | 15                      | 5.6                             | 2.3                       | Cubic                         |

| $La_2O_3$                      | 30                      | 4.3                             | 2.3                       | Hexagonal, cubic              |

| Ta <sub>2</sub> O <sub>5</sub> | 26                      | 4.5                             | 1-1.5                     | Orthorhombic                  |

| TiO <sub>2</sub>               | 80                      | 3.5                             | 1.2                       | Tetragonal (rutile, anatase)  |

| $HfO_2$                        | 25                      | 5.7                             | 1.5                       | Monoclinic, tetragonal, cubic |

| ZrO2                           | 25                      | 5.8                             | 1.4                       | Monoclinic, tetragonal, cubic |

Calculated by Robertson. Ref 30

Nevertheless, the charge carrier mobility degradation in the field effect transistor channel due to the high-*k* dielectric induced phonon and charge scattering effect limits the implementation of high-*k* gate dielectrics in the advanced CMOS technology <sup>16,17,19,34</sup>. It has been noticed recently that the use of the enhanced hole mobility of strained SiGe surface channel may be a way to overcome the mobility degradation problem. Z.H. Shi and his co-workers have reported that 36% drive current enhancement for compressively strained Si<sub>0.8</sub>Ge<sub>0.2</sub> over Si was exhibited for PMOSFETs with physical channel length down to 180 nm <sup>18</sup>. The physical channel length down to 70 nm was also reported by them as 17% drive current enhancement was achieved. The

faction (x) in the  $Si_xGe_{1-x}$  under investigation by many research groups is ranged from 0.15-0.3, and all of the results clearly demonstrated that using strained SiGe channel is a good method to solve the hole mobility issue in high-k gate transistor <sup>14,17,18,20</sup>.

Therefore, it is potentially attractive to use this high mobility channel of compressively strained SiGe together with high-k gate dielectrics. However, the conventional thermal oxidation of SiGe leads formation of Ge-rich layers at the oxide/SiGe interface and causes serious degradation of oxide properties. This effect causes serious problem for use of SiGe in mainstream MOSFET devices. Some research groups have showed that an ultrathin Si-overlayer (or called Si-cap layer) on the strained SiGe shown satisfactory results on suppressing such problem caused by Ge segregation and Ge piled up at the oxide-substrate, and one of the groups has shown that Si-cap of 20 Å was effective to prevent the problem and commented that the electrical properties obtained from their samples with the Si-cap were superior to those without the Si-cap  $^{17}$ .

Most recently, there were many investigations focused on the thermal stability of HfO<sub>2</sub> dielectric on SiGe epitaxial layer <sup>16,17,19,34</sup>. In contrast, to the best of our knowledge, there are few reports demonstrating that HfAlO can serve as a solution to the degradations when applied on SiGe surface channel MOSFET by its compensated and superior properties <sup>8</sup>.

In this thesis, I carried out the study of synthesis and characterization of HfAlO

ultrathin films on compressively strained SiGe. The ratio of Hf/Al in the HfAlO films, oxygen partial pressure and substrate temperature during film growth, and post-growth thermal annealing were studied, and the importance of each of the above parameters was revealed. In addition, the comparison between HfAlO and HfO<sub>2</sub> on the interfacial reactions and electrical properties was carried out. Suppression effects on interfacial reaction were demonstrated, indicating the superior of using HfAlO gate dielectric over pure HfO<sub>2</sub>. Furthermore, the suppression effect was also demonstrated upon utilizing an ultrathin Si-cap layer (~9 Å) on the compressively strained SiGe.

#### 1.5 The scope of the thesis

In <u>Chapter 1</u>, the driving force to implement high-k dielectrics in MOSFET and the motivation (with literature review) to study the HfAlO on compressively strained SiGe channel are introduced.

Background knowledge of synthesis and characterization of HfAlO ultrathin films on compressively strained SiGe will be presented in <u>Chapter 2</u>. In particular, pulsed-laser deposition (PLD) technique, MOS physics and various structural characterization techniques such as x-ray photoemission spectroscopy (XPS) will be introduced.

<u>Chapter 3</u> presents the investigation results of structural and electrical property dependence on the ratio of Hf/Al in the HfAlO films, oxygen partial pressure and

substrate temperature during film growth, and post-growth thermal annealing temperature. It also presents a discussion section on electrical characterization such as capacitance-voltage (C-V) and conductance-voltage (G-V).

<u>Chapter 4</u> focuses on the comparison study between HfAlO and HfO<sub>2</sub> on the interfacial reactions and electrical properties when implemented on SiGe. Suppression effects of HfAlO, in comparison with HfO<sub>2</sub>, to the GeO<sub>x</sub> formation at the interface, and the effect of ultrathin Si-cap layer on SiGe are presented.

In the last chapter--<u>Chapter 5</u>, a conclusion of this thesis and proposed future work will be presented.

### References

- G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations", J. Appl. Phys. 89, 5243-5275 (2001).

- M. Houssa, "High-k gate dielectrics", p.6 (2004).

- M. Houssa, "High-k gate dielectrics", p.8 (2004).

- H. Wong, N. Zhan, K. L. Ng, M. C. Poon, and C. W. Kok, "Interface and oxide traps in high-k hafnium oxide films", Thin Solid Films **462-63**, 96-100 (2004).

- J. Kim, S. Kim, H. Jeon, M. H. Cho, K. B. Chung, and C. Bae, "Characteristics of HfO<sub>2</sub> thin films grown by plasma atomic layer deposition", Appl. Phys. Lett. 87, 053108 (2005).

- J. Y. Dai, P. F. Lee, K. H. Wong, H. L. W. Chan, and C. L. Choy, "Epitaxial growth of yttrium-stabilized HfO<sub>2</sub> high-k gate dielectric thin films on Si", J. Appl. Phys. **94**, 912-915 (2003).

- M. S. Kim, Y. D. Ko, M. S. Yun, J. H. Hong, M. C. Jeong, J. M. Myoung, and I. G. Yun, "Characterization and process effects of HfO<sub>2</sub> thin films grown by metal-organic molecular beam epitaxy", Mat. Sci. Eng. B-Solid **123**, 20-30 (2005).

- K. K. S. Curreem, P. F. Lee, K. S. Wong, J. Y. Dai, M. J. Zhou, J. Wang, and Q. Li, "Comparison of interfacial and electrical characteristics of HfO<sub>2</sub> and HfAlO high-k dielectrics on compressively strained Si<sub>1-x</sub>Ge<sub>x</sub>", Appl. Phys. Lett. **88**, 182905 (2006).

- H. Y. Yu, N. Wu, M. F. Li, C. X. Zhu, B. J. Cho, D. L. Kwong, C. H. Tung, J. S. Pan, J. W. Chai, W. D. Wang, D. Z. Chi, C. H. Ang, J. Z. Zheng, and S. Ramanathan, "Thermal stability of (HfO<sub>2</sub>)<sub>(x)</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>(1-x)</sub> on Si", Appl. Phys. Lett. 81, 3618-3620 (2002).

- H. Y. Yu, M. F. Li, B. J. Cho, C. C. Yeo, M. S. Joo, D. L. Kwong, J. S. Pan, C. H. Ang, J. Z. Zheng, and S. Ramanathan, "Energy gap and band alignment for (HfO<sub>2</sub>)<sub>(x)</sub>(Al2O<sub>3</sub>)<sub>(1-x)</sub> on (100) Si", Appl. Phys. Lett. **81**, 376-378 (2002).

- P. F. Lee, J. Y. Dai, K. H. Wong, H. L. W. Chan, and C. L. Choy, "Study of interfacial reaction and its impact on electric properties of Hf-Al-O high-k gate dielectric thin films grown on Si", Appl. Phys. Lett. 82, 2419-2421 (2003).

- M. H. Cho, D. W. Moon, S. A. Park, Y. K. Kim, K. Jeong, S. K. Kang, D. H. Ko, S. J. Doh, J. H. Lee, and N. I. Lee, "Interfacial characteristics of N-incorporated HfAlO high-k thin films", Appl. Phys. Lett. 84, 5243-5245 (2004).

- V. Mikhelashvili, R. Brener, O. Kreinin, B. Meyler, J. Shneider, and G. Eisenstein, "Characteristics of metal-insulator-semiconductor capacitors based on high-k HfAlO dielectric films obtained by low-temperature electron-beam gun evaporation", Appl. Phys. Lett. 85, 5950 (2004).

- C. K. Maiti, S. Maikap, S. Chatterjee, S. K. Nandi, and S. K. Samanta, "Hafnium oxide gate dielectric for strained-Si<sub>1-x</sub>Ge<sub>x</sub>", Solid. State. Electron. **47**, 1995-2000 (2003).

- G. K. Dalapati, S. Chatterjee, S. K. Samanta, and C. K. Maiti, "Electrical characterization of low temperature deposited TiO<sub>2</sub> films on strained-SiGe layers", Appl. Surf. Sci. **210**, 249-254 (2003).

- J. H. Lee, S. Maikap, D. Y. Kim, R. Mahapatra, S. K. Ray, Y. S. No, and W. K. Choi, "Characteristics of ultrathin HfO<sub>2</sub> gate dielectrics on strained-Si<sub>0.74</sub>Ge<sub>0.26</sub> layers", Appl. Phys. Lett. **83**, 779-781 (2003).

- S. H. Jeong, Y. Roh, N. E. Lee, and C. W. Yang, "Effects of annealing temperature on the characteristics of silicate/HfO<sub>2</sub> insulator formed on the p-Si/Si<sub>0.8</sub>Ge<sub>0.2</sub> and p-Si/Si<sub>0.8</sub>Ge<sub>0.2</sub>/intrinsic-Si (20 Å) substrates", Surf. Coat. Tech. **200**, 258-263 (2005).

- Z. H. Shi, D. Onsongo, and S. K. Banerjee, "Mobility and performance enhancement in compressively strained SiGe channel PMOSFETs", Appl. Surf. Sci. 224, 248-253 (2004).

- T. J. Park, S. K. Kim, J. H. Kim, J. Park, M. J. Cho, S. W. Lee, S. H. Hong, and C. S. Hwang, "Electrical properties of high-k HfO<sub>2</sub> films on Si<sub>1-x</sub>Ge<sub>x</sub> substrates", Microelectron. Eng. 80, 222-225 (2005).

- J. F. Damlencourt, O. Weber, O. Renault, J. M. Hartmann, C. Poggi, F. Ducroquet, and T. Billon, "Study of HfO<sub>2</sub> films deposited on strained Si<sub>1-x</sub>Ge<sub>x</sub> layers by atomic layer deposition", J. Appl. Phys. **96**, 5478-5483 (2004).

- J. Singh, "Electronic and optoelectronic properties of semiconductor structures", p.29 (2003).

- P. J. Briggs, A. B. Walker, and D. C. Herbert, "Calculation of hole mobilities in relaxed and strained SiGe by Monte Carlo simulation", Semicond. Sci. Tech. 13, 680-691 (1998).

- D. A. Muller, T. Sorsch, S. Moccio, F. H. Baumann, K. Evans-Lutterodt, and G. Timp, "The electronic structure at the atomic scale of ultrathin gate oxides", Nature 399, 758-761 (1999).

- S. Tang, R. M. Wallace, A. Seabaugh, and D. King-Smith, "Evaluating the minimum thickness of gate oxide on silicon using first-principle method", Appl. Surf. Sci. 135, 197 (1998).

- <sup>25</sup> A. Chin, C. C. Liao, C. H. Liu, W. J. Chen, and C. Tsai, Tech. Dig. VLSI Symp., p.135 (1999).

- B. Brar, G. D. Wilk, and A. C. Seabaugh, "Direct extraction of the electron tunneling effective mass in ultrathin SiO<sub>2</sub>", Appl. Phys. Lett. **69**, 2728-2730 (1996).

- T. H. Moon, M. H. Ham, M. S. Kim, I. Yun, and J. M. Myoung, "Growth and characterization of MOMBE grown HfO<sub>2</sub>", Appl. Surf. Sci. **240**, 105-111 (2005)

- D.Y. Cho, K.S. Park, B.H. Choi, and S.J. Oh, "Control of silicidation in HfO<sub>2</sub>/Si(100) gate stack", Appl. Phys. Lett. **86**, 041913 (2005).

- D. Wu, J. Lu, E. Vainonen-Ahlgren, E. Tois, M. Tuominen, M. Ostling, and S. L. Zhang, "Structural and electrical characterization of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> on strained SiGe", Solid State Electron. **49**, 193-197 (2005).

- J. Robertson, "Band offsets of wide-band-gap oxides and implications for future electronic devices", J. Vac. Sci. Technol. B 18, 1785-1791 (2000).

- S. J. Ding, C. X. Zhu, M. F. Li, and D. W. Zhang, "Atomic-layer-deposited  $Al_2O_3$ -HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> dielectrics for metal-insulator-metal capacitor applications", Appl. Phys. Lett. 87, 053501 (2005).

- X. Y. Qiu, H. W. Liu, F. Fang, M. J. Ha, and J. M. Liu, "Phase separation and interfacial reaction of high-k HfAlO<sub>x</sub> films prepared by pulsed-laser deposition in oxygen-deficient ambient", Appl. Phys. Lett. 88, 072906 (2006).

- M. H. Cho, H. S. Chang, Y. J. Cho, D. W. Moon, K. H. Min, R. Sinclair, S. K. Kang, D.

H. Ko, J. H. Lee, J. H. Gu, and N. I. Lee, "Change in the chemical state and thermal stability of HfO<sub>2</sub> by the incorporation of Al<sub>2</sub>O<sub>3</sub>", Appl. Phys. Lett. 84, 571-573 (2004).

# THE HONG KONG POLYTECHNIC UNIVERSITY

T. C. Chen, L. S. Lee, W. Z. Lai, and C. W. Liu, "The characteristic of HfO<sub>2</sub> on strained SiGe", Mat. Sci. Semicon. Proc. **8**, 209-213 (2005).

# Chapter 2

# **Background Knowledge and Research Methodology**

In Chapter 2, background knowledge about the film growth technology, metal-oxide semiconductor (MOS) physics and characterization methods will be introduced. In particular, I will introduce the following three parts: (1) Principles and methods of pulsed-laser deposition which is the main growth technique in this project; (2) Basic knowledge about the MOS device, which is fundamental theory in our basic consideration when selecting alternative gate dielectrics and assessing a dielectric/substrate system; (3) Structural and electrical characterization methods.

#### 2.1 Deposition technique

Pulsed-laser deposition (PLD) technique is considered as one of the most flexible technique to offer a large freedom of choice in target materials, ablation characteristics, ambient gas and its pressure, and substrate temperature. All these parameters influence film structure and properties. It is especially attractive for research on novel dielectrics due to its short cycle time and one can easily investigate a wide range of different materials and compositions at a relatively low operation temperature. For these reasons, it satisfied our desires on investigating the potentially attractive composite of HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> high-*k* gate dielectrics with different Hf:Al atomic ratios. In addition, the compressive strain in the SiGe epitaxial layer can be maintained during the low deposition temperature. Regarding to MOS transistor application with high-*k* materials,

controlling the thickness and roughness of the thin films down to an atomic scale is crucial.

Figure 2.1 shows the schematic diagram of a PLD system consisted with a vacuum chamber, a temperature controllable substrate holder, and target material. An excimer laser with wavelength of 248 nm is placed outside the vacuum chamber.

Fig 2.1 Schematic diagram of the PLD system.

The physical processes involved in PLD are rather complicated despite its ease of operation. The PLD process can be divided into three stages: (1) ablation, (2) plasma expansion, and (3) deposition of ablated species on a substrate with subsequent film growth. All stages are indeed important in understanding the relationship between film deposition condition and the resulting film properties.

#### 2.1.1 Ablation

The PLD process starts with the ablation of the target material. A couple of hundred high-power laser pulses irradiate the target during the deposition of a thin film of around 10 nm. When the high power and tightly focused laser pulses irradiate the target, photon energy is absorbed by the target surface inducing target-laser interaction with a thermal cycle. Photon energy absorption generates thermal energy and this thermal energy conducts into a certain depth of a localized area and causes localized material melting. Indeed, the process is highly dependent on the laser fluence, the absorption coefficient, thermal conductivity of specific target and the target surface characteristics such as the film stoichiometry and its roughness. When this thermal energy cannot be fully dissipated through thermal conduction, the local temperature rises rapidly. Once it reaches the material's evaporation temperature, material is dissociated and ablated out from the target.

#### 2.1.2 Plasma expansion

For the second stage, the vaporized material including ions, electrons, molecules and neutral atoms started to expand into surrounding ambient gas driven by the pressure gradient. The dynamic flow of these energetic particles constitutes luminous plasma which is called a plume. This plume is highly dependent on the ambient pressure: a divergent plume is the result when film is deposited in high vacuum, while convergent plume is the result when film is deposited in poor vacuum. Due to the plume dimension dependence on the background pressure, it raises the importance of target-to-substrate

distance in the deposition process. P.E. Dyer and his co-workers<sup>1</sup> have shown that  $E/P_o$  is the scaling parameter for the plume length, where E is the laser-pulse energy, and  $P_o$  is the background gas pressure.

Our frequently used ambient gas is oxygen gas and the use of it is mainly to compensate the loss of a constituent. The oxygen pressure mainly affects the oxygen content in the deposited thin film. For example, the deposited oxide thin film tends to suffer from oxygen vacancy defects when the deposition is done in oxygen gas deficient. Therefore, more understanding of these interrelation parameters is crucial to determine the general growth condition and to understand the film's structural and electrical characteristics.

#### 2.1.3 Deposition of ablated species on a substrate with subsequent film growth

The ablated material will finally reach the substrate surface and, consequently a layer of film will be deposited. In this stage, the surface temperature of the substrate is the key parameter which offers the ablated species mobility through several atomic distances on the surface for sticking to favorable sites. The substrate temperature is also one of the key parameters to determine the ultimate structure of the films: epitaxial, polycrystalline or amorphous. Of course, films with different structure have their own specific uses. For the high-k dielectric in MOS transistor application, in order to avoid the grain boundary induced current leakage in polycrystalline structure, an amorphous structure is rather preferable. In amorphous films, no crystalline structure can be

identified.

Above is the brief introduction for the three physical processes involved in the PLD, and indeed every single physical process can be expanded into a chapter to discuss. However, it is not the scope for this thesis. One can clearly see that PLD involves various deposition parameters, and each of them can strongly affect and determine the film properties. Once we acquire the understanding on each parameter and the experience on handling them, various structures can be fabricated.

#### 2.2 MOS physics

#### 2.2.1 Ideal MOS structure

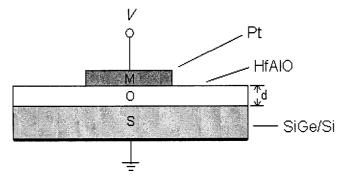

A MOS structure is shown in Fig. 2.2, where d is the thickness of the gate oxide and V is the applied voltage on the metal gate electrode. Indeed, both the interfaces of metal/oxide and oxide/semiconductor are important to the device performance. In this thesis, we will particularly focus on the latter interface. This oxide/semiconductor interface, which is usually about  $\sim$ 5 Å thick, serves as a transition between the atoms associated with the materials in the gate oxide and semiconductor. As will be discussed, this interface region can considerably alter the overall characteristics of the MOS capacitor.

Fig 2.2 Metal-oxide-semiconductor (MOS) structure<sup>2</sup>.

Figure 2.3 shows an energy band diagram of an ideal MOS capacitor (p-type semiconductor) for V=0 where  $\Phi_M$  is the metal work function,  $\chi$  is the semiconductor electron affinity,  $E_g$  is the semiconductor band gap,  $\Phi_B$  is the potential barrier between the metal and dielectric, and  $\Psi_B$  is the potential difference between the Fermi level  $E_F$  and the intrinsic Fermi level  $E_I$ . An ideal MOS capacitor is defined as three points:

(1) At zero applied voltage, there is no energy difference between  $\Phi_M$  and the semiconductor work function  $\Phi_S$  or the work function difference  $\Phi_{MS}$  is zero, i.e.

$$\Phi_{MS} \equiv \Phi_M - \left(\chi + \frac{E_g}{2q} + \Psi_B\right) = 0, \qquad (2.1)$$

In other words, the band is flat (flat-band condition) when there is no applied V.

Fig 2.3 Energy-band diagram of an ideal MOS capacitor at V=0 for p-type semiconductor<sup>3</sup>.

- (2) The only charges which can exist in the structure under any biasing conditions are those in the semiconductor and those with the equal but opposite sign on the metal surface adjacent to the insulator.

- (3) There is no carriers transport through the gate oxide under dc bias condition or the resistance of the insulator is infinity.

When this ideal MOS diode is biased with positive or negative voltages, there are basically three cases which may exist at the semiconductor surface as illustrated in Fig. 2.4.

When a negative voltage (V<0) is applied to the metal gate, Fig. 2.4(a), the top of the valence band bends upward. Since the carrier density depends exponentially on the energy difference ( $E_F$ - $E_V$ ), this band bending causes an accumulation of majority carriers (holes) near the semiconductor

surface. For an ideal MOS capacitor, there is no current flow in the structure. So the Fermi level remains constant in the semiconductor. This is the case of "accumulation".

- (2) When a small positive voltage (V>0) is applied, Fig. 2.4(b), the bands bend downward, and the majority carriers are depleted. This is the case of "depletion".

- When a larger positive voltage is applied, Fig. 2.4(c), the bands bend even more downward such that the intrinsic level  $E_i$  at the surface crosses over the Fermi level  $E_F$ . At this point the number of electrons at the surface is larger than that of the holes, and the surface is thus inverted which is the case of "inversion". Similar results can be obtained for n-type semiconductor.

Fig 2.4 Three different cases of the energy band diagrams for an ideal MOS structure when  $V \neq 0$  for p-type semiconductor<sup>4</sup>.

Figure 2.5(a) shows a more detailed band diagram at the surface of an ideal MOS capacitor (*p*-type semiconductor) with bands bending of the semiconductor identical to that shown in Fig. 2.4 (c). Figure 2.5 (b) shows the corresponding charge distribution.

Fig. 2.5 Schematic diagram of (a) band alignment of an ideal MOS structure, (b) charge distribution under inversion condition, (c) electric field distribution and (d) potential distribution<sup>5</sup>.

For charge neutrality of the system, it is required that

$$Q_M = Q_N + qN_A W = Q_S, (2.2)$$

where  $Q_M$  is charges per unit area on the metal,  $Q_N$  is the electrons per unit area in the inversion region,  $qN_AW$  is the ionized acceptors per unit area in the space-charge region with space-charge width W, and  $Q_s$  is the total charges per unit area in the semiconductor. Figure 2.5(c) and (d) show the electric field and the potential obtained by the first and the second integrations of Poisson's equations, respectively.

In Fig. 2.5(c), it is clear that with the absence of any work-function differences, the applied voltage will partially appear across the insulator and partially across the semiconductor. Thus

$$V = \psi_s + V_{\rm or}, \tag{2.3}$$

where  $\psi_s$  is the semiconductor surface potential and  $V_{ox}$  is the potential across the gate oxide which is given by

$$V_{ox} = \frac{Q_s}{C_{ox}}, \tag{2.4}$$

where  $C_{ox}$  is the capacitance of the gate oxide. The total capacitance, C, of the system is a series combination of the gate oxide capacitance,  $C_{ox}$ , and the depletion capacitance  $C_D$ , i.e.

$$C = \frac{C_{ox}C_D}{C_{ox} + C_D} \tag{2.5}$$

For a given dielectric thickness d, the value of  $C_{ox}$  becomes constant as illustrated in Fig. 2.6(b), while  $C_D$  is varied with V. Hence, total capacitance C is directly depended on V.

This relationship leads to an interesting quantity: threshold voltage,  $V_T$ , beyond which  $(V>V_T)$  strong inversion status begins and current starts to flow through the buried channel right below the interface. The typical C-V curve of an ideal MOS capacitor is shown in Fig. 2.6, where  $C_{min}$  is the minimum capacitance when surface depletion region occurs.

Fig. 2.6 Schematic diagram shows (a) a typical MOS C-V curve sketch, and (b) the equivalent circuit of series combination of the gate oxide capacitance,  $C_{ox}$ , with constant thickness d, and the semiconductor space charge capacitance  $C_D^6$ .

#### 2.2.2 Practical MOS structure

In practical MOS capacitor, the definitions for the ideal MOS previously presented do not hold any more. By contrast, there are many states and charges exist in the structure that affecting the ideal MOS characteristics. The basic classification of these

states and charges are shown in Fig.2.7<sup>7</sup>. They are: (1) interface states which is defined as energy levels within the forbidden band gap at the dielectric/semiconductor interface which can exchange charges with the semiconductor in a short time; (2) surface charges include immobile fixed charges, mobile ions and ionized traps which are located near of or at the semiconductor surface; and (3) space charges include the mobile ions and the ionized traps inside the dielectric.

Fig 2.7 Basic classification of states and charges in the non-ideal MOS structure<sup>7</sup>.

#### 2.2.2.1 Effect of interface states

The interface states have been theoretically studied by Tamm<sup>8</sup>, Shockley<sup>9</sup>, and others<sup>10,11</sup> showing that they exist within the forbidden gap due to the interruption of the periodic lattice structures at the surface of a crystal. This interface state is considered as

a donor state if it can be neutral or it can become positive by donating (giving up) an electron. For an acceptor interface state, it can be neutral or it can become negative by accepting an electron. When a voltage is applied, the surface potential will move up or down with the valence and conductance bands while the Fermi level remains fixed. A change of charges in the interface state occurs when it crosses the Fermi level. This change of charges will contribute to the MOS capacitance and alter the ideal MOS curve. With the help of the equivalent circuit (will be discussed in Section 3), conductance G is introduced and it is found that C-V and G-V characteristics are highly correlated to the change of charges in the surface states. Therefore, the interface state density  $D_{ii}$  can be determined from the combination of a single frequency C-V and G-V measurements using Hill's method<sup>12</sup>. The expression used for calculating the  $D_{ii}$  is given by:

$$D_{ii} = \left(\frac{2G_{\text{max}}}{qA\omega}\right) \left[\left(\frac{G_{\text{max}}}{\omega C_{ox}}\right)^{2} + \left(1 - \frac{C_{m}}{C_{ox}}\right)^{2}\right]^{-1}, \tag{2.6}$$

where  $G_{max}$  is the maximum conductance in the G-V curve with its corresponding capacitance  $(C_m)$ ,  $C_{ox}$  is the oxide capacitance,  $\omega$  is the angular frequency and A is the metal gate area of the capacitor. For SiO<sub>2</sub>/Si interface, the typical value of  $D_{it}$  is ranged in the order of magnitude of  $\sim 10^{10}$ - $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>.

# 2.2.2.2 Effects of surface charges and space charges

The surface charges include the fixed charge, mobile ions and ionized traps which are located near or at the gate-oxide/semiconductor interface; while the space charges include the mobile ions and the ionized traps in the dielectric. The fixed charge has the

following properties. It is fixed and cannot be charged or discharged over a wide variation of applied voltage. Its density  $(Q_{fc})$  is not greatly affected by the oxide thickness, while it depends on the oxidation and annealing conditions, and on the semiconductor orientation. The effect of the fixed charge is more or less similar to that of space charges on the MOS capacitance curve, which causes a parallel shift of the C-V curve along the voltage axis. The amount of the fixed charges can be calculated by the voltage shift  $(\Delta V)$  of the C-V curve:

$$Q_{fc} = \Delta V \cdot C_{ox} \quad . \tag{2.7}$$

This can be explained with the help of Fig.2.8 (a). When positive fixed surface charges are present, the electric field E in the gate-oxide is higher than the field on the semiconductor surface  $E_s$ . Therefore, more charges in the metal electrode are required to create equal but opposite charges. Consequently, a larger voltage is required to compensate them and it causes a shift of the C-V curve as illustrated in Fig.2.8 (b).

Fig. 2.8 Effect of surface charge on MOS curve<sup>13</sup>.

#### 2.2.3 Equivalent oxide thickness (EOT)

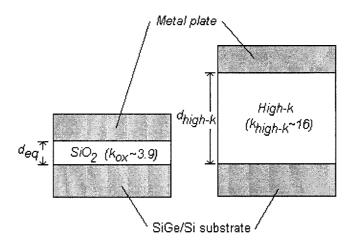

Figure 2.9 illustrates the schematic diagram of two parallel capacitors with different dielectrics, SiO<sub>2</sub> and high-k dielectric, to offer the same total capacitance. In order to increase the total capacitance by thinning SiO<sub>2</sub> dielectric (<10 Å), let's consider a parallel plate capacitor:

$$C = \frac{k\varepsilon_o A}{d},\tag{2.8}$$

where k is the dielectric constant of the material,  $\varepsilon_o$  is the permittivity of free space, A is the area of the capacitor, and d is the thickness of the dielectric. This expression for C can be rewritten in terms of  $d_{eq}$  (i.e. the equivalent oxide thickness of the high-k dielectric when it is assumed to be SiO<sub>2</sub>) and  $k_{ox}$  (=3.9, the dielectric constant of SiO<sub>2</sub>) as illustrated as equation (2.9)

$$C = \frac{k_{ox} \varepsilon_o A}{d_{ea}} \,. \tag{2.9}$$

As we have the relation of:

$$\frac{k_{ox}}{d_{eq}} = \frac{k_{high-k}}{d_{high-k}},\tag{2.10}$$

therefore, we have this equation:

$$d_{high-k} = \frac{k_{high-k}}{k_{ox}} d_{eq} = \frac{k_{high-k}}{3.9} d_{eq}, \qquad (2.11)$$

where  $k_{high-k}$  and  $d_{high-k}$  are the dielectric constant and thickness of a high-k dielectric, respectively. As a result, this relationship allows us to use a physically thicker high-k dielectric (for example  $d_{high-k} = 20$  Å) to attain an ultrathin SiO<sub>2</sub> ( $d_{eq} = 5$  Å) when  $k \sim 16$ . Therefore, the equivalent oxide thickness (EOT) for this high-k dielectric is 5 Å.

Fig. 2.9 Schematic diagram showing two parallel capacitors with two different dielectrics,  $SiO_2$  and high-k dielectric, which offer the same total capacitance.

## 2.2.4 Material properties consideration

All of the material systems discussed earlier in Chapter 1 must meet a set of criteria to perform as successful gate dielectric. We now consider a summary of the appropriate material properties for the selection of materials for gate dielectric applications.

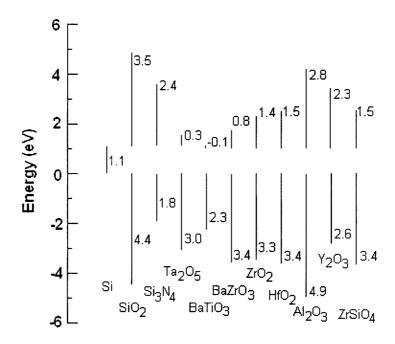

#### 2.2.4.1 Permittivity and barrier height

Selecting a gate dielectric with a high permittivity than that of SiO<sub>2</sub> is essential to improve the performance associated with the scaling of the device dimensions. For many simple oxides, permittivities have been measured on bulk samples and in some cases even on thin films (below the 10 nm-thickness regime) shown in table 1.1 from Chapter 1. But for the more complex materials, the dielectric constants may not be well known. The required permittivity must be balanced against the barrier height for the tunneling process. For electrons traveling from the Si substrate to the gate, this is the conduction band offset,

$$\Delta E_C \equiv q \left( \chi - \left( \Phi_M - \Phi_B \right) \right), \tag{2.12}$$

where the notations have identical definitions to the energy diagram shown in Fig. 2.3; while for the electron traveling from the gate to the semiconductor substrate, this is  $\Phi_B$ . This concern is a must because leakage current increases exponentially with decreasing barrier height (and thickness) for electron direct tunneling transport <sup>14</sup>. Therefore, in order to obtain low leakage current, it is desirable to find a gate dielectric that has large  $\Delta E_C$  value to the semiconductor and gate metal. Various values of  $\Delta E_C$  for dielectric-Si systems were calculated by Robertson and Chen <sup>14</sup> and are illustrated in Fig. 2.10.

Fig. 2.10 Band offset calculations for a number of potential high-k gate dielectric materials  $^{15,16}$ .

These calculations are an important insight into the potential dielectric considerations. If the experimental  $\Delta E_C$  values for these oxides are less than 1.0 eV, they will likely be excluded for being used as oxides in gate dielectric application, since electron transport would lead to unacceptable high leakage currents. Since many potential gate dielectrics do not have reported  $\Delta E_C$  values (for example HfAlO), the closest and attainable indicator of the band offset is its band gap  $(E_g)$ .

Although many researchers originally assumed that selecting a dielectric with k > 25

would be necessary to replace  $SiO_2$ , the more relevant consideration is whether the desired device performance can be obtained. It is therefore more appropriate to find a dielectric which not only provides a moderate increase in k compared to 3.9 for  $SiO_2$ , but also produces a large tunneling barrier and high-quality interface with Si. For the case of  $Al_2O_3$  (k=9) incorporated with  $HfO_2$  (k=25), the overall permittivity of this alloying is inevitably lower than that of the pure  $HfO_2$ , but this trade-off can be very favorable, for the improved stability.

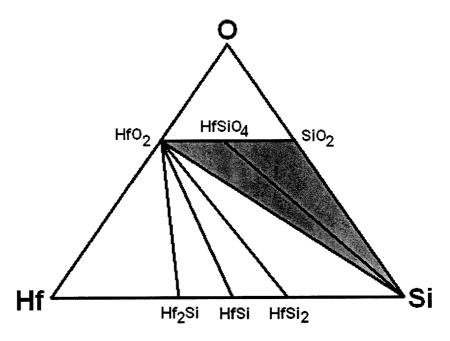

#### 2.2.4.2 Thermodynamic stability

For any thin gate dielectric/substrate systems, the interface plays a key role, and in most cases is the dominant factor in determining the overall electrical properties. Most of the systems investigated show unstable and undesirable interfaces attributed by reactions. An important approach toward predicting and understanding the relative stability of a particular three component system for device application can be explained through ternary phase diagrams<sup>17,18</sup> as illustrated in Fig. 2.11. It shows an analysis of the relevant chemical reactions for the Hf-Si-O ternary system governed by Gibbs free energies. The tie lines in the phase diagram for the Hf-Si-O system indicate that the metal oxide HfO<sub>2</sub> and the compound silicate HfSiO<sub>4</sub> will both be stable in direct contact with Si up to high temperatures. The gray shaded area denotes a large phase field of (HfO<sub>2</sub>)<sub>x</sub>(SiO<sub>2</sub>)<sub>1-x</sub> compositions which are also expected to be stable on Si up to high temperatures. Furthermore, even within the shaded area, compositions with high O levels are preferred because this will be more likely to prevent silicide phase formation.

# (%)

### **Background Knowledge and Research Methodolog**

Of course, the illustration can be extended to predict the possibility of our HfAlO/SiGe system by appropriate modifications.

Fig. 2.11 Ternary phase diagram for Hf-Si-O compound<sup>17,18</sup>.

Again, the k value of  $(HfO_2)_x(SiO_2)_{1-x}$  system are substantially lower than that of pure  $HfO_2$ , but as mentioned in previous sub-section, this trade-off for interfacial control will be acceptable as long as the resulting leakage current is low enough.

#### 2.2.4.3 Interface quality

A clear goal of any potential high-k dielectric is to attain a sufficiently high-quality interface with the substrate channel, say as close as possible to that of SiO<sub>2</sub>/Si. In fact, it is difficult to imagine any material creating a better interface than that of SiO<sub>2</sub>/Si, and typical production SiO<sub>2</sub> gate dielectric have a  $D_{it}$  of about  $10^{10}$ - $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>. Most of the high-k materials reported in the Chapter 1 show the  $D_{it}$  ranged from~ $10^{11}$  to  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. It is crucial to understand the origin of the interface properties of any high-k gate dielectric, so that an optimal high-k/SiGe interface may be obtained. Any silicide bonding which forms near the channel interface will tend to produce unfavorable bonding conditions leading to poor leakage current and poor electron channel mobility.

In order to maintain high-quality interface and channel mobility, it is expected to have no silicide phases present at or near the channel interface. Furthermore, if a metal-oxide gate dielectric has many different stable oxidation states, an extra attention should be paid because it may generate another defect of oxygen vacancies or electron trap sites at the interface. HfO<sub>2</sub> has been previously reported as having high oxygen diffusivity. This is a serious concern regarding control of the interface. Any annealing treatments which have an excess of oxygen presence will lead to rapid oxygen diffusion through the oxides, resulting in a relatively low-k interface layer and it should be forbidden.

#### 2.2.4.4 Film morphology

As discussed in Chapter 1, polycrystalline structure of gate dielectric is undesirable due to the presence of grain boundaries serving as high-leakage paths. In addition, grain size and orientation changes throughout a polycrystalline film can cause significant variations in k leading to irreproducible properties.