#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="mailto:lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

## Advanced Control of SPWM dc/ac Inverters

by

## Xiao Sun

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the Department of Electronic and Information Engineering

The Hong Kong Polytechnic University

Hong Kong SAR, China

June 2003

## CERTIFICATE OF ORIGINALITY

| I hereby declare that this thesis is my own work and that, to the best of my |

|------------------------------------------------------------------------------|

| knowledge and belief, it reproduces no material previously published or      |

| written nor material which has been accepted for the award of any other      |

| degree or diploma, except where due acknowledgement has been made in         |

| the text.                                                                    |

|           | (Signed)          |

|-----------|-------------------|

| SUN, Xiao | (Name of student) |

#### **Abstract**

# of the thesis entitled 'Advanced Control of SPWM dc/ac Inverters' submitted by Xiao Sun for the degree of Doctor of Philosophy at The Hong Kong polytechnic University at October 2002

There is a growing need for sinusoidal inverters that can supply power to nonlinear loads and still maintain precise regulation of the output voltage magnitude, phase and total harmonic distortion (THD). Also, with the ever-increasing demand for power, UPS systems may have to be paralleled to form a multi-inverter system. A multi-inverter system can have many desirable features such as N+X redundancy operation, improved reliability, modularity and expandability.

This thesis studies the control methodologies that enable inverter systems to deal with nonlinear loads and be paralleled easily with high performance. Starting with a brief introduction to the basics of sinusoidal PWM inverter in Chapter 2, neural network (NN) control of the inverters is introduced in Chapter 3. Benefited from abilities of nonlinear functional mapping and fault tolerance, simulation and experiment results show superior performance of the proposed NN controller compared with a traditional PI controller. In Chapter 4 and 5, parallel operation of multi-inverters is discussed. An instantaneous average-current-sharing scheme is modeled and analyzed in Chapter 4. Based on the model established, some key issues of the parallel multi-inverter system are discussed, including stability of the current-sharing controller, impedance characteristics and voltage regulation. A full-state feedback controller for parallel multiinverter systems based on optimal control methodology is presented in Chapter 5. Having a global view of the whole system, the proposed full-state feedback controller is easy to design. The robustness of the controller to the change of number of parallel inverters has also been investigated. The hardware implementation of the controller is simple. All modeling and theoretical analyses are verified by simulation and experiment results. Finally, suggestions for future research are addressed.

## Acknowledgements

To my family, my supervisors, my friends and all who have stood by me and helped me through the whole study and research, I would like to take this chance to express my sincere appreciation.

First of all, I would like to express my gratitude towards Prof. Y. S. Lee, my chief supervisor, for his valuable advice, patient guidance and support, which made this study possible. His immense enthusiasm and encouragement made undertaking this study a pleasure. I would also like to give my thanks to Prof. D. Xu, my second supervisor, for his supports and encouragements throughout my study. It is he who recommended me to continue my study in PolyU.

I would like to thank Dr. F.H.F. Leung, Dr. M.H.L. Chow and Dr. L.K. Wong for their constructive comments and suggestions.

I will be grateful to my colleagues in the Power Electronics Laboratory who have imparted direct assistance during the course of my study. In particular, I would like to thank Dr. K.W. Siu, Mr. Y.L. Cheng, Mr. C.P. Lee, Mr. T.M. Leung, Mr. L.P. Wong, Mr. D.C. Lu and Mr. S.H. Wong for their support and helpful discussion. It has been a very enjoyable experience working with them.

I gratefully acknowledge the Hong Kong Polytechnic University and also the Department of Electronic and Information Engineering for their financial support through my study.

Last, but not least, I must thank my parents and my sister for their endless love and support over years.

## **Contents**

| Abstract    |      |                                             | i   |

|-------------|------|---------------------------------------------|-----|

| Acknowled   | lgem | ients                                       | ii  |

| Contents    |      |                                             | iii |

| List of Fig | ures |                                             | vi  |

| List of Tab | oles |                                             | xi  |

| Chapter 1   | Int  | roduction                                   | 1   |

|             | 1.1  | Motivation                                  | 1   |

|             | 1.2  | Background                                  | 3   |

|             | 1.3  | Objectives                                  | 6   |

|             | 1.4  | Outline of the Thesis                       | 7   |

| Chapter 2   | Bas  | sics of Sinusoidal PWM dc/ac Inverters      | 9   |

|             | 2.1  | Introduction                                | 9   |

|             | 2.2  | Topologies of a dc/ac Inverter              | 9   |

|             |      | 2.2.1 Half-Bridge Inverter                  | 10  |

|             |      | 2.2.2 Full-Bridge Inverter                  | 11  |

|             | 2.3  | PWM Operation of Inverters                  | 12  |

|             |      | 2.3.1 Bipolar Switching                     | 14  |

|             |      | 2.3.2 Unipolar Switching                    | 15  |

|             | 2.4  | Linear Model of a Sinusoidal dc/ac Inverter | 18  |

|             | 2.5  | Summary                                     | 21  |

| Chapter 3 | Nei | ural N | etwork Based Control for SPWM Inverter                              | 22 |

|-----------|-----|--------|---------------------------------------------------------------------|----|

|           | 3.1 | Introd | luction                                                             | 22 |

|           | 3.2 | Feedf  | orward Neural Network                                               | 28 |

|           | 3.3 | Propo  | sed Neural Network Control of Inverter                              | 31 |

|           |     | 3.3.1  | Obtaining Example Patterns Under Linear Loading Conditions          | 31 |

|           |     | 3.3.2  | Obtaining Example Patterns Under Nonlinear Loading Conditions       | 33 |

|           |     | 3.3.3  | Training of the Neural Network                                      | 36 |

|           | 3.4 |        | ation Results, Analogue Hardware Implementation and imental Results | 38 |

|           |     | 3.4.1  | Simulation Results                                                  | 39 |

|           |     | 3.4.2  | Analogue Hardware Implementation                                    | 42 |

|           |     | 3.4.3  | Experimental Results                                                | 45 |

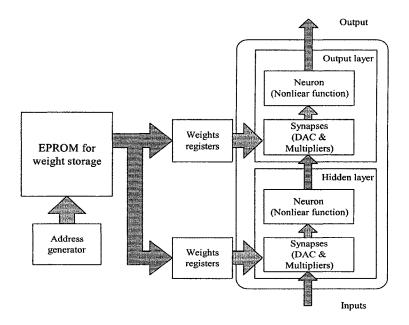

|           | 3.5 | ~      | mentation of the Proposed NN Controller Using ated Circuits         | 50 |

|           |     | 3.5.1  | EPROM                                                               | 51 |

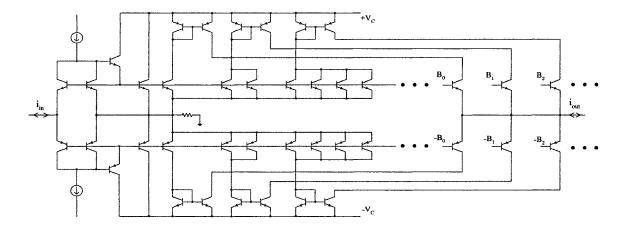

|           |     | 3.5.2  | Synapse                                                             | 51 |

|           |     | 3.5.3  | Neuron                                                              | 53 |

|           | 3.6 | Concl  | usion                                                               | 54 |

| Chapter 4 |     | _      | and Analysis of Parallel Multi-Inverter                             |    |

|           | •   |        | vith Average-Current-Sharing Scheme                                 | 55 |

|           | 4.1 |        | uction                                                              |    |

|           | 4.2 | -      | n Configuration of Parallel Multi-Inverter System                   |    |

|           | 4.3 | Mode   | ling of Parallel Multi-Inverter System                              |    |

|           |     | 4.3.1  | Model of a Single dc/ac Inverter                                    |    |

|           |     | 4.3.2  | Model of Parallel Multi-Inverter Systems                            |    |

|           | 4.4 | Analy  | sis and Simulations                                                 | 67 |

|           |     | 4.4.1  | Current-Sharing Controller                                          | 68 |

|           |     | 4.4.2  | Impedance Characteristics                                           | 77 |

|           |     | 4.4.3  | Voltage Regulation                                                  | 82 |

|           | 4.5 | Exper  | imental Results                                                     | 83 |

|           | 4.6 | Concl  | usion                                                               | 92 |

| Chapter 5   | A State Feedback Controller for Parallel M<br>Inverter Systems | Aulti–<br>93 |

|-------------|----------------------------------------------------------------|--------------|

|             | 5.1 Introduction                                               | 92           |

|             | 5.2 Modeling of a Multi-Inverter System                        | 9            |

|             | 5.3 Optimal Control                                            | 9            |

|             | 5.3.1 Augmented System                                         | 9            |

|             | 5.3.2 Solving for the Riccati Equation                         | 100          |

|             | 5.3.3 Relationship Between Performance Index Performance       |              |

|             | 5.3.4 Minimize Circulating Current                             | 102          |

|             | 5.4 Design Example and Simulation                              | 103          |

|             | 5.4.1 Design Step                                              | 103          |

|             | 5.4.2 Simulations                                              | 100          |

|             | 5.5 Robustness of the Proposed Controller                      | 109          |

|             | 5.5.1 Current Sharing                                          | 110          |

|             | 5.5.2 Voltage Regulation                                       |              |

|             | 5.5.3 Simulations                                              | 114          |

|             | 5.6 Experimental Results                                       |              |

|             | 5.7 Conclusion                                                 | 120          |

| Chapter 6   | <b>Conclusions and Suggestions for Future research</b>         | 122          |

|             | 6.1 Contributions of the Thesis                                | 122          |

|             | 6.2 Suggestions for Future Research                            | 124          |

| Appendix A  | A                                                              | 127          |

| Appendix l  | 3                                                              | 133          |

| Appendix (  |                                                                | 134          |

| Publication | S                                                              | 136          |

| References  |                                                                | 137          |

## **List of Figures**

| Figure 2.1 | Single-phase Sinusoidal PWM inverter                                                                                                    | 10   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.2 | Half-bridge inverter.                                                                                                                   | 11   |

| Figure 2.3 | Full-bridge inverter.                                                                                                                   | 12   |

| Figure 2.4 | Bipolar pulse-width modulation.                                                                                                         | 14   |

| Figure 2.5 | Unipolar pulse-width modulation.                                                                                                        | 16   |

| Figure 2.6 | Full-bridge inverter with LC filter.                                                                                                    | 18   |

| Figure 2.7 | Sinusoidal PWM                                                                                                                          | 19   |

| Figure 2.8 | Equivalent circuit of the averaged sinusoidal PWM inverter                                                                              | 20   |

| Figure 2.9 | Linearized model of sinusoidal PWM inverter.                                                                                            | 21   |

| Figure 3.1 | Structure of an artificial neuron.                                                                                                      | 29   |

| Figure 3.2 | Structure of a two layer feedforward neural network showing the back propagation training.                                              | 30   |

| Figure 3.3 | Multiple feedback loop control scheme to obtain example patterns under linear loads                                                     | 32   |

| Figure 3.4 | Idealized load current feedback control scheme to obtain example patterns under nonlinear loads                                         | 34   |

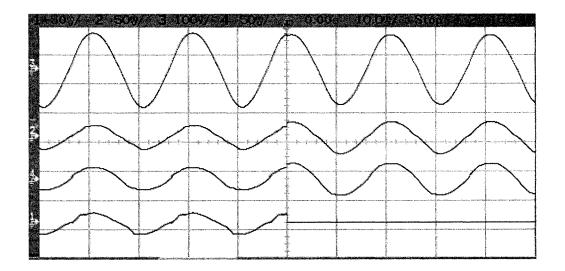

| Figure 3.5 | Example waveform of idealized load-current feedback control scheme.                                                                     | 35   |

| Figure 3.6 | Proposed neural network control scheme for UPS inverter.                                                                                | .39  |

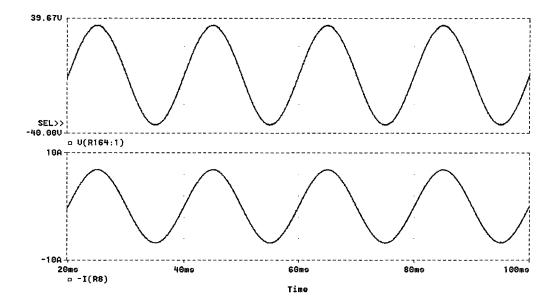

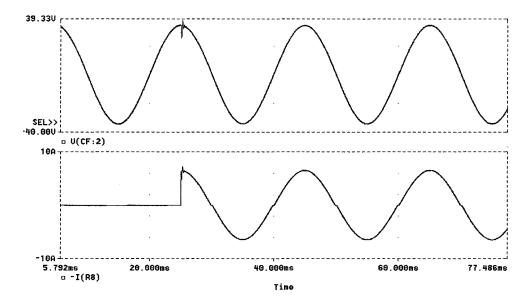

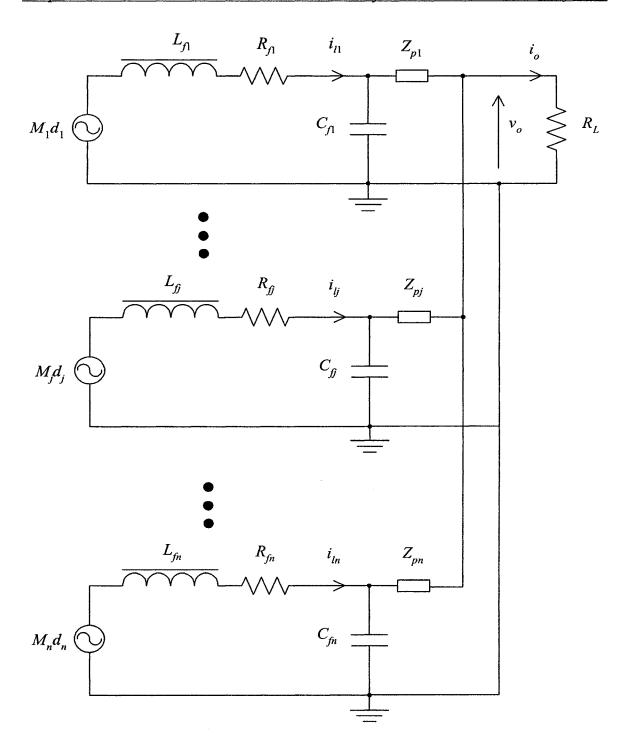

| Figure 3.7 | Simulation result of the steady-state response of the proposed NN controlled UPS inverter for full resistive load ( $5\Omega$ )         | . 41 |

| Figure 3.8 | Simulation result of the transient response of the proposed NN controlled UPS inverter when the load changes from no load to full load. | .41  |

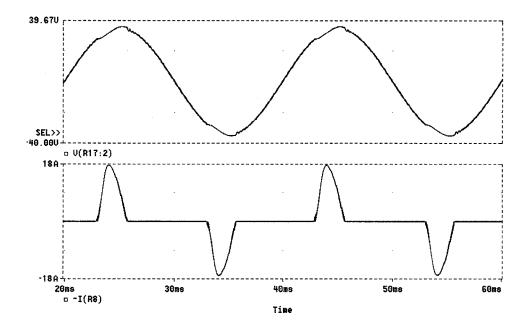

| Figure 3.9  | Simulation result of the proposed NN controlled UPS inverter for a full-wave diode bridge rectifier load (3200 $\mu$ F 10 $\Omega$ )                                      |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.10 | An analog circuit realization of the proposed NN controller43                                                                                                             |

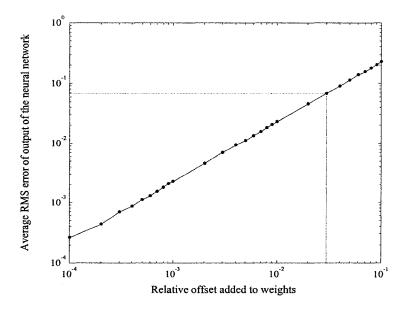

| Figure 3.11 | Effect of limited precision in the weights44                                                                                                                              |

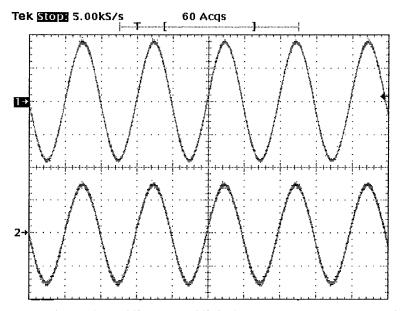

| Figure 3.12 | Experimental result of the steady-state response of the proposed NN controlled UPS inverter for full resistive load (5 $\Omega$ )46                                       |

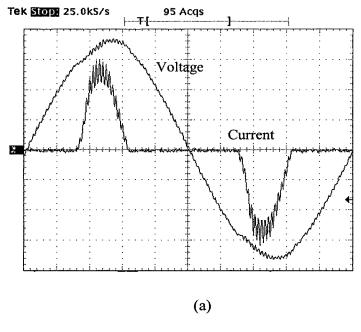

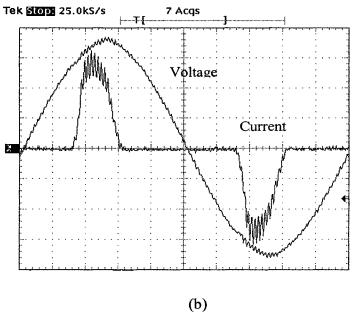

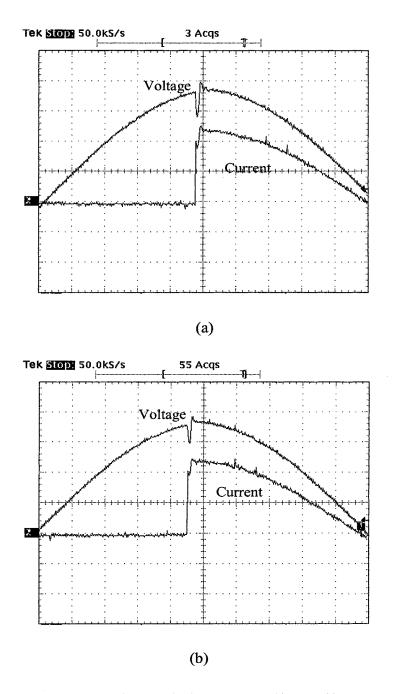

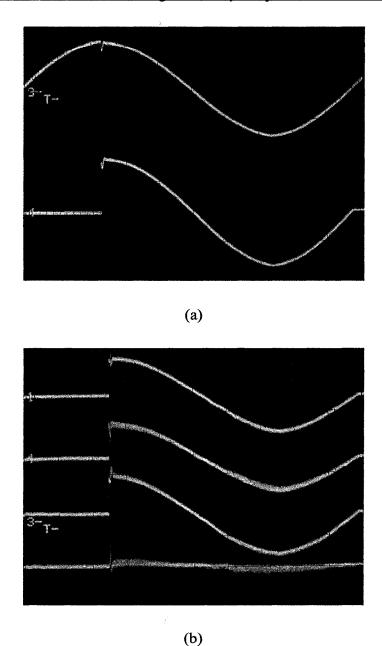

| Figure 3.13 | Experimental result for a full-wave diode bridge rectifier load $(3200\mu F\ 10\Omega)$ (a). The PI controlled UPS inverter; (b). The proposed NN controlled UPS inverter |

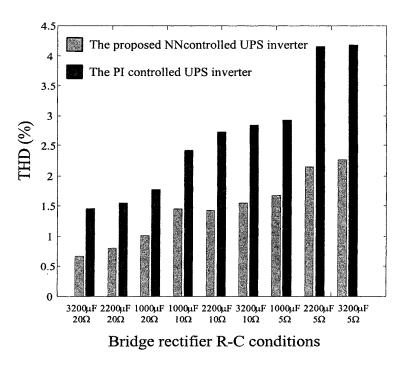

| Figure 3.14 | The THD of the output voltage for bridge rectifier loads feeding different R-C loads                                                                                      |

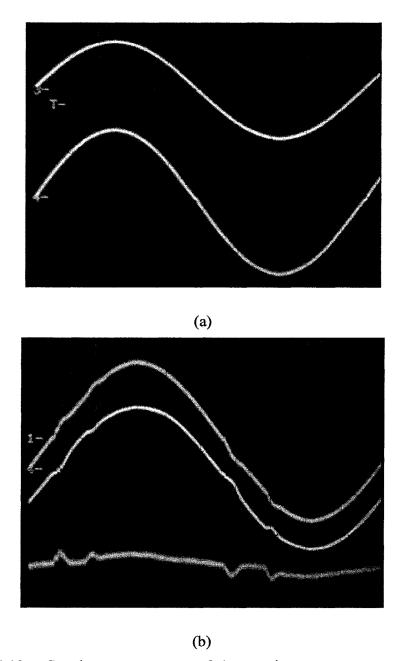

| Figure 3.15 | Experimental results with a step-change of load from no load to $5\Omega$ (a). The PI controlled UPS inverter; (b). The proposed NN controlled UPS inverter.              |

| Figure 3.16 | Block diagram of the integrated circuit implementation of the proposed NN controller                                                                                      |

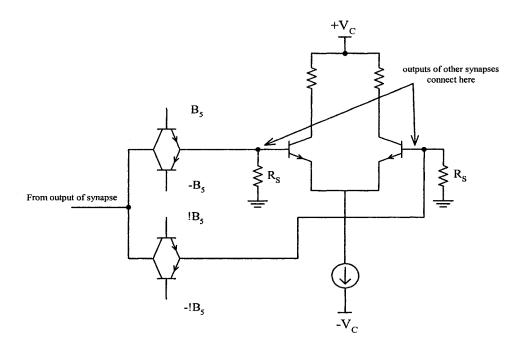

| Figure 3.17 | The circuit of a synapse                                                                                                                                                  |

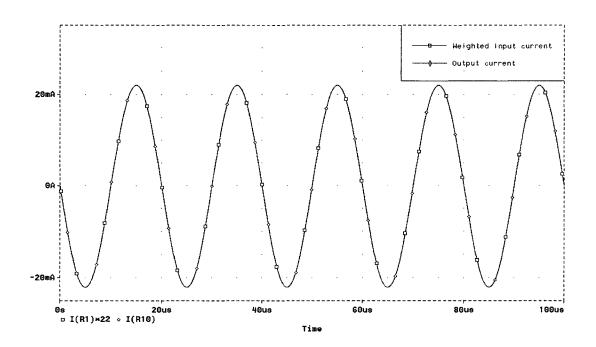

| Figure 3.18 | Simulation results to show the function of the circuit in Figure 3.17 52                                                                                                  |

| Figure 3.19 | The circuit of a neuron                                                                                                                                                   |

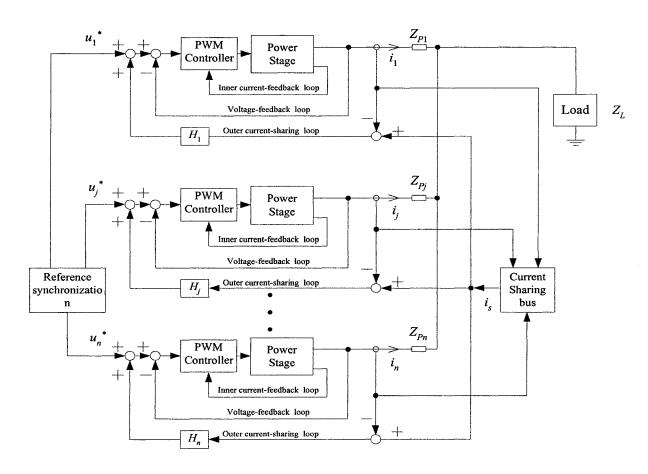

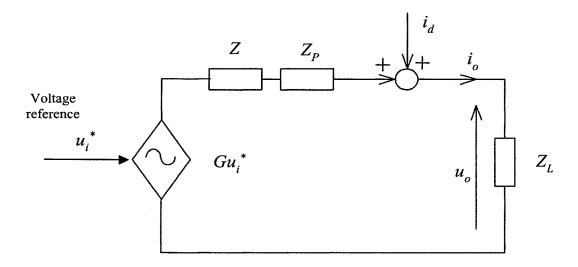

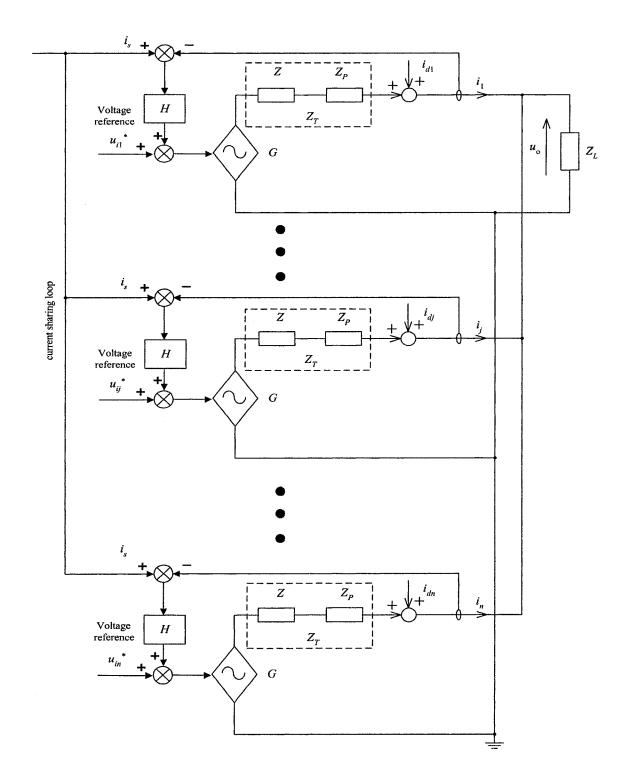

| Figure 4.1  | A block diagram of parallel multi-inverter system59                                                                                                                       |

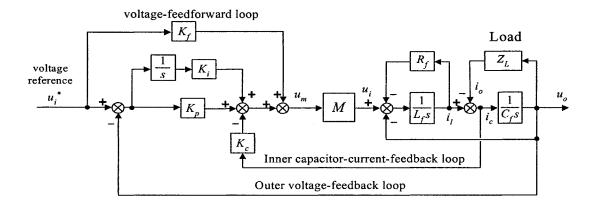

| Figure 4.2  | Linear model of inverter with multi-loop feedback control61                                                                                                               |

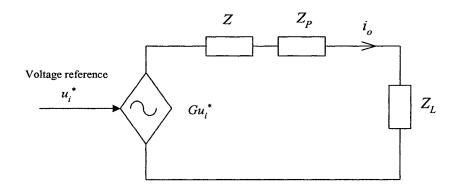

| Figure 4.3  | Thévenin equivalent circuit of a closed-loop inverter62                                                                                                                   |

| Figure 4.4  | Typical Bode plots of the closed-loop gain $G$ and the output impedance $Z$                                                                                               |

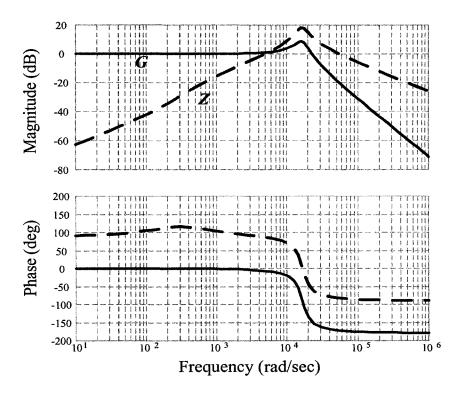

| Figure 4.5  | Inverter model showing disturbance surce                                                                                                                                  |

| Figure 4.6  | Model of a parallel multi-inverter system65                                                                                                                               |

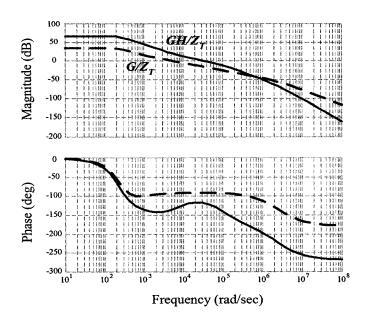

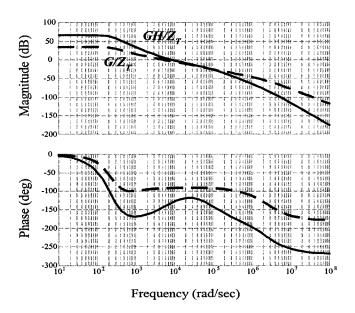

| Figure 4.7  | Bode plots of $G/Z_T$ and $GH/Z_T$ ( $H$ have the transfer function of (4-9))                                                                                             |

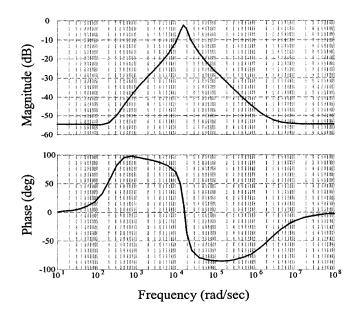

| Figure 4.8  | Bode plots of $\frac{Z_T}{nZ_T}$ . (Total load is $5\Omega$ , number of paralleled                                                                                        |

|             | inverters is 2)                                                                                                                                                           |

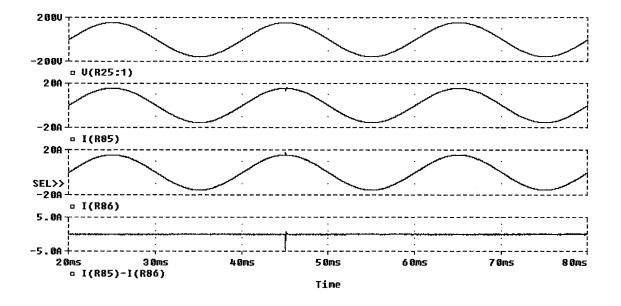

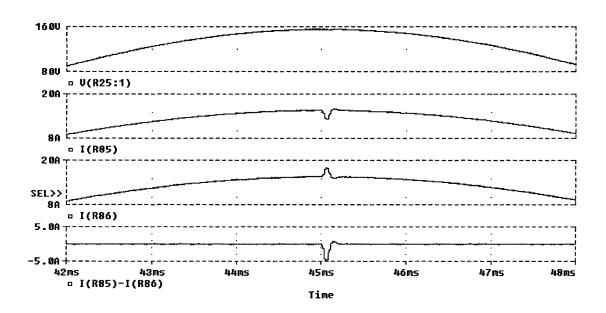

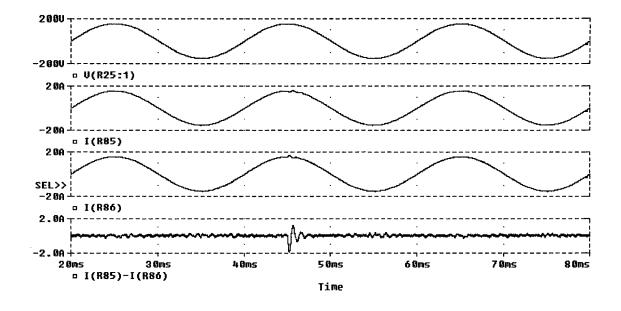

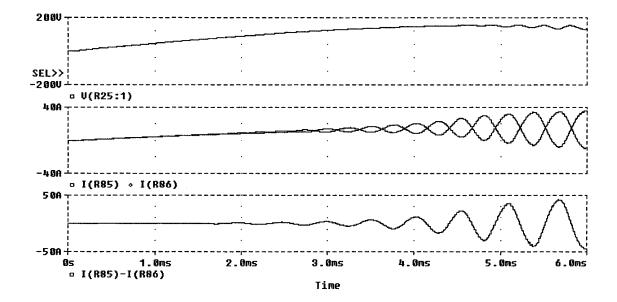

| Figure 4.9  | PSpice simulation results of transient response of two-inverter system with H of (4-9), (a), global view, (b), detailed view, First:                                      |

|             | output voltage; Second: output current of the first inverter; Third: output current of the second inverter; Fourth: error between the output current of the two inverters                                                                                                                                                                                                                                                      | '1 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.10 | Bode plots of $G/Z_T$ and $GH/Z_T$ (H has the transfer function of (4-10))                                                                                                                                                                                                                                                                                                                                                     | '2 |

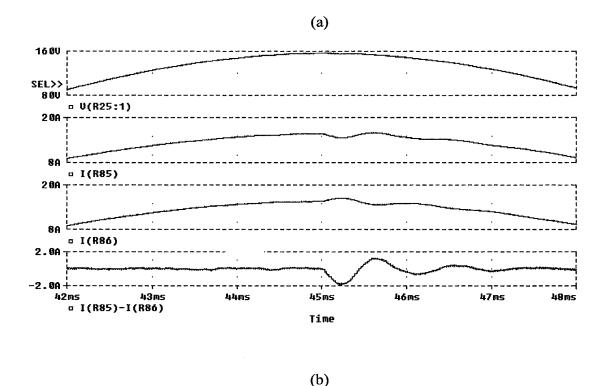

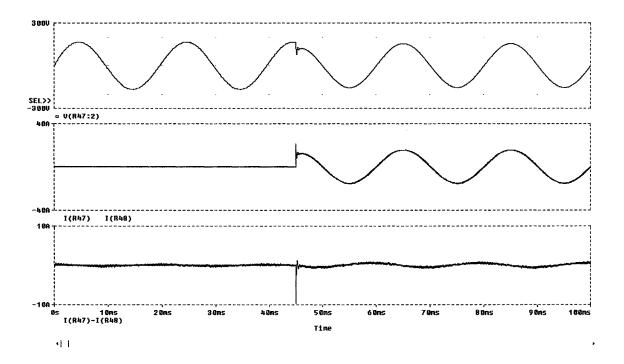

| Figure 4.11 | PSpice simulation results of transient response of two-inverter system with $H$ of (4-10). (a). global view. (b). detailed view. First: output voltage; Second: output current of the first inverter; Third: output current of the second inverter; Fourth: error between the output current of the two inverters.                                                                                                             | '3 |

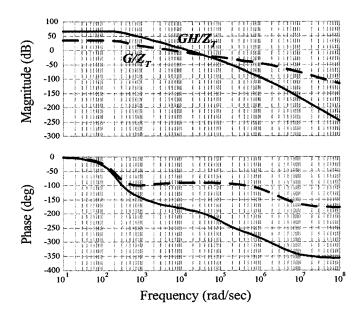

| Figure 4.12 | Bode plots of $G/Z_T$ and $GH/Z_T$ ( $H$ have the transfer function of (4-11))                                                                                                                                                                                                                                                                                                                                                 | '4 |

| Figure 4.13 | PSpice simulation results of transient response of two-inverter system with $H$ of (4-11). First: output voltage; Second: output current of both inverters; Third: error between the output current of the two inverters.                                                                                                                                                                                                      | '5 |

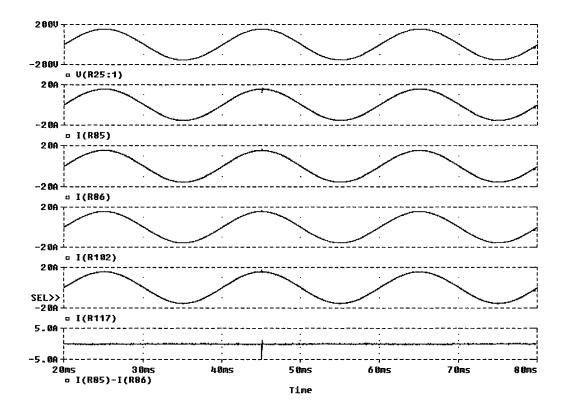

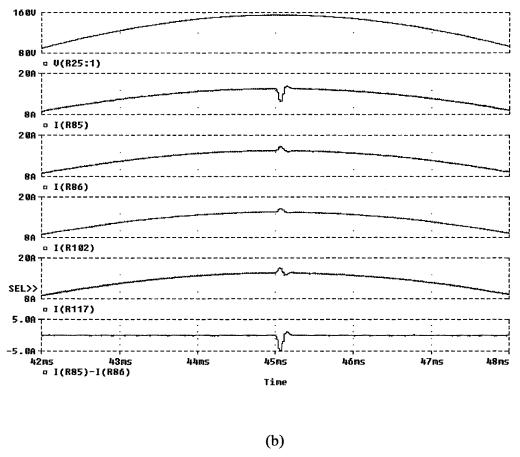

| Figure 4.14 | PSpice simulation results of transient response of four-inverter system with $H$ of (4-9). (a). global view. (b). detailed view. First: output voltage; Second: output current of the first inverter; Third: output current of the second inverter; Fourth: output current of the third inverter; Fifth: output current of the fourth inverter; Sixth: error between the output current of the first and the second inverters. | '7 |

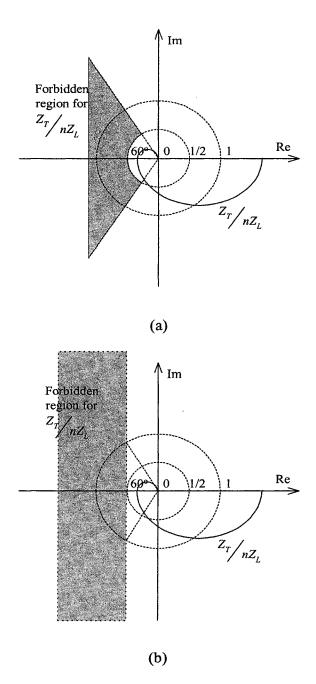

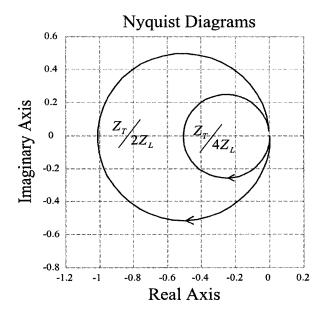

| Figure 4.15 | Forbidden regions for $\frac{Z_T}{nZ_L}$                                                                                                                                                                                                                                                                                                                                                                                       | 9  |

| Figure 4.16 | Nyquist plots of $\frac{Z_T}{2Z_L}$ and $\frac{Z_T}{4Z_L}$                                                                                                                                                                                                                                                                                                                                                                     | 1  |

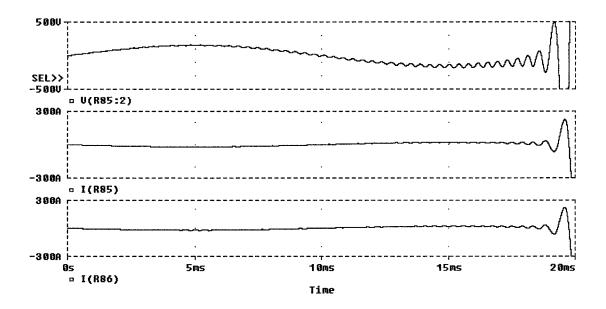

| Figure 4.17 | PSpice simulation results of transient response of two-inverter system with negative resistance, $-4\Omega$ . First: output voltage; Second: output current of the first inverter; Third: output current of the second inverter.                                                                                                                                                                                               | 1  |

| Figure 4.18 | PSpice simulation results of transient response of four-inverter system with negative resistance, $-4\Omega$ . First: output voltage; Second: output current of the first inverter; Third: output current of the second inverter; Fourth: output current of the third inverter; Fifth: output current of the fourth inverter.                                                                                                  | 2  |

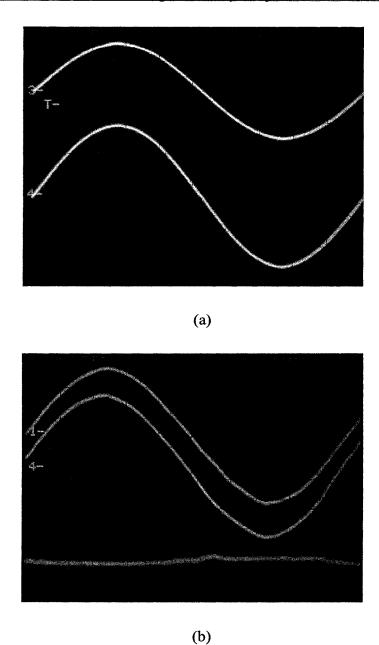

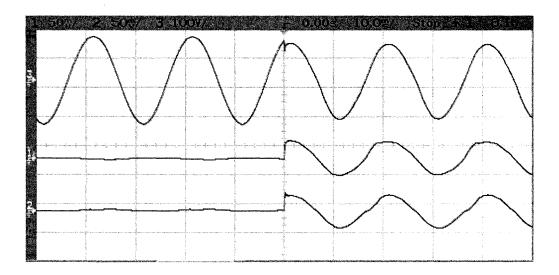

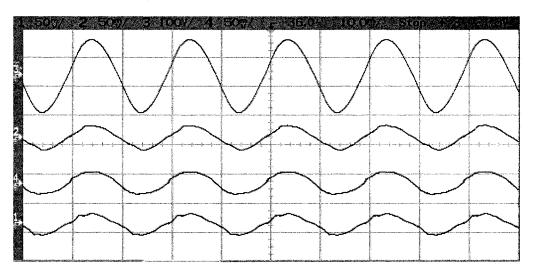

| Figure 4.19 | Steady-state response of the two-inverter system with the current sharing controller of (4-10). (a). output voltage (upper: 100V/div) and output current (lower: 10A/div); (b). current of both inverters (upper: 5A/div) and current error between them (bottom: 5A/div).                                                                                                                                                     | 5  |

| Figure 4.20 | Steady-state response of the two-inverter system with the current sharing controller of (4-9). (a). output voltage (upper: 100V/div) and output current (lower: 10A/div); (b). current of both inverters (upper: 5A/div) and current error between them (bottom: 5A/div)86                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

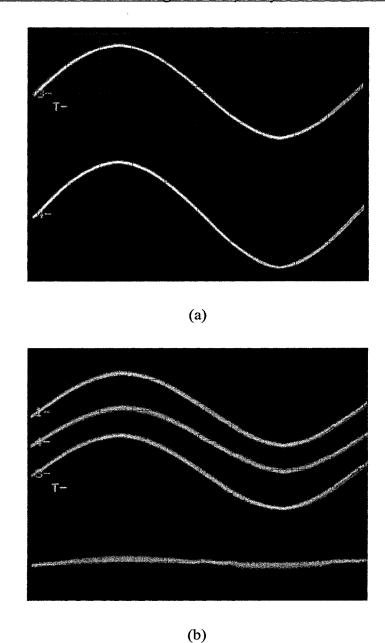

| Figure 4.21 | Steady-state response of the three-inverter system with the current sharing controller of (4-9). (a). output voltage (upper: 100V/div) and output current (lower: 20A/div); (b). current of all inverters (upper: 10A/div) and current error between first and second inverter (bottom: 10A/div).               |

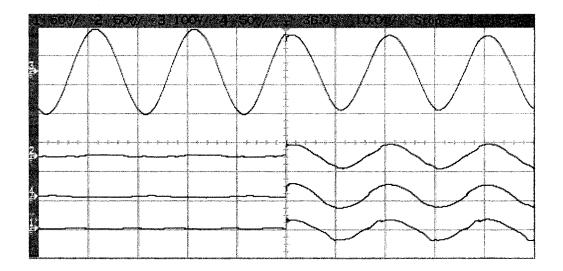

| Figure 4.22 | Dynamic response of the two-inverter system with the current sharing controller of (4-10). (a). output voltage (upper: 100V/div) and output current (lower: 10A/div); (b). current of both inverters (upper: 5A/div) and current error between them (lower: 5A/div)88                                           |

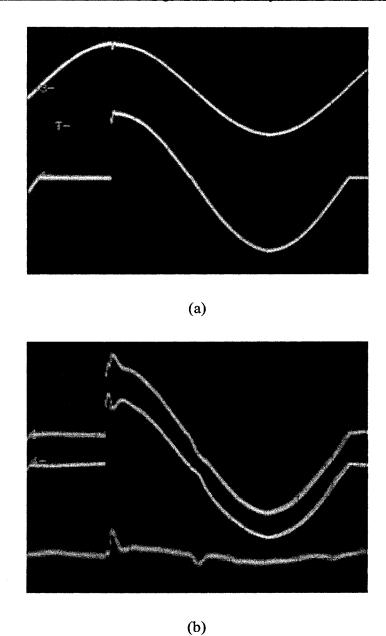

| Figure 4.23 | Dynamic response of the two-inverter system with the current sharing controller of (4-9). (a). output voltage (upper: 100V/div) and output current (lower: 10A/div); (b). current of both inverters (upper: 10A/div) and current error between them (lower: 10A/div)89                                          |

| Figure 4.24 | Dynamic response of the three-inverter system with the current sharing controller of (4-9). (a). output voltage (upper: 100V/div) and output current (lower: 20A/div); (b). current of both inverters (upper: 10A/div) and current error between first and second inverter (lower: 10A/div)                     |

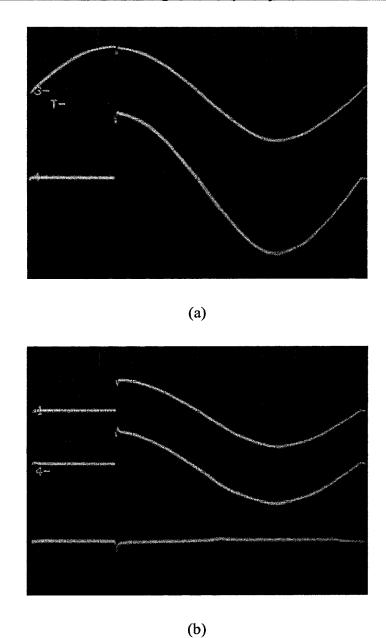

| Figure 4.25 | Response of the three-inverter system with the current sharing controller of (4-9) for rectifier-type load. (a). output voltage (upper: 100V/div) and output current (lower: 20A/div); (b). current of both inverters (upper: 10A/div) and current error between first and second inverter (lower: 10A/div)     |

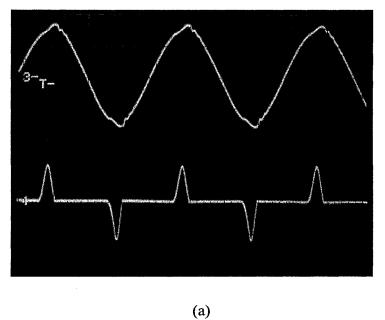

| Figure 5.1  | Model of <i>n</i> paralleled inverters97                                                                                                                                                                                                                                                                        |

| Figure 5.2  | Diagram of proposed state-feedback controller for <i>j</i> -th inverter of the multi-inverter system                                                                                                                                                                                                            |

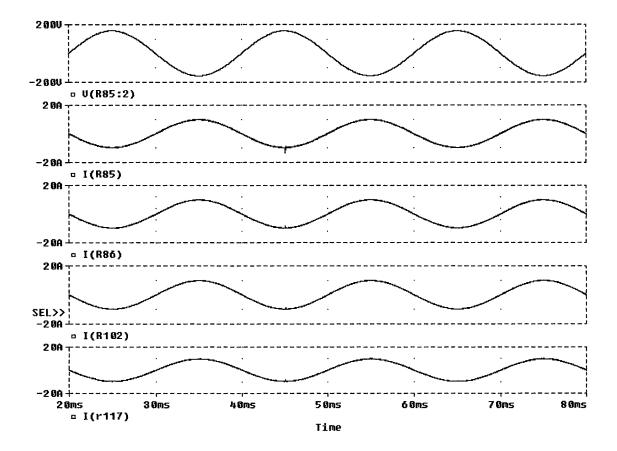

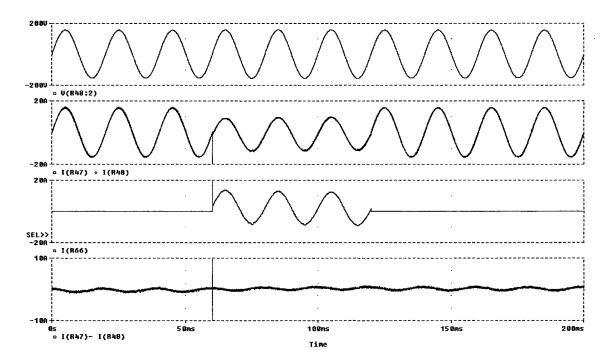

| Figure 5.3  | Simulation results of a two-inverter system when load changes from open circuit (no load) to $5\Omega$ . Top: the output voltage, Middle: the output currents of individual inverter. Bottom: the output current difference between two inverters                                                               |

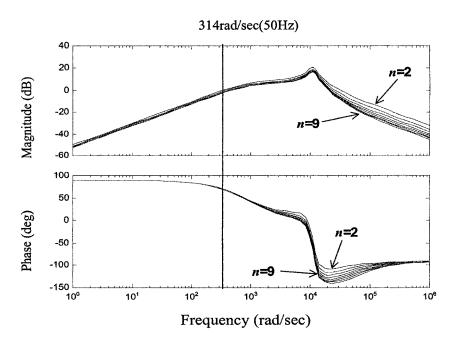

| Figure 5.4  | Bode plot of the equivalent output impendence of multi-inverter system $(n = 2,, 9)$                                                                                                                                                                                                                            |

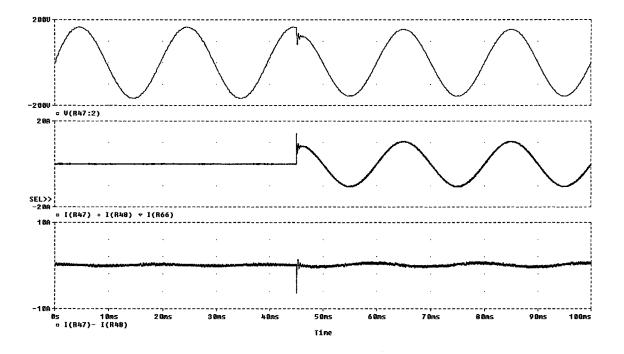

| Figure 5.5  | Simulation results of a three-inverter system (the third inverter is added, then removed). Top: the output voltage. Second: the output currents of the first and second inverter. Third: the output current of the third inverter. Bottom: the output current difference between the first and second inverters |

| Figure 5.6  | Simulation results of a three-inverter system when load changes from open circuit (no load) to $5\Omega$ . Top: the output voltage. Middle: the output currents of the first, second and third inverter. Bottom: the output current difference between the first and second inverters116                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

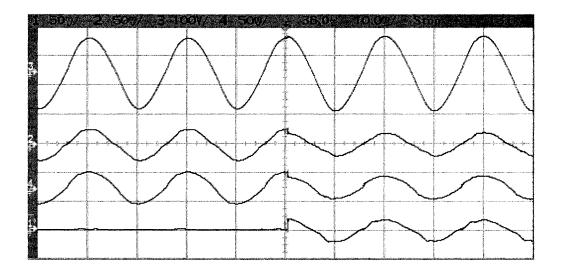

| Figure 5.7  | Experimental results of a two-inverter system under rated load of $5\Omega$ . Top: the output voltage (100V/div). Middle: the output currents of the first inverter (25A/div). Bottom: the output current of the second inverter (25A/div).                                                                                                 |

| Figure 5.8  | Experimental results of a two-inverter system when load changes from open circuit (no load) to $5\Omega$ . Top: the output voltage (100V/div). Middle: the output currents of the first inverter (25A/div). Bottom: the output current of the second inverter (25A/div).                                                                    |

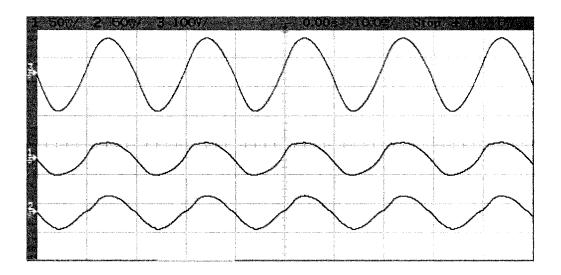

| Figure 5.9  | Experimental results of a three-inverter system under load of $5\Omega$ . Top: the output voltage (100V/div). Second: the output currents of the first inverter (25A/div). Third: the output currents of the second inverter (25A/div). Bottom: the output current of the third inverter (25A/div).                                         |

| Figure 5.10 | Experimental results of a three-inverter system when load changes from open circuit (no load) to $5\Omega$ . Top: the output voltage (100v/div). Second: the output currents of the first inverter (25A/div). Third: the output currents of the second inverter (25A/div). Bottom: the output current of the third inverter (25A/div).      |

| Figure 5.11 | Experimental results of a three-inverter system when an inverter is added (load of $5\Omega$ ). Top: the output voltage (100v/div). Second: the output currents of the first inverter (25A/div). Third: the output currents of the second inverter Bottom (25A/div): the output current of the third inverter (25A/div)                     |

| Figure 5.12 | Experimental results of a three-inverter system when an inverter is removed (load of $5\Omega$ ). Top: the output voltage ( $100v/div$ ). Second: the output currents of the first inverter ( $25A/div$ ). Third: the output currents of the second inverter ( $25A/div$ ). Bottom: the output current of the third inverter ( $25A/div$ ). |

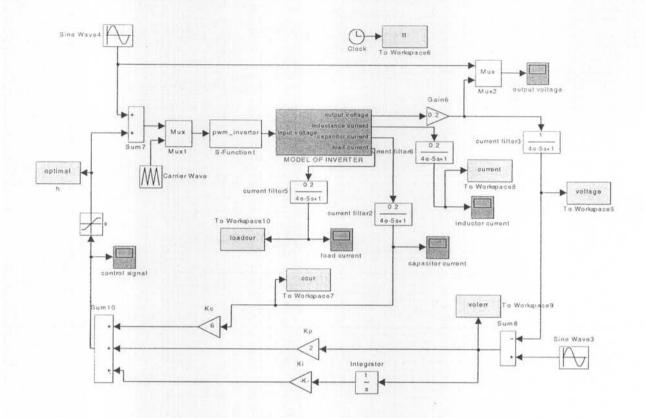

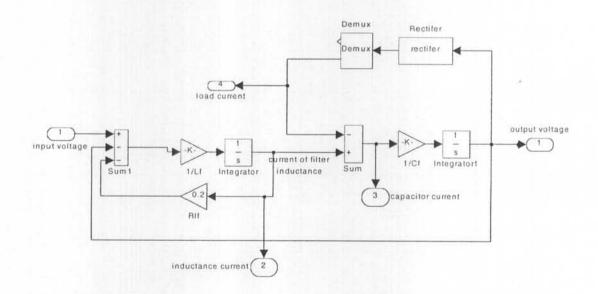

| Figure A.1. | SIMULINK model of Figure 3.3                                                                                                                                                                                                                                                                                                                |

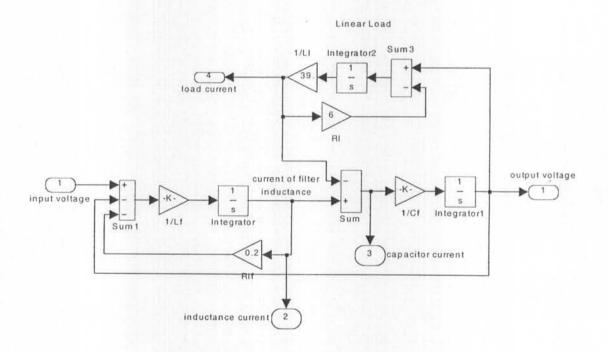

| Figure A.2. | Details of the subsystem of "model of inverter" in Figure A.1131                                                                                                                                                                                                                                                                            |

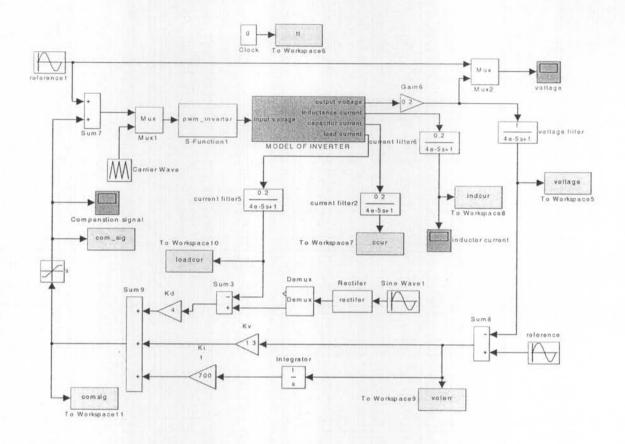

| Figure A.3. | SIMULINK model of Figure 3.4. 132                                                                                                                                                                                                                                                                                                           |

| Figure A.4. | Details of the subsystem of "model of inverter" in Figure A.2                                                                                                                                                                                                                                                                               |

## **List of Tables**

| Table 3.1 | Inverter Parameters                                                               | 38  |

|-----------|-----------------------------------------------------------------------------------|-----|

| Table 3.2 | THD of Output Voltage under Various Load Conditions                               | 40  |

| Table 4.1 | The parameter lists of L-C filter and line impedance that used in the simulation. | 67  |

| Table 5.1 | Parameter list                                                                    | 107 |

## Chapter 1

## Introduction

## 1.1 Motivation

As modern society continues to increase its reliance on electrical and electronic equipment, there is a growing demand for a clean and reliable ac power to keep these devices operating regardless of weather, location or other conditions adverse to nominal utility power supply [1]. Traditionally, backup generators have been used to meet this need, and they continue to be installed in great numbers in hospitals, data processing centers, recreational & emergency vehicles, communication centers and the like. However, backup generators have an unavoidable lag of several seconds from the beginning of a power outage to the time that the generator can be started and switched in. While this was once a minor inconvenience, there now exists a growing class of "critical loads" that demand uninterrupted power at all times. Such loads include:

- Computer Systems

- Security Systems

- Communication Systems

- Hospital Equipment

#### Critical Process Control Equipment

As such, power electronic inverters have been developed that can synthesize sinewave ac voltage from a backup power source, traditionally a bank of batteries. These inverters can be activated almost instantaneously in case of a power outage, and thus can provide uninterrupted ac power. Hence, the phrased "Uninterruptible Power Supply" (UPS) was coined.

Furthermore, UPSs can protect their loads from disturbances of the mains supply.

These disturbances can be divided into different categories [2]:

- Radio-frequency (rf) voltages,

- Voltage spikes,

- Harmonic voltages,

- Dips, surges, brown-outs, flickers and failure.

As an alternative of the main supplies, UPSs are required to produce constant sinusoidal output voltage with minimum Total Harmonic Distortion (THD) for a wide load range: from resistive to reactive (inductive or capacitive), and from linear to nonlinear. At the same time, fast transient response, good stability and high reliability are also required.

Nowadays, more and more power electronic converters are employed to provide electrical power. Most of converters use diode rectifiers (followed by a filtering capacitor) as an interface with the mains supply, which draws non-sinusoidal current with high spike when fed with a sinusoidal voltage. When serving the nonlinear loads, like diode rectifiers, UPSs should have much higher dynamic stiffness and much lower output impedance. It is becoming more difficult (but essential) to design a suitable

controller for a dc/ac inverter, the core of a UPS, to maintain a sinusoidal voltage, especially for the cases of nonlinear loads.

Parallel operation is tendency of power supplies [3]. The power capability of the system can be easily expanded by adding more modules into system. Reliability, redundancy and modularity are also improved by parallel operation. Technologies for Parallel operation of dc/dc converter have been developed for last two decades. Some successful technologies [4] and mature commercial products [5] provide very convenient method to parallel connect converters with high performance.

As a backup power supply system, the reliability and redundancy of the UPSs are remarkable. Parallel operation can provide a good solution to improve reliability and redundancy. More and more researchers put their focuses on parallel operation of UPSs.

## 1.2 Background

As the technology of power electronics has progressed over the years, so has the technology of UPS inverters: as far back as 1981 there were UPS systems referred to as "5th generation". A complete history of UPS inverter development is beyond the scope of this thesis. In general, as better power electronic switching devices and techniques became available, they were subsequently incorporated into UPS inverter designs. It should be noted that UPS inverter designs incorporated ferroresonant transformers, though quite prevalent in the past, will not be considered as they are becoming obsolete. It should also be noted that the scope of the research reported in this thesis is limited to the ac output voltage synthesis and control of UPS-style inverters. Other issues pertaining to UPS inverter systems, such as battery maintenance, startup-shutdown, line-synchronization, etc. will not be addressed.

Chapter 1 Introduction

Today, the vast majority of UPS inverters incorporate transistors (IGBTs or MOSFETs). They are of the voltage source inverter (VSI) type, with a DC link supplying voltage to the inverter bridge. These types of UPS inverters can be classified into two broad categories based on their output voltage synthesis:

- 1). **Stepped-wave output**: Here a sinusoidal waveform is approximated by a series of voltage "steps". The RMS magnitude of the output voltage is usually controlled by varying the width, or duty-cycle, of the steps. The peak of the output voltage steps are determined by the dc link (or bus) voltage level [6].

- 2). Sinewave output: These inverters produce a "smooth" sinusoidal output voltage by passing the output of the inverter bridge through an LC filter. To minimize the size and rating of the filter components, the inverter bridge is usually pulse-width-modulated (PWM) at a switching frequency much higher than the fundamental of the synthesized output voltage. Output voltage control can be controlled either on an RMS or instantaneous basis [7].

Early UPS inverters were dominated by the stepped-wave design (also referred to as "quasi-sinewave"). They were simple to implement and had a high efficiency due to the low switching frequency. The drawbacks of these inverters included poor output voltage quality, as measured by THD, and rather slow response to load transients. While many types of loads (such as lighting and heating) function properly with stepped-wave inverters, the harmonics of the output voltage waveform tend to heat up motors, and adversely affect some other types of electronic equipment. Today, these types of UPS inverters are found mostly in low-cost systems where waveform quality is not a major concern.

Chapter 1 Introduction

As with all electronic equipment, better performance is continually being sought, and thus sinewave output UPS inverters are increasingly in demand. With advances in power electronic device performance, high-frequency PWM inverters can deliver up to 100KVA and beyond [8]. These types of sinewave inverters are compatible with all types of ac-powered equipment. They can also offer fast-speed regulation and low THD (better than what is generally supplied by the utility). In addition, since the inverter comprises an electronic converter, a much wide range of dc bus voltage can be utilized. This thesis is concerned with Sinusoidal Pulse-Width-Modulated (SPWM) UPS inverter systems with LC filters intended for sinewave output voltage waveforms, as these are seen to be the most dominant design for current and future UPS systems.

In a SPWM inverter, the switching frequency is usually several orders higher than the fundamental frequency of the output voltage. The dynamics of the switching can therefore be ignored. An averaged time-continuous model of the SPWM inverter can be easily derived. Such a model is quite precise within half the switching frequency. Generally, the frequency domain analysis is applied to the controller design of SPWM inverters. The Bode plots are powerful tools, which make system analysis and controller evaluation visable and straightforward. The derived controller, mostly PI controllers, have been widely used in SPWM inverters. However, because the design is based on the linearized model under a specific loading condition, the performance of PI controllers is often far from ideal for extreme loading conditions. For example, under nonlinear loading conditions, PI controllers often have poor ability to maintain a low THD in the output voltage.

Parallel operation of the UPS inverters can bring many desirable advantages. However, for the following reasons, the parallel operation of voltage source inverters is very sensitive to disturbance, and therefore extremely careful consideration should be given when planning and designing the system [9].

- An inverter has an overload capacity of only 150-200 percent, and if the

output current exceeds this limit, even for a fraction of a cycle, this will

result in a commutation failure or a damage of the switching device.

- Because of its low-impedance and quick-response characteristics, the inverter output current changes very rapidly and thereby easily reaches an overload condition.

- There are many different configurations of inverter circuits with various operating principles, and each configuration has its own characteristics and weakness.

Therefore, some addition mechanisms are required to deal with the current balance among the inverters. However, not much research work had been reported on the parallel operation of dc/ac inverters.

## 1.3 Objectives

The performance of the UPS inverters under nonlinear loads is quite essential since more and more electrical loads are becoming nonlinear and generate harmonics. However, the design of most controllers for UPS inverters is based on linearized models. Although linear models make the design quite simple and direct, the performance of the systems degrades in a wide load range. The intelligent control, like fuzzy logic or neural networks, shows its advantages to deal with nonlinear systems, and attracts efforts on research and development. In this thesis, neural networks are applied to the control of UPS inverters. The focuses are put on trying to find a simple and low-cost solution of

Chapter 1 Introduction

neural-network controller for the UPS inverter, which is expected to have superior performance under nonlinear loading conditions.

Due to the shortage of knowledge of parallel multi-inverter system, when we design such a system, some questions arise. Can we apply the methodology of design of a single inverter to the design of a parallel multi-inverter system? Are the characteristics of the inverters changed when they are paralleled together? How to model a parallel multi-inverter system? Can we predict the performance of the parallel multi-inverter system when we design the controllers? This thesis tries to answer these questions.

#### 1.4 Outline of the Thesis

Chapter 2 gives a brief introduction to the basics of SPWM dc/ac inverters. The circuit topology, PWM operation, and linear model of the SPWM dc/ac inverters are addressed. The linear model developed will be used in other chapters to analyze and synthesize the SPWM dc/ac inverters.

In Chapter 3, neural-network-based control is introduced into SPWM dc/ac inverters. The proposed neural-network controller is benefited from the nonlinear-functional-mapping ability of the neural networks. Design procedures of the proposed controller are given. Simulation and experimental results show its superior performance to a PI controller with optimized parameters. The implementation of the analogue neural-network controller using integrated circuits is also discussed.

In Chapter 4, a parallel multi-inverter system with instantaneous average-currentsharing scheme is discussed. A model that describes the whole system's performance is built. Based on this model, some key issues of parallel multi-inverter systems are discussed, including stability of the current-sharing controller, impedance characteristics and voltage regulation. Three experimental 110Vac/1.1KVA inverters are built and paralleled to verify the theoretical predictions.

Chapter 5 further discusses the parallel multi-inverter system. The optimal theory is employed to design a state feedback controller for the system. The robustness of the controller to the change of the number of parallel inverters has also been investigated. Simulation and experimental results are provided.

Finally, Chapter 6 presents conclusions and discusses opportunities for further research.

## Chapter 2

## Basics of Sinusoidal PWM dc/ac

## **Inverters**

#### 2.1 Introduction

As mentioned in Chapter 1, the scope of this thesis is limited to single-phase high frequency SPWM voltage source inverters with LC output filters. In general, this type of sinusoidal inverter is well suited for producing tightly regulated sinusoidal output voltage waveforms. Since most modern sinusoidal inverters are operated above the audible range (≥18kHz) to alleviate human discomfort (as well as to reduce filter component size), the inverter harmonics have frequencies well above that of the output voltage fundamental, and are easily filtered out. This chapter presents a brief introduction to the basics of sinusoidal PWM inverters. The popular circuit topologies, PWM operation and linearized models of inverters are included.

## 2.2 Topologies of a dc/ac Inverter

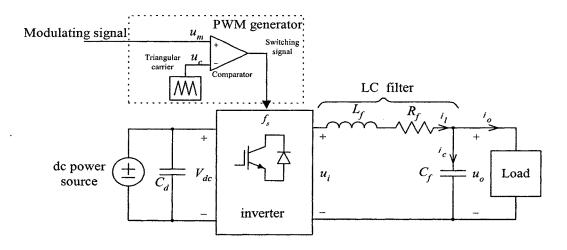

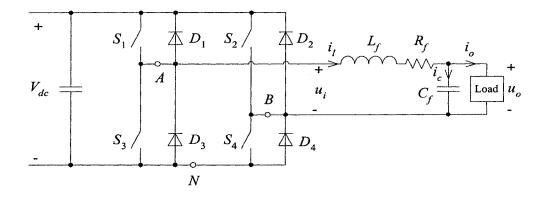

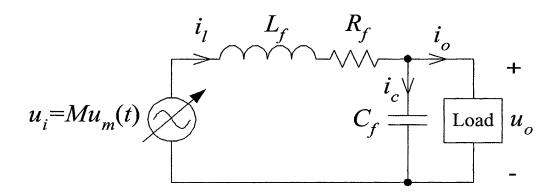

A sinusoidal inverter typically consists of a dc power source, a PWM inverter and an LC filter, as shown in Figure 2.1. The inverter, which is the core of the system, chops

the dc input into a series of PWM pulses according to modulation signal  $u_m$ . The function of the second-order LC filter is to remove the high frequency components of the chopped output voltage  $u_i$ .  $R_f$  represents the resistance of the filter inductor. The effective series resistance (ESR) of the filter capacitor is ignored since it only has a small effect within the frequency range concerned. The dc power source is considered as an ideal constant-voltage supply. The load shown in Figure 2.1 can be of any type: resistive, inductive, capacitive or nonlinear.

Figure 2.1 Single-phase Sinusoidal PWM inverter.

The most obvious and popular configurations for the inverter, shown in middle of Figure 2.1, are half-bridge and full-bridge inverters [10][11]. The following two subsections give a brief introduction to both of them.

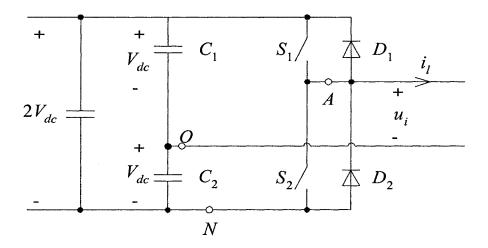

#### 2.2.1 Half-Bridge Inverter

Figure 2.2 shows a half-bridge inverter. Here, two equal capacitors are connected in series across the dc input. Their junction is at a midpotential, with a voltage  $V_{dc}$  across each capacitor. Sufficiently large capacitances should be used such that it is reasonable to assume that the potential at point O remains essentially constant with

respect to the negative dc bus N. The two switches,  $S_1$  and  $S_2$ , are switched in such a way that when one of them is on, the other is off. The two switches are never turned on simultaneously. In practice, they can also be both off for a short time interval (known as the blanking time) to avoid short circuit of the dc input. Because of the anti-parallel diodes of the switches, when a switch is turned on, it may or may not conduct a current, depending on the direction of the output current  $i_l$ . Therefore, a half-bridge inverter such as shown in Figure 2.2 can operate in all four quadrants of the  $i_l$ - $u_l$  plane, and the power flow through the inverter can be in either direction.

Figure 2.2 Half-bridge inverter.

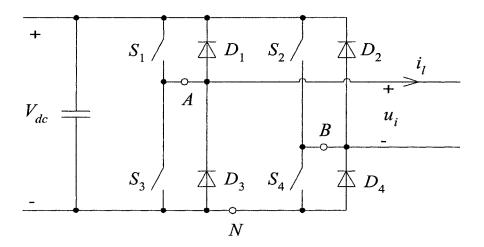

#### 2.2.2 Full-Bridge Inverter

A full-bridge inverter is shown in Figure 2.3. This inverter consists of two legs, A and B. The number of switches is twice that of the half-bridge inverter. Full-bridge is the preferred arrangement for higher power applications. With the same output voltage, the minimum dc input voltage of the full-bridge inverter is half that of the half-bridge inverter. This implies that for the same power, the voltage stresses of the switches are

one-half of those for a half-bridge inverter. At high power levels, this is a distinct advantage.

Figure 2.3 Full-bridge inverter.

## 2.3 PWM Operation of Inverters

Pulse-width-Modulation (PWM) provides a way to decrease the Total Harmonic Distortion (THD) of load current. A PWM inverter output, with some filtering, can meet THD requirements easily. The unfiltered PWM output will have a relative high THD, but the harmonics will be at much higher frequencies, making filtering easier.

In PWM, the amplitude of the output voltage can be controlled by the modulating waveform. Reduced filter requirements for harmonics and easier control of the output voltage amplitude are two distinct advantages of PWM. Disadvantages include more complex control circuits for the switches and increased losses due to high frequency switching.

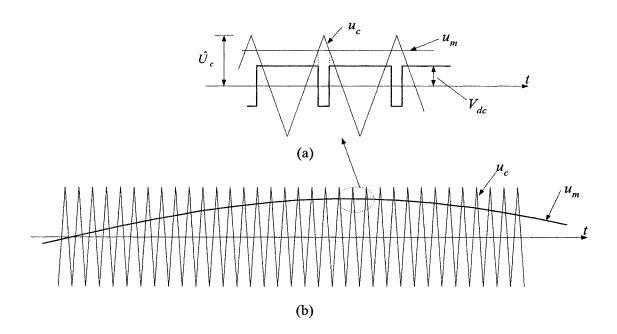

The control of the switches for sinusoidal PWM output requires (1) a reference signal, sometime called a modulating or control signal ( $u_m$  as shown in Figure 2.1),

which is a sinewave; and (2) a carrier signal ( $u_c$  as shown in Figure 2.1), which is a triangular wave that controls the switching frequency.

Before discussing the PWM behavior, it is necessary to define a few terms. The triangular carrier  $u_c$  in Figure 2.1 has amplitude of  $\hat{U}_c$  and frequency of  $f_s$ , which establishes the switching frequency of the inverter. The modulating signal  $u_m$  is used to modulate the switch duty ratio and has a frequency of  $f_1$ , which is the desired fundamental frequency of the inverter voltage output. The amplitude modulation ratio  $m_a$  is defined as

$$m_a = \frac{\hat{U}_m}{\hat{U}_c} \tag{2-1}$$

where  $\hat{U}_m$  is the peak amplitude of the modulating signal. The amplitude  $\hat{U}_c$  of the triangular carrier is generally kept constant.

The frequency modulation ratio  $m_f$  is defined as

$$m_f = \frac{f_s}{f_1} \tag{2-2}$$

Bipolar and unipolar switch schemes are introduced in following two sub-sections.

#### 2.3.1 Bipolar Switching

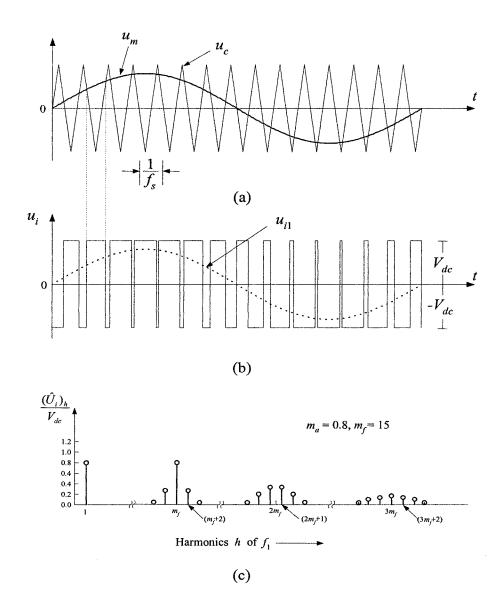

Figure 2.4 Bipolar pulse-width modulation.

Figure 2.4 illustrates the principle of sinusoidal bipolar pulse-width modulation. Figure 2.4a shows a sinusoidal reference signal and a triangular carrier signal. When the instantaneous value of the sine reference is larger than the triangular carrier, the output is at  $+V_{dc}$ , and when the reference is less than the carrier, the output is at  $-V_{dc}$  as shown in Figure 2.4b.

The fundamental of the output voltage  $u_i$  of the inverter is a sinusoidal waveform, whose magnitude and frequency can be controlled by the reference (modulating signal). This version of PWM is bipolar because the output alternates between the positive and the negative of the dc supply voltage.

The switching schemes that will implement bipolar switching using the halfbridge inverter of Figure 2.2 and the full-bridge inverter of Figure 2.3 are

$$u_m > u_c$$

:  $S_1$  on;  $u_i = V_{dc}$ ,

$$u_m < u_c$$

:  $S_2$  on;  $u_i = -V_{dc}$ .

and

$$u_m > u_c$$

:  $S_1$  and  $S_4$  on;  $u_i = V_{dc}$ ,

$$u_m < u_c$$

:  $S_2$  and  $S_3$  on;  $u_i = -V_{dc}$ .

The harmonic spectrum of  $u_i$  under the bipolar PWM switching is shown in Figure 2.4c, where the normalized harmonic voltages  $\frac{(\hat{U}_i)_h}{V_{dc}}$  are plotted. The harmonics in the inverter output voltage waveform appears as sidebands, centered around the switching frequency and its multiples, that is, around harmonics  $m_f$ ,  $2m_f$ ,  $3m_f$ , and so on. Therefore, if  $m_f$  is large, the harmonics of the output voltage will appear at high frequency, the size of filter can be reduced significantly.

#### 2.3.2 Unipolar Switching

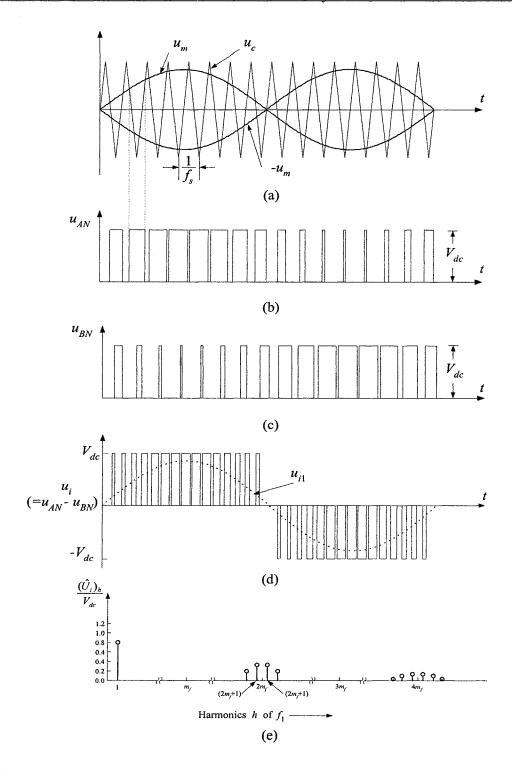

Unipolar switching is for full-bridge inverter only, because the switches in the two legs of the full-bridge inverter of Figure 2.3 are not switched simultaneously as in the bipolar switching scheme. Here, the legs of A and B of the full-bridge inverter are controlled separately by comparing  $u_c$  with  $u_m$  and  $-u_m$ , respectively.

Figure 2.5 Unipolar pulse-width modulation.

As shown in Figure 2.5a, the comparison of modulating signal  $u_m$  with the triangular carrier  $u_c$  results in the following switching scheme in leg A:

$$u_m > u_c$$

:  $S_1$  on and  $u_{AN} = V_{dc}$ ,

$$u_m < u_c$$

:  $S_4$  on and  $u_{AN} = 0$ .

The output voltage of inverter leg A with respect to the negative dc bus N is shown in Figure 2.5b. For controlling the leg B switches,  $-u_m$  is compared with the same triangular carrier  $u_c$ , which yields the following:

$$(-u_m) > u_c$$

:  $S_2$  on and  $u_{BN} = V_{dc}$ ,

$$(-u_m) < u_c$$

:  $S_3$  on and  $u_{BN} = 0$ .

Because there are antiparallel diodes across the switches, the voltages at  $u_{AN}$  and  $u_{BN}$  are independent of the direction of the output current  $i_l$ . The waveforms of Figure 2.5 show that there are four combinations of switch on-states and the corresponding voltage levels:

1.

$$S_1$$

,  $S_4$  on:  $u_{AN} = V_{dc}$ ,  $u_{BN} = 0$ ;  $u_i = V_{dc}$

2.

$$S_2$$

,  $S_3$  on:  $u_{AN} = 0$ ,  $u_{BN} = V_{dc}$ ;  $ui = -V_{dc}$

3.

$$S_1$$

,  $S_2$  on:  $u_{AN} = V_{dc}$ ,  $u_{BN} = V_{dc}$ ;  $u_i = 0$

4.

$$S_3$$

,  $S_4$  on:  $u_{AN} = 0$ ,  $u_{BN} = 0$ ;  $u_i = 0$

In this type of PWM scheme, when a switching occurs, the output voltage changes between zero and  $+V_{dc}$ , or between zero and  $-V_{dc}$ . For this reason, this type of PWM scheme is called PWM with a unipolar voltage switching, as opposed to the PWM with bipolar (between  $+V_{dc}$  and  $-V_{dc}$ ) voltage switching scheme, as described in last sub-section. This scheme has the advantage of "effectively" doubling the switching frequency as far as the output harmonics are concerned, compared to the bipolar voltage-switching scheme. Figure 2.5e shows the harmonic spectrum of the output voltage  $u_i$ , where the lowest harmonics (in the idealized circuit) appear as sidebands of twice the switching frequency.

There is yet another unipolar switching scheme which has one pair of switches operating at the carrier frequency and another pair operating at the ac reference frequency, thus having two high-frequency switches and two low-frequency switches [11]. The switching losses of those two switches with low switching frequency are greatly reduced. Furthermore, they can be implemented using slow power semiconductor devices (e.g., GTO thyristors), which usually have lower conduction losses than the corresponding fast power semiconductor devices (e.g., MOSFET's).

## 2.4 Linear Model of a Sinusoidal dc/ac Inverter

Figure 2.6 Full-bridge inverter with LC filter.

Figure 2.6 shows a full-bridge inverter with LC filter. Assuming that the bipolar PWM scheme is used, the output voltage  $u_i$  of the bridge changes between  $+V_{dc}$  and  $-V_{dc}$ . With the foregoing discussion, a switching function is defined as follows:

$$S^* = \begin{cases} 1 & u_m > u_c : S_1 \text{ and } S_3 \text{ on} \\ 0 & u_m < u_c : S_2 \text{ and } S_4 \text{ on} \end{cases}$$

(2-3)

Therefore, the output voltage  $u_i$  of the bridge can be described as

$$u_i = V_{dc}(2S^* - 1) (2-4)$$

Figure 2.7 Sinusoidal PWM.

Let us assume (though this assumption is not necessary) that the carrier frequency  $f_s$  is much high than the frequency  $f_1$  of the modulating signal  $u_m$ , meaning that the frequency modulation ratio  $m_f$  is large, as shown in Figure 2.7b. Therefore,  $u_m$  can be considered as constant over a switching time period. Consequently, for  $m_a \leq 1$  ( $\hat{U}_m \leq \hat{U}_c$ ), the discontinuous switching function  $S^*$  can be replaced by its time-dependent duty cycle d(t) [13], as

$$d(t) = \frac{1}{2} \left( \frac{u_m(t)}{\hat{U}_c} + 1 \right)$$

(2-5)

where  $\hat{U}_{c}$  is amplitude of the triangular carrier.

By inserting (2-5) as  $S^*$  into (2-4), an averaged time-continuous model of the sinusoidal PWM inverter can be obtained as

$$u_{i} = V_{dc} \frac{u_{m}(t)}{\hat{U}_{c}} = Mu_{m}(t)$$

(2-6)

where  $M = \frac{V_{dc}}{\hat{U}_c}$  is the modulating gain. Therefore, the bridge inverter in Figure 2.6 can

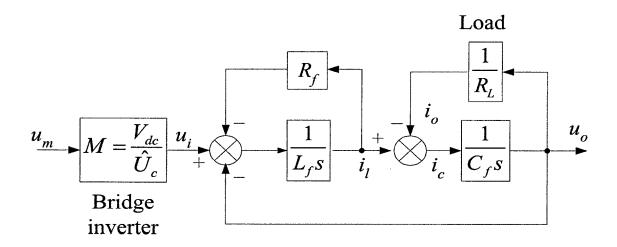

be modeled as a controlled voltage source with the gain of M, as described in (2-6). The equivalent circuit of the averaged sinusoidal PWM inverter with LC filter is shown in Figure 2.8.

Figure 2.8 Equivalent circuit of the averaged sinusoidal PWM inverter.

Thus, we can use state-space function to describe the sinusoidal PWM inverter as (2-7). Here, the load is assumed to be a pure resistance, represented by  $R_L$ .

$$\frac{d}{dt} \begin{bmatrix} i_l \\ u_o \end{bmatrix} = \begin{bmatrix} -\frac{R_f}{L_f} & -\frac{1}{L_f} \\ \frac{1}{C_f} & -\frac{1}{R_L C_f} \end{bmatrix} \begin{bmatrix} i_l \\ u_o \end{bmatrix} + \begin{bmatrix} \frac{M}{L_f} \\ 0 \end{bmatrix} u_m$$

(2-7)

By applying Laplace transform, a linearized model can be easily derived as shown in Figure 2.9.

Figure 2.9 Linearized model of sinusoidal PWM inverter.

## 2.5 Summary

In this chapter, the basics of the sinusoidal PWM inverter are introduced. The focus is put on high frequency PWM, where the frequency of the triangular carrier is much higher than that of the modulating signal. The popular circuit topologies and PWM switching schemes are discussed briefly. Moreover, a linearized model of the sinusoidal PWM inverter is established. This model will be used in the later parts of the thesis.

## Chapter 3

## **Neural Network Based Control for**

## **SPWM Inverter**

#### 3.1 Introduction

The objective of UPS inverters is to provide a pure sinusoidal voltage with constant frequency and constant amplitude. Various controllers were used to achieve regulation. The controllers can be classified into two groups: analog-based and digital-based.

Most of the analog-based controllers were designed based on linearized model and traditional frequency-domain analysis. Some multiple-feedback-loop control strategies were proposed in [14][15]. Such schemes sense the current in the inductor (or capacitor) of the LC filter as the control signal of an inner feedback loop. An outer voltage feedback loop is incorporated to ensure a sinusoidal output voltage. Owing to the introduction of the inner current feedback loop, the output impedance of the inverter filter is decreased and the dynamic stiffness enhanced. The controlled inverter can produce a satisfactory sinusoidal output voltage within a certain load range. However, uniform performance cannot be obtained under extreme loading conditions, and THD

increases significantly when there is a nonlinear load. In addition, such schemes are analog-based. As a result, they have all the drawbacks of analog circuits, such as limited accuracy, uncompensated thermal drift, and need of recalibration.

Digital control schemes are all realized by software. They bring more flexibility than analog schemes. Microprocessor-based deadbeat control scheme was proposed in [16][17]. In this scheme, the capacitor voltage and its derivative (or capacitor current) are used to calculate the duration of the ON/OFF state of the switching devices, so that the capacitor voltage is forced to be equal to the reference voltage at each sampling instant. Although this technique can achieve good performance when the switching frequency is low (a few kHz), it has two major disadvantages: 1) high sensitivity to parameter variations; 2) high THD under nonlinear load conditions.

Modern Digital Signal Processors (DSP) are capable of executing over 50 million instructions per second (MIPS). Some complicated control algorithms, which are almost impossible to be realized by analog circuitry, can be flexibly implemented by DSP. In addition, there are many advantages in using DSP, e.g. the system parameters are free from the effects of aging and temperature drift. References [18]-[21] proposed different DSP-based control algorithms of inverters. However, although these algorithms could achieve good transient response and low THD under nonlinear loading conditions, the high computation demand increases the implementation difficulty as well as expense.

Numerous advances have been made in developing intelligent system, some inspired by biological neural networks. Researchers from many scientific disciplines are designing artificial neural networks to solve a variety of problems in pattern recognition, prediction, optimization, associative memory, and control. Conventional

approaches have been proposed for solving these problems. Although successful applications can be found in certain well-constrained environments, none is flexible enough to perform well outside its domain. Neural network (NN) provides exciting alternatives, and many applications could benefit from using them. An NN is a massively parallel computing systems consisting of an extremely large number of simple processors with many interconnections that simulates a real biological brain system. Therefore, the NN possesses the features of distributed representation and computation, learning ability, adaptability, inherent contextual information processing, and fault tolerance [22].

Power electronic systems are nonlinear indeed. Although there are many approaches to model power electronic circuits as low frequency behavior models [23] and hence various control methodologies can be applied to power electronic systems, the performance of the system against nonlinear loads is still poor. With specific reference to NN in control the following characteristics and properties of NN are important [24]:

- Nonlinear system,

- Parallel distributed processing,

- Hardware implementation,

- Learning and adaptation,

- Data fusion,

- Multivariable system.

From the control theory viewpoint, the ability of the NN to deal with nonlinear systems is perhaps most significant. This stems from its theoretical ability to

approximate arbitrary nonlinear mapping. The NN is, thus, very attractive for electronic to tackle strong nonlinearity of power electronic systems. It has already been employed in various control and signal processing applications in power electronics [25]-[27].

The NN is employed to perform waveform estimations of power electronics. Due to its strong abilities of parallel processing and data fusion, the NN is successfully applied to estimate distorted waveform generated by power electronic circuits [28]-[31]. Harmonic estimation or prediction also benefit from the NN [32]-[36].

In the control of dc/ac inverters, the NN has been introduced in the current control of inverters for ac motor drives [35]-[39], where the NN receives a phase-current error and generates PWM logic signals to drive the inverter switches. [40]-[42] presented a neural network application in the harmonic elimination of PWM inverter where the NN replaced a large and memory-demanding look-up table to generate the switching angles of the PWM inverter for a given modulation index.

Many architectures of NN have been reported. Although they have different elements and connections, they can be classified into two categories: dynamic (feedback, recurrent) and static (feedforward). Dynamic networks have feedback connections, which produce several stable points in networks. Dynamic networks are vital in many applications, like pattern recognition, signal processing and optimization. Static networks may have more than one layer. However, a neuron in one layer receives inputs only from neurons in the previous layer (or, in the case of the first layer, from the network input). The connection of several layers gives the possibility of more complex nonlinear mapping between the inputs and outputs. A number of results have been published showing that a feedforward network of multi-layer type can approximate arbitrarily well a continuous function. To be specific, it is proved that a continuous function can be arbitrarily well approximated by a feedforward network with only one

single internal hidden layer [24]. With these properties, static (feedforward) networks have great application potential in the modeling and control of nonlinear systems.

The loading conditions of a SPWM inverter can be quite complicated. The range may cover linear and nonlinear regions. When we attempt to introduce NN control to an inverter, an obvious difficulty is that not all the loading conditions that the inverter may encounter can be included into the model. A complete model of the control objectives, therefore, cannot be established. If a dynamic NN were employed, it would be very hard to describe the prescribed equilibrium (or steady-state matching) in the network. Our attention naturally turns to static NN, which has the property of nonlinear functional mapping. Our idea is to present an almost-perfect teacher, which can perform very well in simulation under all loading conditions, to a static (feedforward) NN. The teacher is actually a database composed of idealized input-output patterns. The training of the NN is a classical supervised training problem. Training an NN using a set of input-output data from a nonlinear plant can be considered as a nonlinear functional approximation problem. The training can be performed either on-line or off-line.

In on-line training, since the weights and biases of the NN are adaptively modified during the control process, it has better adaptability to nonlinear systems. The most popular gradient decent algorithm is back propagation. It is attractive because it is stable, robust and efficient. However, the back propagation algorithm involves a great deal of multiplication. If implemented in software, it needs a very fast digital processor. If implemented in hardware, it results in a rather complex circuitry and expensive solution [43].

Possible alternatives of the back propagation are perturbation-based algorithms, such as weight perturbation [44], chain-rule perturbation learning [45] or random weight change [46]. In these algorithms, the weights are perturbed and the gradients are

evaluated from the errors generated (instead of calculating the derivatives in back propagation). They are feasible for analogue VLSI implementation [47]. However, in real-time control of the power electronic system, there are no desired outputs to be presented to the NN since we have no a priori knowledge about the loading conditions. We can employ an NN emulator to identify the system behavior in order to determine the output error of the NN controller [48], but this NN emulator also need to be pretrained with data obtained from simulations or experiments. Therefore, in short, on-line training of the NN has better adaptability to the system, but at the cost of complicated computation and expensive implementation. Moreover, it is difficult to directly introduce on-line training into the control of UPS inverters. We consider that the on-line training of the NN does not fit the requirement of fast response of the real-time control of the UPS inverters.

Off-line training of the NN requires a large number of example patterns, which may be obtained through simulations. Although the weights and biases are fixed during the control process, the NN is a nonlinear system that has much better robustness than a linear system. Moreover, the forward calculation of the NN just involves addition, multiplication and sigmoidal-function waveshaping that can be implemented with simple and low-cost analogue hardware [49]. The fast response and low-cost implementation of the off-line trained NN are suitable for UPS inverter applications.

Simulations of an NN controller with off-line training for PWM inverter were reported in [50]. The NN learned the control law through simulations off-line. The inputs of the NN are time, present output voltage and last sampled output voltage. This NN may not have enough information to ensure a sinusoidal output voltage under various loading conditions. Moreover, only computer simulation, but no experimental results are reported.

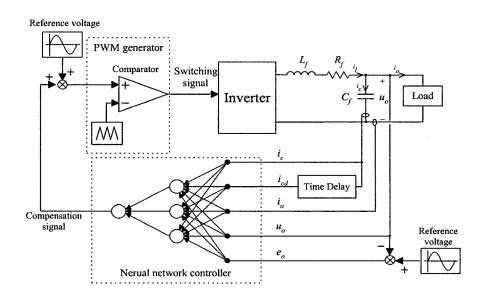

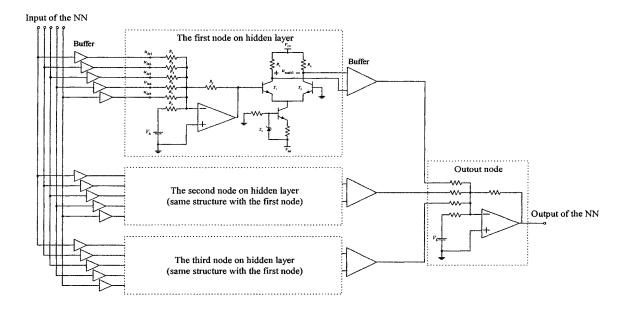

In this chapter, an analogue NN controller with off-line training for UPS inverter applications is proposed. It is a trial of applying NN in a quite simply way. The proposed NN controller is of feedforward type with supervised training. Example patterns are obtained from two simulation models, one is a traditional multi-loop controller for linear loads, the other is an idealized load-current-reference controller specially for nonlinear loads. A selected feedforward NN is trained to model this controller using back propagation algorithm. After training, the NN is used to control the inverter on-line. Simulation results show that the proposed NN controller can achieve low THD under nonlinear loading conditions and good dynamic response under transient loading conditions. To further verify the performance of the proposed NN controller, a hardware inverter with an analogue NN controller (constructed using operational amplifiers and resistors) is built. A PI controller with optimized parameters is built as well for comparison purposes. Experiment results confirm the simulation results and show the superior performance of the proposed NN controller. A discussion about the integrated circuit implementation of the proposed analogue NN controller will also be given.

## 3.2 Feedforward Neural Network

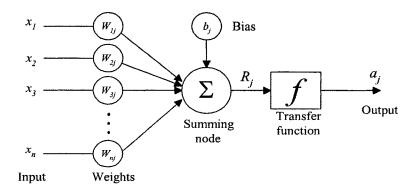

Neural networks are interconnections of artificial neurons that tend to emulate the human brain. One structure of the artificial neuron is shown in Figure 3.1.

Figure 3.1 Structure of an artificial neuron.

Here the individual element inputs,  $x_1, x_2, x_3, \ldots x_n$ , are multiplied by weights,  $W_{Ij}$ ,  $W_{2j}, W_{3j}, \ldots W_{nj}$ , and the weighted values are fed to the summing node. The neuron has a bias b, which is summed with the weighted inputs to form the net input  $R_j$ .  $R_j$  is then used as the argument of the transfer function f. Therefore, the output of the neuron can be written as:

$$a_J = f(\sum_i W_{ij} x_i + b_j) \tag{3-1}$$

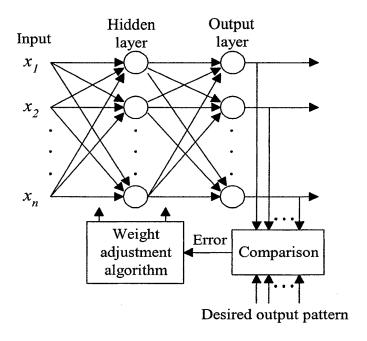

The transfer function can be of threshold type, sigmoid type, linear type and etc. Figure 3.2 shows the structure of a feedforward multi-layer network that has one hidden layer. The circles represent neurons, which have the structure as shown in Figure 3.1. A weight-adjustment feature is included when the back propagation is implemented. There can be more than one hidden layer. The number of hidden layers and the number of neurons on each layer depend on the complexity of the problem being solved and the desired accuracy.

Figure 3.2 Structure of a two layer feedforward neural network showing the back propagation training.

Neural networks can compute very fast in a parallel and distributed manner, and can approximate any complicate nonlinear functions by multi-compounding simple nonlinear functions through a training process, which is realized by repeated adjustments of weights and biases. The back propagation training algorithm is the most commonly used one for feedforward neural networks [51]. It updates the network weights and biases in such a direction that the performance function, usually the sum of square errors, will decrease most rapidly. A properly trained network tends to give a reasonable output when presented with inputs that have never been seen. The training is usually done by an off-line computer simulation program using a large number of example patterns. The example patterns can be obtained from analysis, simulation or directly from experiments if the model is totally unknown.

# 3.3 Proposed Neural Network Control of Inverter

To realize the proposed neural network control scheme on inverters, we have to present a large number of example patterns obtained under various loading conditions, and train the neural network properly to implement control law. Two controllers, one for linear loads, the other for nonlinear loads, are built and simulated using MATLAB [52] and SIMULINK [53].

# 3.3.1 Obtaining Example Patterns Under Linear Loading Conditions

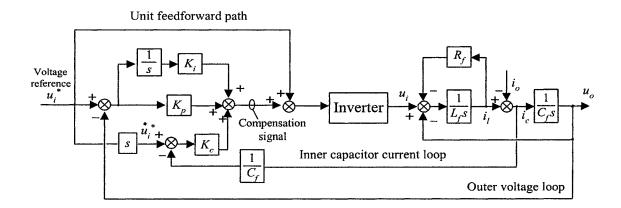

The control scheme for linear loads is shown in Figure 3.3. Under linear load conditions (resistive, capacitive, or inductive), a multiple-feedback-loop control scheme can give good performance [14][15]. Based on the traditional frequency-domain theory, an inner capacitor-current feedback loop is designed to reduce the phase lag caused by the filter inductor, so that the gain and phase margin can be improved. An outer voltage feedback loop can easily enable the output voltage to track the reference with small error and low THD. Different from the strategy proposed in [14][15], there is a unit feedforward path from the reference voltage (shown at the top of Figure 3.3), which is found to have advantages of reducing steady-state error and providing a high tracking accuracy to the reference. Although it may cause large overshoot in the dynamic response, the drawback can be overcome by optimizing the parameters of the voltage feedback loop. The whole modulation signal to PWM generator can be divided into two parts, one is a sinusoidal signal, and the other is called compensation signal (as marked in the middle of Figure 3.5) produced by feedback loops. Another important reason to

introduce the voltage feedforward loop is that the neural network can then use compensation signal as its desired output. During the training process of the neural network, we find that, as compared with the method using the net modulation signal as the desired output, the method using the compensation signal can greatly improve effectiveness of the training.

Variables marked with \* are reference variables

Figure 3.3 Multiple feedback loop control scheme to obtain example patterns under linear loads.

An inverter system with multiple-feedback-loop control scheme is modeled using MATLAB and SIMULINK. The full-bridge inverter is described by the following equation in SIMULINK:

$$u_i = \begin{cases} V_{dc} & (u_m \ge u_c) \\ -V_{dc} & (u_m < u_c) \end{cases}$$

(3-2)

where  $u_m$  is the instantaneous voltage of the modulating signal and  $u_c$  is the instantaneous voltage of the triangular carrier wave in the PWM. By using S-Function provided by SIMULINK, the full-bridge inverter can be easily built. The model of

Figure 3.3 in SIMULINK and the S-Function described the full-bridge inverter are listed in Appendix A.

It should be noted that a controller with fixed parameters could not be good for all kinds of linear loads. Each load is associated with a set of optimal parameters. We design the parameters for each load using frequency-domain analysis to ensure enough stability margin and small steady-state error, and fine-tune the parameters in the simulations for good transient responses. The compensation signal as shown in Figure 3.3 is collected as the desired output of the neural network. The output voltage and output currents (including load current, capacitor current) of the inverter are collected as the inputs to the neural network. Dozens of example patterns are obtained from the simulation results under different load conditions and controller parameters.

# 3.3.2 Obtaining Example Patterns Under Nonlinear Loading Conditions

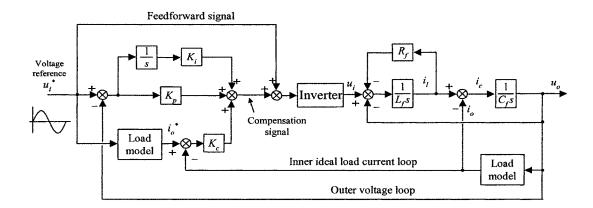

Many electrical loads nowadays are nonlinear. It is therefore essential to maintain the performance of a UPS inverter under nonlinear loading conditions. The nonlinear load in this Chapter is chosen to be a full-wave diode bridge rectifier with an output filter. The input current of the nonlinear load, namely the output current of the inverter, is usually non-sinusoidal with a rather large slope. The multiple-feedback-loop control scheme used under the linear loading conditions cannot perform satisfactorily. Thus, we should find another control scheme especially for nonlinear loads in order to obtain example patterns.

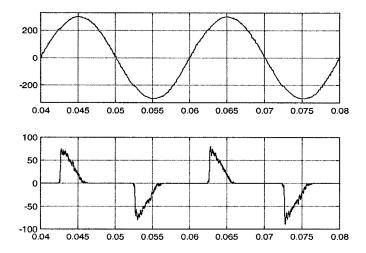

If the loading current of the inverter can be predicted, we can design a controller to keep trace of the output current. Following the control scheme used under the linear loading conditions, we change the inner capacitor-current loop to a load-current loop whose reference is obtained from an idealized load-current feedback control scheme (as shown in Figure 3.4), where a sinusoidal voltage is fed to a nonlinear load model to obtain a load-current reference. The actual load current is compared with this reference, and the error signal is used as the controller input. Although such a scheme is impossible to implement practically, it is actually an excellent teacher for the NN to learn to achieve the idealized performance. Figure 3.5 shows an example of the output waveform of an inverter controlled by an idealized load current feedback scheme. It can be seen that the performance of such a scheme is very good under nonlinear load conditions.

Variables marked with \* are reference variables