#### **Copyright Undertaking**

This thesis is protected by copyright, with all rights reserved.

#### By reading and using the thesis, the reader understands and agrees to the following terms:

- 1. The reader will abide by the rules and legal ordinances governing copyright regarding the use of the thesis.

- 2. The reader will use the thesis for the purpose of research or private study only and not for distribution or further reproduction or any other purpose.

- 3. The reader agrees to indemnify and hold the University harmless from and against any loss, damage, cost, liability or expenses arising from copyright infringement or unauthorized usage.

#### IMPORTANT

If you have reasons to believe that any materials in this thesis are deemed not suitable to be distributed in this form, or a copyright owner having difficulty with the material being included in our database, please contact <a href="https://www.lbsys@polyu.edu.hk">lbsys@polyu.edu.hk</a> providing details. The Library will look into your claim and consider taking remedial action upon receipt of the written requests.

Pao Yue-kong Library, The Hong Kong Polytechnic University, Hung Hom, Kowloon, Hong Kong

http://www.lib.polyu.edu.hk

## THE HONG KONG POLYTECHNIC UNIVERSITY DEPARTMENT OF ELECTRONIC AND INFORMATION ENGINEERING

## Fundamental Research on Electronic Design Automation in VLSI Design - Routability

Lu Jingwei

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Philosophy

February, 2010

# CERTIFICATE OF ORIGINALITY

I hereby declare that this thesis is my own work and that, to the best of my knowledge and belief, it reproduces no material previously published or written, nor material that has been accepted for the award of any other degree or diploma, except where due acknowledgement has been made in the text.

\_\_\_\_\_ (Signed)

(Name of student)

# Abstract

As the feature size of integrated circuits is revolutionized into nanometer scale, delay of interconnection has become the dominant factor instead of the transistor internal delay. As a result, new demands on interconnection have been proposed to the developers, and they usually enhance the routability of the chip so as to improve the performance of interconnection. Under the general research topic of routability, our work is focused on congestion prediction, clock network synthesis, clock gating design and global routing. They are all critical steps regarding routability concerns in the VLSI physical design.

In the early stages of the physical design, congestion prediction is necessary for the routability evaluation. An accurate estimation of a placement result is an effective metric to evaluate the behavior of the corresponding placer. In our work we propose three models, shortest Manhattan distance (SMD) model, Detour model and 3-step approach, for congestion prediction. The two major techniques applied in modern global routers, the detoured routing as well as the rip-up and rerouting, are considered in our work for further enhancement on estimation accuracy. The experimental results of our work present a progress on the performance compared to the previous congestion models.

The behavior (timing delay) of clock network synthesis (CNS) is mainly determined by the clock skew and the PVT (Process, Voltage and Temperature) variation factors. In our work, we develop two new clock network synthesizers (DMST and DMSTSS) with several novel techniques to tackle these issues. A dual-MST based perfect matching and a hierarchical buffer sizing are proposed to handle the clock latency range (CLR), which is the major metric for performance evaluation. An iterative buffer insertion approach and a dual-MZ blockage handling technique are developed for a proper distribution of buffers and wires. Internal nodes of the clock tree are relocated based on the delay estimation by SPICE simulation. The clock skew can be further reduced in this procedure. Slew table construction is designed to conform to the constraint on slew rate. In the experimental results it is shown that our synthesizers can effectively reduce the CLR in a much shorter runtime.

In the modern synchronous digital circuits, the clock network consumes a great share of the total power cost. Therefore, it is necessary to engage masking gates to reduce its power usage. This technique turns off the according clock tree sections during their idle periods. In the previous clock gating works, switched capacitance is a major metric to denote the power usage of the clock network and the according controller network. Two clock gating works, HKPUcg and HKPUst, are proposed in this thesis. HKPUcg aims at minimizing the switched capacitance, and the objective of HKPUst is reducing the clock skew. Two novel methods of power aware topology generation are proposed, respectively. Moreover, a new decision technique on gate insertion is developed to further reduce the switched capacitance and balance the delay difference. From the experimental results, we can see that our clock gating works can effectively reduce the total power usage. By SPICE simulation, the clock skew is small.

Among the modern global routers, the technique of iterative rip-up and rerouting is widely applied. Based on this technique, we develop two methods of dynamic steiner point relocation and edge-based maze routing to further reduce the overflow and shorten the wirelength. The first approach is implemented in constant time with a new data structure constructed for pins, steiner points and subnet connection. The second approach is built up based on the propagation among the global edges instead of global bins. From the experimental results, we can see that our router is efficient and robust compared to the previous state-of-the-art global routers.

# Acknowledgements

At first, I would like to express the deepest gratitude to my chief supervisor, Dr. Bruce Chiu-Wing Sham, for his excellent direction, patient instruction and generous help throughout the past two years. During my MPhil study, Dr. Sham not only enriches my academic experiences, broadens my horizon of research, but also impresses me with his kindness and tolerance. Without him I could not finish my MPhil study, and it is a great honor of mine to study under his supervision.

Secondly, I would like to express the sincere thanks to my co-supervisor, Prof. Evangeline Fung-Yu Young, for her guidance and cares to me. Besides research instructions, Prof. Young also gives me encouragement to pursue higher goals in my career life. Without her I could not proceed my study at VLSI CAD, let alone my future works. It is beyond my words to express my appreciation to her.

Thirdly, I would like to thank my colleague, William Chow-Wing Kai, for his support to my research work. I have benefited a lot from the discussion with him regarding academic problems and living concerns. It is a memorable experience of mine to work with him.

Meanwhile, I appreciate the cares and helps from my parents during my study in Hong Kong. I could never pursue my oversea education without their comprehension and support.

# Contents

| 1        | Intr                  | oduction                                      | 1  |

|----------|-----------------------|-----------------------------------------------|----|

|          | 1.1                   | Motivation                                    | 1  |

|          | 1.2                   | Our Contribution                              | 2  |

|          | 1.3                   | Outline of Thesis                             | 3  |

| <b>2</b> | Bac                   | kground                                       | 5  |

|          | 2.1                   | Overview of VLSI Physical Design              | 5  |

|          | 2.2                   | Metrics Analysis                              | 7  |

|          |                       | 2.2.1 Signal Delay Models                     | 7  |

|          |                       | 2.2.2 Clock Skew and Clock Latency Range(CLR) | 9  |

|          |                       | 2.2.3 Clock Slew Rate                         | 10 |

|          |                       | 2.2.4 Congestion Probability and Overflow     | 11 |

|          |                       | 2.2.5 Power on Capacitance and Wirelength     | 12 |

| 3        | $\operatorname{Lite}$ | rature Review                                 | 15 |

|          | 3.1                   | Overview                                      | 15 |

|          | 3.2                   | Congestion Prediction                         | 15 |

|          | 3.3                   | Clock Network Synthesis                       | 17 |

|          | 3.4                   | Clock Gating Design                           | 18 |

|          | 3.5                   | Global Routing                                | 19 |

|          | 3.6                   | Summary                                       | 21 |

| 4        | Cor | gestion Prediction 2                                 | 22 |

|----------|-----|------------------------------------------------------|----|

|          | 4.1 | Overview                                             | 22 |

|          | 4.2 | Problem Formulation                                  | 22 |

|          | 4.3 | Analysis of Congestion Models                        | 24 |

|          | 4.4 | SMD Model                                            | 24 |

|          | 4.5 | Detour Model                                         | 26 |

|          |     | 4.5.1 Estimation of Detoured length                  | 27 |

|          |     | 4.5.2 Congestion Estimation                          | 28 |

|          | 4.6 | 3-Step Approach                                      | 30 |

|          |     | 4.6.1 Preliminary Estimation                         | 31 |

|          |     | 4.6.2 Detailed Estimation                            | 32 |

|          |     | 4.6.3 Congestion Redistribution                      | 33 |

|          | 4.7 | Experimental Results                                 | 35 |

|          | 4.8 | Summary                                              | 41 |

| <b>5</b> | Clo | ck Network Synthesis                                 | 42 |

|          | 5.1 | Overview                                             | 42 |

|          | 5.2 | Problem Formulation                                  | 43 |

|          | 5.3 | Methodology                                          | 44 |

|          |     | 5.3.1 A Dual-MST based Geometric Perfect Matching    | 46 |

|          |     | 5.3.2 Hierarchical Buffer Sizing                     | 50 |

|          |     | 5.3.3 Iterative Buffer Insertion                     | 53 |

|          |     | 5.3.4 Dual-MZ Blockage Handling Technique            | 55 |

|          |     | 5.3.5 Merging Point Relocation with SPICE Simulation | 56 |

|          |     | 5.3.6 Slew Table Construction                        | 59 |

|          | 5.4 | Experimental Results                                 | 61 |

|          | 5.5 | Summary                                              | 67 |

| 6        | Clo | ck Gating Design                                     | 71 |

|          | 6.1 | Overview                                             | 71 |

|    | 6.2          | Problem Formulation                            | 2 |

|----|--------------|------------------------------------------------|---|

|    |              | 6.2.1 Clock Tree and Controller Tree           | 2 |

|    |              | 6.2.2 Switched Capacitance                     | 4 |

|    | 6.3          | Methodology                                    | 5 |

|    |              | 6.3.1 Power Aware Topology Generation          | 6 |

|    |              | 6.3.2 Concurrent Gate and Buffer Insertion     | 8 |

|    | 6.4          | Experimental Results                           | 0 |

|    | 6.5          | Summary                                        | 7 |

| 7  | Glo          | bal Routing 89                                 | 9 |

|    | 7.1          | Overview                                       | 9 |

|    | 7.2          | Problem Formulation                            | 0 |

|    | 7.3          | Methodology                                    | 1 |

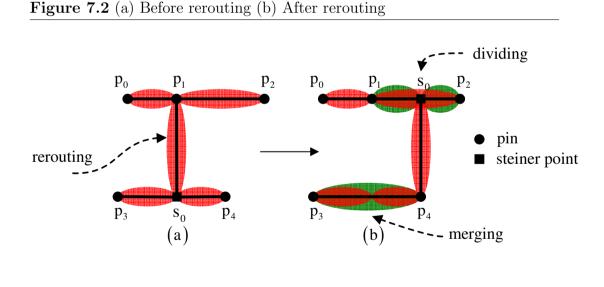

|    |              | 7.3.1 Dynamic Steiner Point Relocation         | 1 |

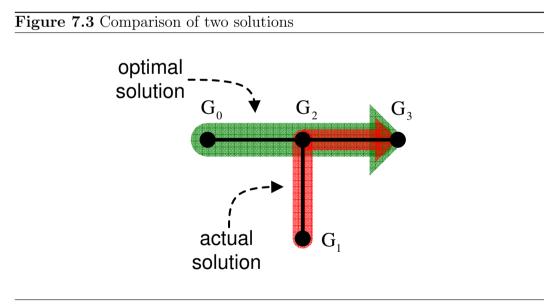

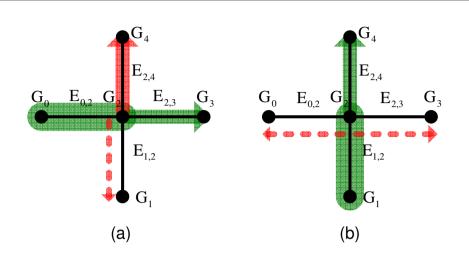

|    |              | 7.3.2 Edge-based Monotonic and Maze Routing 94 | 4 |

|    | 7.4          | Experimental Results                           | 7 |

|    | 7.5          | Summary                                        | 9 |

| 8  | Cor          | nclusion 104                                   | 4 |

| Bi | Bibliography |                                                | 7 |

# List of Figures

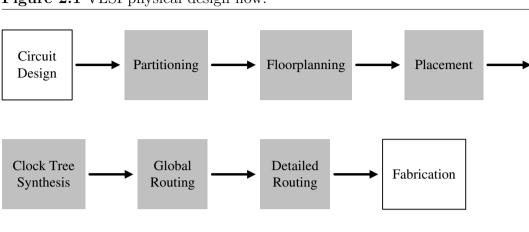

| 2.1 | VLSI physical design flow.                                                                                   | 6  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

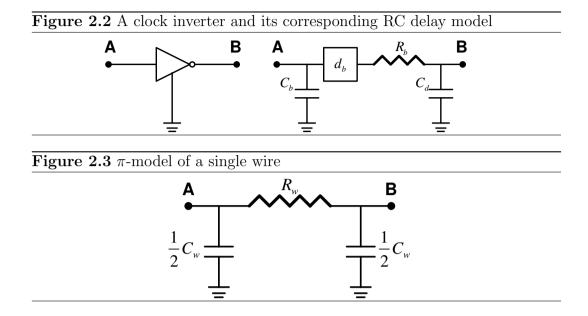

| 2.2 | A clock inverter and its corresponding RC delay model $\ . \ . \ .$                                          | 8  |

| 2.3 | $\pi$ -model of a single wire $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 8  |

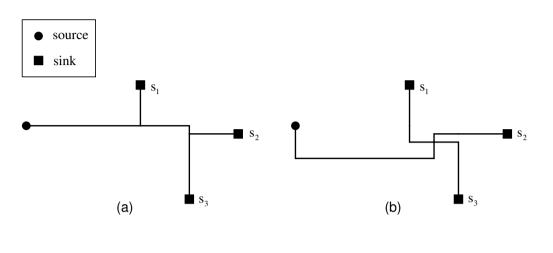

| 2.4 | (a) Non-equidistant clock tree (b) Equidistant clock tree                                                    | 10 |

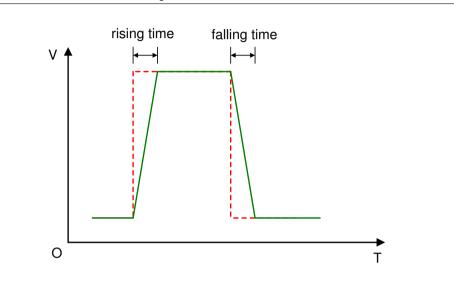

| 2.5 | Slew effect on square wave                                                                                   | 11 |

| 2.6 | The tracks between tile $T_1$ and tile $T_2$                                                                 | 12 |

| 2.7 | The capacitance accumulation in clock tree                                                                   | 13 |

| 2.8 | (a) Minimum spanning tree (b) Steiner tree                                                                   | 14 |

| 4.1 | SMD model for a two-pin net                                                                                  | 25 |

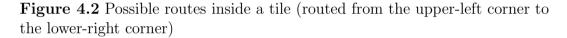

| 4.2 | Possible routes inside a tile (routed from the upper-left corner                                             |    |

|     | to the lower-right corner)                                                                                   | 25 |

| 4.3 | Detour model for a two-pin net                                                                               | 29 |

| 4.4 | An example of computing the congestion measures for a two-pin                                                |    |

|     | net in the detailed estimation step                                                                          | 32 |

| 4.5 | An example of congestion redistribution                                                                      | 34 |

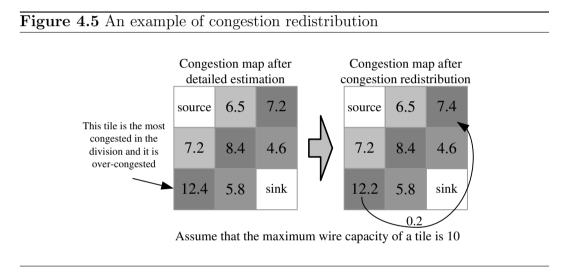

| 4.6 | Congestion maps of horizontal wires (case: $ibm03$ )                                                         | 37 |

| 4.7 | Error distribution of horizontal wires (case: ibm03) $\ldots$                                                | 38 |

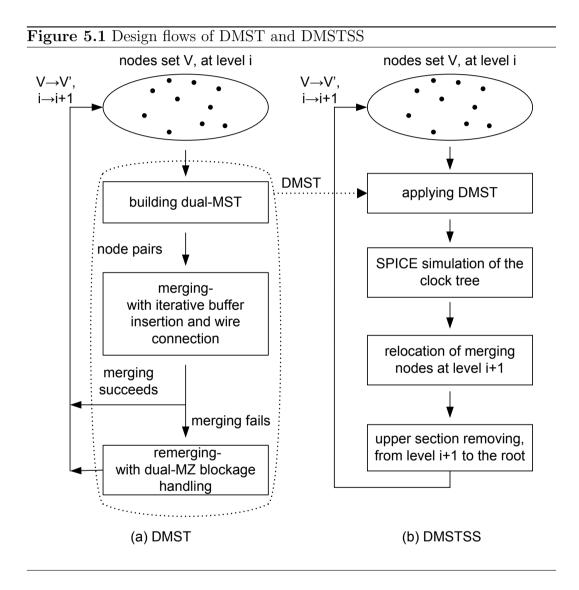

| 5.1 | Design flows of DMST and DMSTSS                                                                              | 45 |

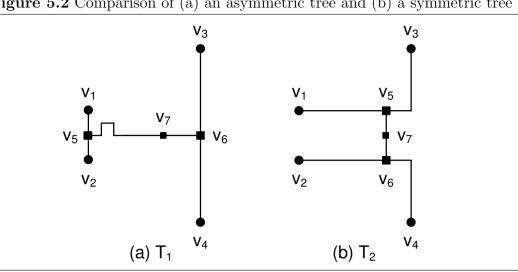

| 5.2 | Comparison of (a) an asymmetric tree and (b) a symmetric tree                                                | 48 |

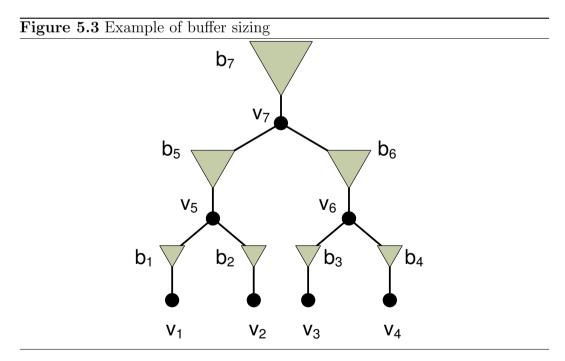

| 5.3 | Example of buffer sizing                                                                                     | 50 |

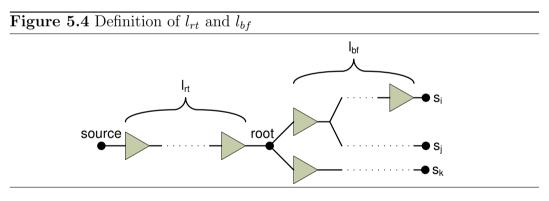

| 5.4 | Definition of $l_{rt}$ and $l_{bf}$                                                                          | 52 |

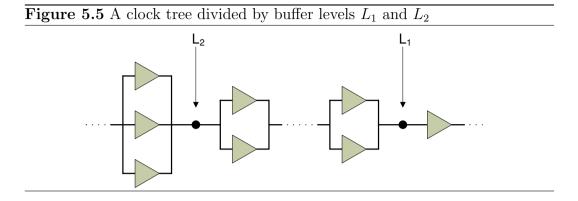

| 5.5        | A clock tree divided by buffer levels $L_1$ and $L_2$                  | 53 |

|------------|------------------------------------------------------------------------|----|

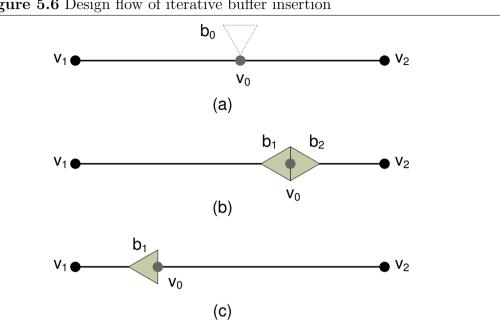

| 5.6        | Design flow of iterative buffer insertion                              | 54 |

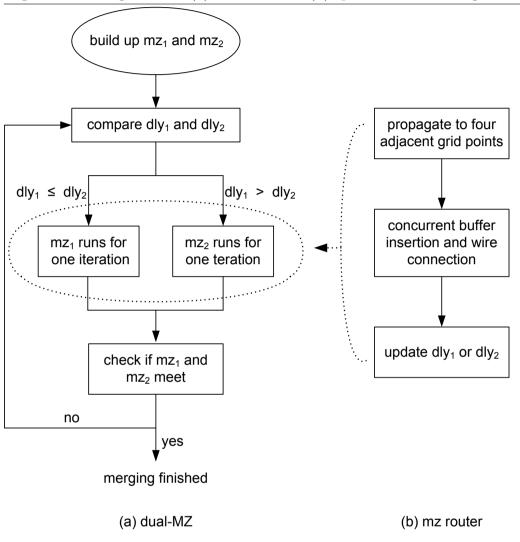

| 5.7        | Design flow of (a) dual-MZ and (b) specific maze routing $\ . \ . \ .$ | 57 |

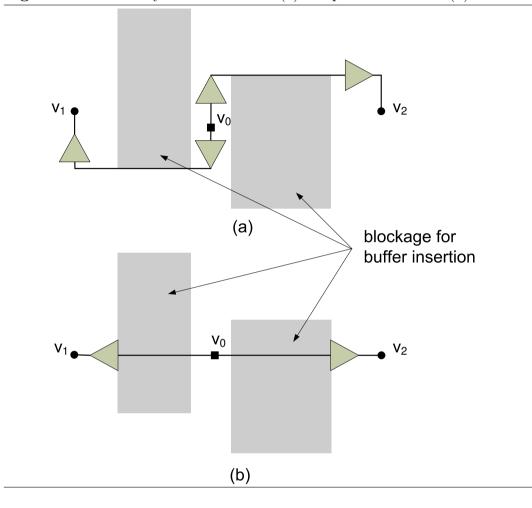

| 5.8        | Possible synthesis results of (a) complete detour and (b) dual-        |    |

|            | MZ                                                                     | 58 |

| 5.9        | DMSTSS synthesis result of the benchmark $ispd09fnb1$                  | 59 |

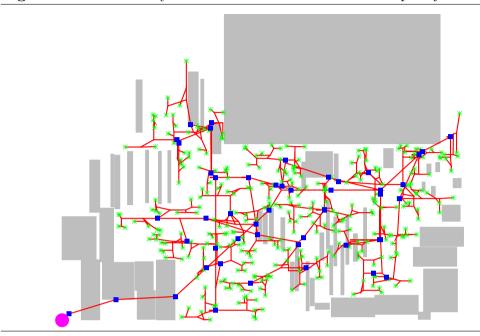

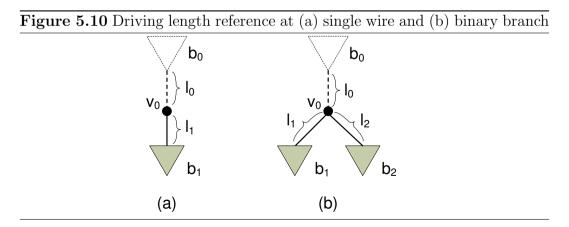

| 5.10       | Driving length reference at (a) single wire and (b) binary branch      | 60 |

|            |                                                                        |    |

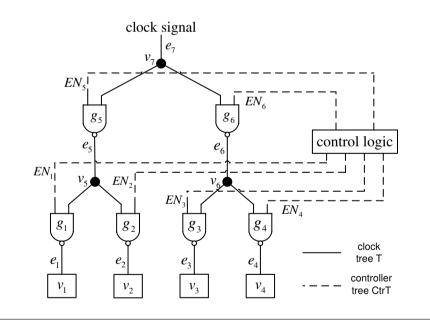

| 6.1        | A gated clock binary tree                                              | 73 |

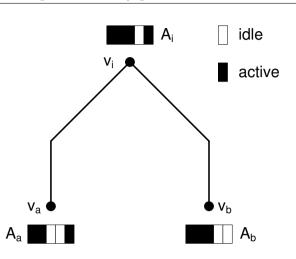

| 6.2        | An example of activity pattern transmission                            | 74 |

|            |                                                                        |    |

|            |                                                                        |    |

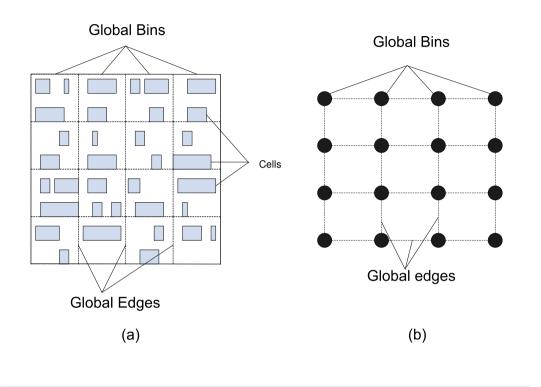

| 7.1        | (a) Chip decomposition (b) Grid graph                                  | 91 |

| 7.1<br>7.2 | <ul><li>(a) Chip decomposition (b) Grid graph</li></ul>                |    |

|            |                                                                        | 93 |

# List of Tables

| 4.1 | Notations in congestion prediction                              | 23 |

|-----|-----------------------------------------------------------------|----|

| 4.2 | Percentage of detoured nets                                     | 27 |

| 4.3 | Improvement of wirelength estimation                            | 28 |

| 4.4 | Information of the test cases                                   | 35 |

| 4.5 | Comparison on the mean and standard deviation of error of the   |    |

|     | congestion models for more congested circuits                   | 36 |

| 4.6 | Comparison of the runtime of the congestion models              | 39 |

| 4.7 | Comparison on the mean of error of the congestion models when   |    |

|     | the circuit is global routed by AMGR                            | 40 |

| 4.8 | Comparison on the mean of error of the congestion models when   |    |

|     | the circuit is global routed by MaizeRouter                     | 40 |

| 5.1 | Buffer configuration                                            | 61 |

| 5.2 | Circuit information of the benchmarks from ISPD 2009 $\ldots$ . | 62 |

| 5.3 | Variation of the transistor                                     | 63 |

| 5.4 | Comparison between different matching methods                   | 64 |

| 5.5 | Comparison of computing platforms                               | 64 |

| 5.6 | Comparison among DMSTSS, the three synthesizers in ASP-         |    |

|     | DAC 2010 and the best result in ISPD 2009                       | 65 |

| 5.7 | Comparison among DMSTSS, the three synthesizers in ASP-         |    |

|     | DAC 2010 and the best result in ISPD 2009                       | 66 |

| 5.8  | Comparison among DMSTSS, the three synthesizers in ASP-    |   |

|------|------------------------------------------------------------|---|

|      | DAC 2010 and the best result in ISPD 2009                  | 7 |

| 5.9  | Comparison of CLR for fixed buffer sizing in DMSTSS 68     | 3 |

| 5.10 | Comparison of CLR for fixed buffer sizing in DMST 69       | 9 |

| 5.11 | Circuit information of the benchmarks from r1 to r5        | ) |

| 5.12 | Performance of DMSTSS on r1 to r5                          | ) |

| 6.1  | Buffer and gate configuration                              | ) |

| 6.2  | Clock skew and switched capacitance with gate insertion 82 | 2 |

| 6.3  | Clock skew and switched capacitance with gate insertion 83 | 3 |

| 6.4  | Circuit information of the benchmarks from r1 to r5 83     | 3 |

| 6.5  | Performance comparison between HKPUcg and other clock gat- |   |

|      | ing works                                                  | 4 |

| 6.6  | Performance comparison between HKPUcg and other clock gat- |   |

|      | ing works                                                  | 4 |

| 6.7  | Performance comparison between HKPUcg and other clock gat- |   |

|      | ing works                                                  | 5 |

| 7.1  | Notations in global routing                                | ) |

| 7.2  | Information of ISPD08 benchmarks                           | 3 |

| 7.3  | Performance comparison based on ISPD08 benchmarks 99       | 9 |

| 7.4  | Performance comparison based on ISPD08 benchmarks 100      | ) |

| 7.5  | Performance comparison based on ISPD08 benchmarks 102      | 1 |

| 7.6  | Comparison of HKPUgr and NCTU on the modified ISPD08       |   |

|      | benchmarks, with 2 tracks removed on each edge 102         | 2 |

| 7.7  | Comparison of HKPUgr and NCTU on the modified ISPD08       |   |

|      | benchmarks, with 2 tracks added on each edge               | 3 |

## Chapter 1

# Introduction

## 1.1 Motivation

In the modern time, integrated circuit (chip) is widely applied in the electronic equipments. Almost every digital appliance, like computer, camera, music player or mobile phone, has one or several chips on its circuit board. VLSI, the acronym of very-large-scale integration, is the process of combining a huge amount of transistor-based circuits into a single chip. Complex of electronic components are designed, specified then fabricated on the substrate, which is made of pure semiconductor materials. Physical design is at the lowest level of the VLSI design flow, it is the process of determining the actual location of all the active devices and interconnecting the pins inside the boundary of a VLSI chip. As the improvement on the craft of semiconductor manufacture proceeds into deep-submicron and nanometer scale and the enlargement of integration scale into billions of transistors, designing demands of much stricter rules (power usage, process variation, timing closure) have been proposed. It is no longer applicable for the manual operation to deal with problems of such huge difficulty.

Instead of traditional manual design, electronic design automation (EDA) is applied to automate the design process of semiconductors and improve the efficiency of the work. The major objective of EDA is to develop a category of

CAD (computer aided design) software tools. Meanwhile, the according performance simulation can be applied in PC or supercomputers, which is very attainable. In the procedure of EDA, fundamental comprehension on the VLSI technology and the knowledge on the feature attributes are important skills for the designers. Therefore, they can efficiently fill the gap between system specification and chip manufacture. By means of problem formulation, algorithm devision and performance evaluation, designers are supposed to build up a program to automate the physical design in a computer.

Due to the prevalent application of nanometer-scale technology in the modern integrated circuits, the excessively high density of interconnections will result in negative effect towards the routability of the chip. This is because the over-congestion of wires will severely damage the quality of the signal transmission in each network, therefore impair the circuit performance. As a result, routability optimization has become a major concern in the VLSI physical design. In our research work, routability is improved in several correlated steps: congestion prediction, clock tree synthesis and global routing.

### 1.2 Our Contribution

In VLSI physical design, our research work is focused on the topic of routability. It includes both the estimation and the implementation of the interconnections of the networks. Our contribution is composed of four parts:

Congestion Prediction. We propose three models (SMD model, detour model and 3-step approach) to evaluate the congestion in early stages. Based on the packing results of a placer, the grade of congestion of all the tiles on the chip can be estimated by our prediction models. The result of prediction is an effective metric to evaluate the performance of the according placer, therefore enhance the routability of the chip and facilitate the network interconnection (routing) in later stages.

- 2. Clock Network Synthesis. In our work, we develop two synthesizers (DM-STSS and DMST). Overall six novel techniques are proposed to improve the performance. A merging node relocation approach is devised to reduce the clock skew, which is the major concern in CNS. By our blockage handling approach, distribution problems for buffer insertion are successfully solved, and the additional resource cost is very low. Besides, the capacitance usage, although a less important concern, is also reduced by our merging approach.

- 3. Clock Gating Design. It is an extended work based on the clock network synthesis. In clock gating design, the power usage of the network becomes the major concern. In this thesis, two clock gating works (HKPUcg and HKPUst) are proposed. An improved power aware topology of the clock tree is implemented. Meanwhile, a decision technique on clock gate insertion is developed to reduce the resultant switched capacitance thus cut down the power usage. Our synthesizers can guarantee exact zero skew without violation on the slew rate constraint.

- 4. Global Routing. We propose a new global router, HKPUgr, for inter-bin connection of all the networks in the chip. We developed two novel methods, a dynamic steiner point relocation technique as well as an edge-based maze routing technique, to reduce the wirelength and via length. In each iteration of iterative rip-up and rerouting, our approach is proved to achieve the optimum solution based on a common composite cost function of global routing.

### 1.3 Outline of Thesis

This thesis is organized as follows. We give the introduction of our thesis in chapter 1. The background knowledge regarding this thesis is presented in chapter 2, with the overview of the VLSI physical design and some discussions on the related performance metrics. Previous research works are reviewed and analyzed in chapter 3. Three models of congestion prediction is discussed in chapter 4 with comprehensive analysis. Two clock network synthesizers with six technical enhancements are proposed in chapter 5. Clock gating design is proposed in chapter 6 to reduce the power usage of the clock network by gate insertion. A new global router is proposed in chapter 7 to reduce the total wirelength. Finally, we reach our conclusion in chapter 8.

## Chapter 2

# Background

## 2.1 Overview of VLSI Physical Design

Modern VLSI design is usually divided into four concatenated stages: behavioral design, structural design, logic design and physical design. In the VLSI physical design, the source code at register transfer level (RTL) in hardware description language (HDL) is converted into specific circuit layout for manufacture. VLSI physical design is typically solved in a hierarchical framework. For problem simplification with less concerns of optimization involved, each design stage would be mostly independently improved. Meanwhile, correlated optimization concerns among various stages should also be engaged, in order to maintain the total layout problem manageable for the subsequent stages (fabrication). The procedure of VLSI physical design is generally composed of five steps: partitioning, floorplanning, placement, clock tree synthesis, global routing and detailed routing. The design flow is shown by the gray rectangles in figure 2.1. Sometimes partitioning, floorplanning and placement are summarized into a superior stage of placement, and clock tree synthesis, global routing and detailed routing are summarized into a superior stage of routing.

Partitioning divides a circuit into smaller parts. The objective is to restrict each part within a prescribed range. Meanwhile, the amount of interconnections among different components is minimized so as to enhance the routability

Figure 2.1 VLSI physical design flow.

and reduce the power usage. Partitioning is a fundamental step of the VLSI physical design, it transforms a large problem into smaller ones of manageable sizes. In the literature, the research works on partitioning mainly include iterative partitioning algorithms [45, 28, 48, 81] and ratio cut approaches [73, 51].

Floorplanning is applied after partitioning to determine the approximate location of each module in the chip area. A good approach of floorplanning should minimize the total chip area, facilitate the following routing stage and reduce the signal delay. Modules with higher density connections should be placed closer to each other. In retrospect to the past, various approaches concerning floorplanning have been proposed. They are mainly composed of rectangular dual graph approach [47], planar triangulated graph approaches [90, 93], hierarchical approach [77], simulated annealing approach [97] and floorplan sizing approach [67, 87].

In placement, each module has fixed shape and terminal locations. The main target is to determine the optimal position of every module on the chip. The placement algorithms can be divided into two main categories: iterative improvement and constructive placement. General methods include force-directed [2, 34, 66], simulated annealing [82], partitioning [23] and resistive network [16].

The major target of clock network synthesis is to connect all the synchronous signal receivers together with the signal source. Buffer insertion, sizing and wire customization are also engaged to synthesize the work and further improve the timing performance. The basic two approaches of clock tree construction are the top-down procedure [40] and the bottom-up procedure [41]. There are also two general methods of signal delay computation: linear delay estimated by wirelength and Elmore RC delay model [26].

In global routing, the grid is decomposed into small rectangles, which are named global bins. Only inter-bin connection among the pins of each network is applied in global routing. It is aimed at reducing the degree of congestion and the total wirelength. A good global router will evenly distribute the congestion over the whole routing area. The general routing methods include multi-commodity flow-based approaches [6, 85] and single-turn routing approach [43].

Detailed routing follows the global routing and implements the interconnections inside the global bins. Track assignment between global bins is also completed. The general approaches include channel routing [78] and hierarchical routing [4].

### 2.2 Metrics Analysis

In this section, we introduce the major metrics for performance evaluation in this thesis. Generally, the evaluation is based on the result regarding two items: (1) timing delay (2) power consumption. Both of the two metrics should be minimized in order to improve the performance of our research work.

#### 2.2.1 Signal Delay Models

In clock tree synthesis, there are plenty of delay models in different orders. By applying these models, signal delay at any point of the clock network can

be calculated. Linear delay model is a simple model for delay computation and balancing. The pathlength between a clock sink to the source is used to denote its according timing delay. Besides, Elmore RC model [26] is a more effective delay model. Compared to the linear model, Elmore RC model is more accurate together with increased complexity of computation.

An example of RC delay model of a buffer is shown in figure 2.2. The corresponding formula to calculate the buffer delay is shown as below

$$D_B = d_b + R_b \times C_d \tag{2.1}$$

where  $C_d$  means the load capacitance at point B,  $d_b$  is the internal delay of a buffer and  $R_b$  is the driver resistance of a buffer.

The delay model of a wire can be obtained in a similar way. We usually use  $\pi$ -model to denote the wire delay case, as illustrated in figure 2.3. Based on the Elmore delay model, the following equation is used to calculate the delay of a wire,

$$D_w = R_w \times \left(\frac{1}{2} \times C_w + C_d\right) \tag{2.2}$$

#### 2.2.2 Clock Skew and Clock Latency Range(CLR)

Let S denote the set of sinks,  $S = \{s_1, \ldots, s_{|S|}\}$ .  $s_i$  is the *ith* sink, and  $d_{s_i}$  represents the internal delay between the source and the sink  $s_i$ . The skew of a clock network means the maximum difference of the source-to-sink delay among all the sinks. To minimize the skew, we need to build a clock network with all  $d_{s_i}$  as close as possible. Notice that the skew is not determined by the average delay of the sinks, but by the difference between the maximum delay and the minimum delay. The equation for clock skew  $(C_s)$  calculation is shown as below.

$$C_s = \max\{d_{s_i} | \forall s_i \in S\} - \min\{d_{s_i} | \forall s_i \in S\}$$

$$(2.3)$$

Two examples in linear delay model are shown in figure 2.4. Figure 2.4(*a*) is a non-equidistant solution. We can find that  $d_{s_1} < d_{s_2} < d_{s_3}$ , and the pathlength skew is  $(d_{s_3} - d_{s_1})$ . However, in figure 2.4(*b*)  $d_{s_1} = d_{s_2} = d_{s_3}$  and the pathlength skew is zero. Therefore, the equidistant one is better than the non-equidistant one, although its total wirelength is longer.

Due to the PVT (process, voltage and temperature) variation, the actual performance of the clock network would be worse than the theoretical estimation. In ISPD 2009 Clock Network Synthesis Contest [88, 39], a new metric named clock latency range (CLR) is formulated, concerning voltage variation additionally. Assume that the supplied voltage at each buffer vary between  $V_{dd_1}$  and  $V_{dd_2}$ . Therefore, two voltage sources  $V_{dd_1}$  and  $V_{dd_2}$  are applied in two simulation tests independently to simulate the voltage uncertainty. The metric of CLR is thus determined by the difference between the maximal and minimal clock skew values under these two given voltage supplies. CLR is the major

Figure 2.4 (a) Non-equidistant clock tree (b) Equidistant clock tree.

metric for performance evaluation in our CNS work.

$$p_{1_{max}} = \max\{d_{s_i} | \forall s_i \in S, V_{dd_1}\}$$

$$(2.4a)$$

$$p_{1_{min}} = \min\{d_{s_i} | \forall s_i \in S, V_{dd_1}\}$$

(2.4b)

$$p_{2_{max}} = \max\{d_{s_i} | \forall s_i \in S, V_{dd_2}\}$$

(2.4c)

$$p_{2_{min}} = \min\{d_{s_i} | \forall s_i \in S, V_{dd_2}\}$$

(2.4d)

$$CLR = \max\{p_{1_{max}}, p_{2_{max}}\} - \min\{p_{1_{min}}, p_{2_{min}}\}$$

(2.4e)

It can be concluded from the above equations that CLR represents both the deviation caused by delay models and the voltage variation.

#### 2.2.3 Clock Slew Rate

The slew rate of an electronic circuit is generally defined as the maximum rate of change on the signal transmission. In physical design, we estimate the duration of the signal rising (falling) time for slew rate maintenance in the circuit. Signal rising (falling) time means the timing delay from low-level to high-level (high to low). For better signal quality therefore shorter rising (falling) time, proper buffer insertion is necessary for driving power supply. An example of slew demonstration is shown in figure 2.5.

**Figure 2.5** Slew effect on square wave.

The restriction on clock slew describes the requirement on the rising (falling) signal rate. In some previous clock gating works [65, 11], it is defined to be the limited maximum load capacitance ( $\leq 20 \times C_g$ ). In ISPD 2009 Clock Network Synthesis Contest [88, 39], it is defined to be the lasting time from  $10\% \rightarrow 90\%$  ( $90\% \rightarrow 10\%$ ) of the signal strength, and the upper limit is set to be 100 ps. Slew rate violation at any point would be regarded as a failure of the whole clock network synthesis.

#### 2.2.4 Congestion Probability and Overflow

In congestion prediction, we model the degree of congestion for every tile in terms of the accumulated probability. Therefore, the congestion probability is the major metric for performance evaluation. In global routing, the maximal capacity for each edge is predefined, and the exceeding amount is named as overflow. We need to minimize the total overflow of the grid to improve the congestion. The whole chip area is decomposed into rectangular tiles, and  $e_{i,j}$

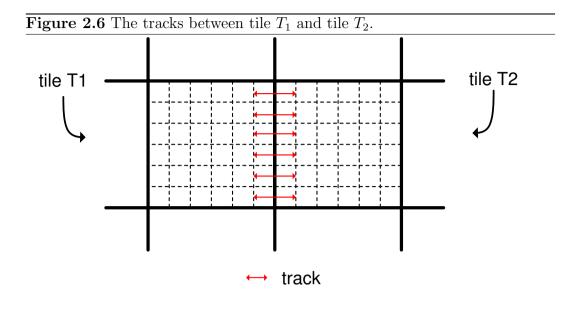

denotes the edge connecting the two adjacent tiles  $T_i$  and  $T_j$ . The respective capacity, demand and overflow on this edge are denoted as  $cap_{i,j}$ ,  $dem_{i,j}$  and  $ovf_{i,j}$ , respectively.  $ovf_{total}$  means the total overflow of the whole circuit. The capacity of an edge is determined by the number of tracks on it. As shown in figure 2.6, the red double-arrow line denotes a single track. Since there are six tracks in all on  $e_{1,2}$ , we have  $cap_{1,2} = 6$ . There will be overflow if the according demand of tracks  $dem_{1,2}$  exceeds the capacity. The general definition of  $ovf_{i,j}$ and  $ovf_{total}$  are shown as below.

$$ovf_{i,j} = \begin{cases} dem_{i,j} - cap_{i,j} & : dem_{i,j} > cap_{i,j} \\ 0 & : dem_{i,j} \le cap_{i,j} \end{cases}$$

(2.5)

$$ov f_{total} = \sum_{\text{all } e_{i,j}} ov f_{i,j}$$

(2.6)

#### 2.2.5 Power on Capacitance and Wirelength

Power consumption has become a critical issue in the system-on-chip (SoC) design. Besides previous research works, much more work remains to be done

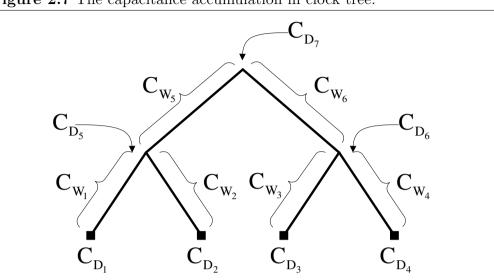

Figure 2.7 The capacitance accumulation in clock tree.

to automate the design flow. The equation for power usage computation is  $P = \frac{1}{2} \alpha C_d f V_{dd}^2$ .  $\alpha$  is the amount of transition periods,  $C_d$  is the total load capacitance of the network, f represents the signal frequency and  $V_{dd}$  denotes the voltage supply. According to the above equation, the consumed power is in a linear relationship with the total capacitance  $C_d$ . Therefore, total capacitance is optimized in our work to reduce the power consumption.

In clock network synthesis, both the buffers and the wires have their contribution to the capacitance. We denote the procedure of capacitance accumulation in figure 2.7, where  $C_{D_i}$  denotes the downstream capacitance, and  $C_{W_i}$ denotes the capacitance contributed by a segment of wire. Notice that when there are buffer insertions, downstream capacitance will be changed according to the input capacitance of buffers.

$$C_{D_5} = (C_{D_1} + C_{D_2}) + (C_{W_1} + C_{W_2})$$

(2.7a)

$$C_{D_6} = (C_{D_3} + C_{D_4}) + (C_{W_3} + C_{W_4})$$

(2.7b)

$$C_{D_7} = (C_{D_5} + C_{D_6}) + (C_{W_5} + C_{W_6})$$

(2.7c)

In global routing, the capacitance is approximated by the total wirelength.

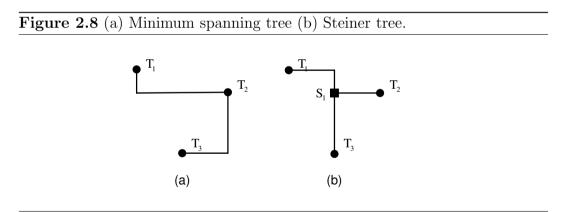

We can reduce the power consumption by means of wirelength minimization. Notice that in our work, based on the rectilinear grid, the distance between each pair of pins is not the Euclidean distance. Instead, the Manhattan distance is applied which equals the sum of the horizontal and vertical distance. Rectilinear steiner minimum tree (RSMT) is an efficient approach to achieve the shortest connection of a network with multiple pins. Insertion of proper steiner points is a necessary step in the steiner tree construction. Two comparable examples are shown in figure 2.8, where  $T_1, T_2, T_3$  are the three original pins to be connected, and  $S_1$  is an additional steiner point. The minimum spanning tree (MST) solution is shown in the left case, and the rectilinear steiner minimum tree is a better solution with a shorter wirelength caused. The rectilinear steiner minimum tree problem is NP-hard, but plenty of approximation schemes have been proposed with acceptable performance [35]. Some are with even optimal performance at particular cases.

## Chapter 3

# Literature Review

### 3.1 Overview

In this thesis, our research focus is located at the routability in VLSI physical design. During the early designing time, congestion prediction is applied in order to evaluate the degree of congestion in terms of respective probability on edge occupancy. In clock network synthesis, buffers cannot be inserted inside the blockage areas, which are preoccupied by macro blocks during the placement stage. Therefore, routability is maintained by proper buffer distribution for clock signal transmission. Clock gating design is an associating step of CNS aiming at power reduction. It is implemented by turn on/off active/inactive modules selectively. Subsequently except for the clock network, global routing implements the connection of the rest of the networks inside the chip area. Congestion and overflow are minimized and the according routability is maximized.

#### **3.2** Congestion Prediction

By virtue of the non-stopping reduction of feature size in the VLSI design, interconnection delay replaces the transistor delay to be the dominant factor on the signal delay. Therefore, routability has become a critical concern regarding the total timing performance of the circuit. However, improper design or operation in early stages will cause negative effect to the routing performance. For instance, arbitrary packing of modules will possibly lead to uneven distribution of congestion. As a result, the interconnection of such placement result may not be completed by global routers. Therefore, it is quite necessary to develop algorithms to improve routability during the placement or some other early designing steps, where congestion prediction is an effective technique of them. Congestion prediction can provide the probability of usage of all the tiles on the chip.

In retrospect to the past research achievements, several models have been proposed. In the works [14, 7, 57], a packing is divided into tiles and congestion is estimated in each tile, assuming that each net is routed in either L- or Z-shape. In [50], the congestion model used is the average net density on the boundaries of different regions in a floorplanning. In the papers [49, 54], probabilistic analysis is performed to estimate congestion and routability. They assume that all feasible routes have the same probability of being selected. In practice, routes of less bends are more desirable. In the papers [42, 96], extended versions of [54] are proposed. The authors take into account the impact of the number of bends in a routing path on the probability of occurrence of the path. However, the accuracy of their congestion models will depend on the accuracies of their predictions on the distribution of the number of bends in the routed circuit. The paper [99] proposed to predict congestion by using the Rent's rule. However, connections of the nets are already known in the floorplanning and placement stage, and we should be able to predict congestion more accurately than simply using the Rent's rule. The papers [94, 95] proposed to use global routers to estimate congestion, which will be more accurate but the runtime penalty is high. The paper [75] presented a probabilistic congestion prediction method based on routers intelligence. The paper [89]

gives an tutorial on all recent congestion technique and show the importance of the congestion prediction.

#### **3.3** Clock Network Synthesis

After placement, the interconnection of all the networks should be completed in the stage of routing, in which clock network synthesis is the first step. In VLSI circuits, digital modules are synchronized by receiving clock signals, which are transmitted from a source through the clock network. In clock network synthesis, the clock skew is usually a major concern, which represents the difference of the signal arrival time at all the terminals. In order to synchronize one circuit, each terminal must be reached by the clock signal within a small time range. Otherwise, the performance on synchronization is unacceptable. Regarding the maximum attainable frequency of operation in the circuits, the resultant clock skew of the synthesis work must be reduced into a predetermined range.

Clock skew minimization is a popular research topic during the past decades. Plenty of research achievements have been proposed by previous researchers. Some earlier proposed works concentrated on the distribution of wirelength between the source and the sinks to achieve delay equalization. Jackson [40] firstly presented a clock routing algorithm in a top-down course. Later, a geometric perfect matching was proposed in [41] in a bottom-up procedure. More improvements were also made to reach exact equidistant tree [25] for the clock network. Afterwards, delay balancing using Elmore delay model [26] became prevalent to acquire more accurate information on the timing delay. Clock tree with exact zero skew [92] was proposed by applying such balancing method. The deferred-merging and embedding (DME) technique [3, 10] was proposed to achieve zero skew with a shorter wirelength in the clock tree. In topology generation, some algorithms were proposed for both un-buffered [24] and buffered [12] clock trees respectively. In [31, 17] buffer insertion was involved for power supply and transition time reduction

In the recent years, tolerance on variation became a focus of attention. This is mainly due to the uncertainty of various uncertain factors inside a circuit, such as process [63, 100], voltage [76] and temperature [80]. In order to keep a chip stable and functioning well, methods with greater tolerance on variation are widely favored. Many researchers focused on robust algorithms for variation minimization. Techniques such as wire sizing [52], buffer sizing [15] and link insertion [71, 72] are applied. In ISPD 2009 clock network synthesis contest [88, 39], a voltage variation related objective, CLR, was formulated. Several new benchmarks were released accordingly. Subsequently, some related research works were proposed [86, 53, 55]. In [55], a dual-MST topology generation approach was devised and analyzed Its objective is to minimize the maximal edge cost during the weighted perfect matching.

#### **3.4** Clock Gating Design

In modern VLSI design, optimization on the power consumption is necessary, in case chip overheat and battery shortage (for portable devices). Clock network affords the synchronization of digital modules in the circuits. However, it is also quite power consuming. From statistics, it is shown that twenty to fifty percent of the dynamic power usage is contributed by the clock network [46]. Therefore, optimization on clock network is an effective way to make the chip less power consuming. At each clock period, only a small portion of the digital module set is active. The remaining modules are temporarily idle and they can be turned off for power saving. Based on this assumption, gated clock network is proposed in the sequential circuits for enable/disable control signal transmission. The principal idea is to turn off the idle modules and the according sections of the clock tree, and the unnecessary switching power can thus be cut down.

Clock gating can be applied on logic level [8], register-transfer-level level [22]

and architecture level [56], respectively. Nevertheless, optimization on these upper design levels may ignore the physical information and cause unnecessary detours or snaking wires. Upper level improvement may be offsetted by lower level implementation [30]. As a matter of fact, physical location of the modules should be taken into account during the clock gating design, in case wirelength overhead thus power waste.

Some achievements have been proposed with simultaneous logical and physical concerns. The design of activity-driven gated clock network was proposed in [91] and [27]. However, clock skew was only concerned by gate number balancing, and the contribution of wires were ignored. Meanwhile, the gate insertion was not applied concurrently within the topology generation. In [13], similarity of activity patterns between clock nodes was utilized, and the performance was improved with reduced power consumption. Instruction stream was proposed in [64] to simulate the probabilistic information of each module. In [65], a gating method regarding microprocessor design was developed to minimize the switched capacitance. However, no relationship of activities was concerned while merging each pair of nodes. Meanwhile, the resulted clock tree was still non-zero skew. Recently, a comprehensive technique was proposed in [11]. It is composed of a recursive computation on effective switched capacitance and a solution sampling method based on merging segment set. Despite the improvement on performance, the approach is very time and memory consuming, and the slew rate is too ideal (limit on downstream capacitance) which may not be applicable for industry use.

### 3.5 Global Routing

After clock network synthesis, global routing and detailed routing are applied to complete the interconnections of the rest of the networks. In the stage of global routing, the grid is decomposed into global bins. By such decomposition, all the pins are labelled with the coordinates of their according global bins. In each network, only the pins from different global bins need to be connected together. The specific inner-bin connection will be implemented in the detailed routing. Plenty of research works regarding global routing have been proposed with a great deal of improvements achieved [60]. Meanwhile, there were two global routing contests held in 2007 [62, 37] and 2008 [38], which greatly stimulated the research interests in global routing.

Among those state-of-the-art global routers, they generally employ two categories of basic techniques: (1) iterative rip-up and rerouting (2) multicommodity flow. The approach of iterative rip-up and rerouting does not confine routing selections in the early steps. However, it completes the task by means of numerous iterations of rerouting to gradually approach the final target of zero overflow. Repetitious rerouting would cost additional runtime to fulfill the work, thus focus is usually centralized on those congested area to make the processing efficient. The distribution of routing power is asymmetrical among all the nets, and congested nets usually get a big share. There are already a number of algorithms proposed based on it. Chi Dispersion [32] is a global routing approach implemented based on cost amplification. Labyrinth [44] is implemented based on the scheme of predictable routing. These are the two early global routers employing this technique. Recently, more and more global routers are presented, including Archer [68], BoxRouter [18], FGR [74], FastRoute [69, 70, 101], MaizeRoute [58, 59], NTHU-Route[29, 9], NTUgr [33] and NCTU [21]. Most of them apply FLUTE [19, 20], a rather efficient tool based on look-up table, to generate the Rectilinear Steiner Minimum Tree (RSMT) for each network. FastRoute is of rather high speed and it can be integrated into placement to provide interconnection information. MaizeRoute is implemented with extreme-edge-shift technique, and NTHU

uses the concept of region-based constraint for overflow reduction. For the approach of multi-commodity flow, the global routing problem is formulated and transferred into an integer linear programming (ILP) problem to be solved. A recent router from the work by Albrecht [1] provides an approximation method based on this approach.

#### 3.6 Summary

From the above review, it is shown that some achievements have been made by previous researchers on the topic of routability. Nevertheless, owing to the development of the craft on semiconductors and the enlargement of the integration scale, new requirements on routability have been proposed. Therefore, there are still large space for performance improvement. In congestion estimation, a lot of efficient models have been proposed, such as some predefined patterns for resource assignment and probabilistic analysis. The influence caused by routing procedure still lacks enough concerns. In clock network synthesis and clock gating design, equidistant clock tree and zero skew approach have been developed and improved. Nonetheless, excessive focus on wirelength optimization would deteriorate the tolerance on variability and reduce the robustness of the work. In global routing, recent global routers focused on fast reduction of overflow, but the optimization on wirelength and via connection is partly ignored.

# Chapter 4

# **Congestion Prediction**

# 4.1 Overview

Congestion prediction is of crucial importance in the early stages of the physical design. In this chapter, we propose three congestion models: SMD (shortest Manhattan distance), Detour model [84] and 3-step approach [83]. From the experimental results it is shown that the 3-step approach is the most efficient one considering the accuracy of congestion prediction.

# 4.2 Problem Formulation

Congestion modeling is an important part of interconnect estimation during the floorplanning and placement stage. Given a packing which is partitioned into  $l_h \times l_w$  tiles (according to the length of tile,  $t_l$ ), we will calculate the net density at each tile according to the congestion model. Net density means the accumulated probability of tracking paths in each tile, which are contributed by all the nets in the chip. Based on the congestion information obtained from the net density, we can evaluate the routability of the packing result. The objective of our work is to minimize the difference between the results of estimation and routing, in order to predict the grade of congestion accurately at early stages of the physical design.

| Table 4.1                                                     | Notations in congestion prediction                               |

|---------------------------------------------------------------|------------------------------------------------------------------|

| Notation                                                      | Description                                                      |

| $t_l$                                                         | Length of a tile                                                 |

| $c_{max}^h$                                                   | Maximum horizontal wire capacity inside a tile                   |

| $c_{max}^v$                                                   | Maximum vertical wire capacity inside a tile                     |

| $c_k(r)$                                                      | The number of tiles that is $r$ tiles from the source of net $k$ |

| $DT_k$                                                        | The shortest Manhattan distance between the source and sink of   |

|                                                               | the net $k$                                                      |

| $d_k(x,y)$                                                    | The distance from the source of net $k$ to tile $(x, y)$         |

| $P_k(x,y)$                                                    | A rough estimation of the probability of net $k$ passing through |

|                                                               | the tile $(x, y)$                                                |

| W(x,y)                                                        | The weight of tile $(x, y)$                                      |

| $CF_k$                                                        | Congestion factor of the net $k$                                 |

| $l_d^k$                                                       | Detoured length of the net $k$                                   |

| $E_k(x,y)$                                                    | Probability of net k passing through $(x, y)$                    |

| $E_k^h(x,y)$                                                  | Probability of net k passing through $(x, y)$ horizontally       |

| $E_k^v(x,y)$                                                  | Probability of net k passing through $(x, y)$ vertically         |

| $E^h(x,y)$                                                    | Expected number of wires passing through $(x, y)$ horizontally   |

| $E^v(x,y)$                                                    | Expected number of wires passing through $(x, y)$ vertically     |

| $A^h(x,y)$                                                    | Actual number of wires passing through $(x, y)$ horizontally,    |

|                                                               | obtained from global routing result                              |

| $A^v(x,y)$                                                    | Actual number of wires passing through $(x, y)$ vertically,      |

|                                                               | obtained from global routing result                              |

| $\left(s_{k}^{x},s_{k}^{y} ight)$                             | Coordinate of the source tile of net $k$                         |

| $(t_k^x, t_k^y)$                                              | Coordinate of the terminal tile of net $k$                       |

| $\frac{(s_k^x, s_k^y)}{(t_k^x, t_k^y)}$ $\frac{T_k^d}{T_k^d}$ | The set of extra tiles when the detoured nets pass through       |

|                                                               | outside the bounding box of net $k$                              |

| $T_k$                                                         | The set of tiles inside the bounding box of net $k$              |

| $T_k(d)$                                                      | The set of tiles inside the bounding box of net $k$ ,            |

|                                                               | being $d$ tiles away from the source                             |

# 4.3 Analysis of Congestion Models

In the previous works regarding congestion prediction, we usually break down the multi-pin nets into 2-pin nets first. A network with N pins can be decomposed into N - 1 subnets, each subnet is a connection of two pins. In this section, we mainly propose three models of congestion prediction. All of them are constructed based on 2-pin subnets decomposition. Respective principal analysis and performance comparison are listed. These models are SMD, Detour and 3-step approach, which are discussed as follows.

## 4.4 SMD Model

When we assume that all the nets are routed in their shortest Manhattan distances, the tiles within the smallest bounding box of net k can be divided into  $DT_k - 1$  divisions where  $DT_k$  is the shortest Manhattan distance between the source and sink of net k. An example is shown in figure 4.1. The tiles are divided into three divisions  $D_1$ ,  $D_2$  and  $D_3$ . Intuitively, if the nets are restricted to be routed within the bounding box with the shortest Manhattan distance, the nets will pass through exactly one tile in each division of the corresponding smallest bounding box. Instead of assuming that the probability of each possible route is the same, we propose a new congestion model, SMD model, assuming that a net will pass through the tiles in the same division with the similar probability. Thus, all the tiles that have the same distance from the source or sink of a net k will have the same probability of being passed through by net k.

Let  $s_k(x, y)$  denote the distance from the source of net k to tile (x, y). The tiles having the same distance from the source of net k will be grouped in the same division. Let  $c_k(r)$  be the number of tiles that is r tiles from the source of net k. Hence, the probability of net k passing through (x, y),  $P_k(x, y)$ , can

be calculated by the following equation:

$$P_k(x,y) = \frac{1}{c_k(d_k(x,y))}$$

(4.1)

In addition, a net may pass through a tile either horizontally or vertically. When a net is routed from the upper-left corner to the lower-right corner of the bounding box, the net may pass through a tile with a path as shown in figure 4.2. If the tile is on the boundary of the bounding box, the route may pass through the tile in two ways. The four different cases of the tile lying along the top, the left, the bottom and the right boundary are shown in figure 4.2a. If the tile is on the left or right (at the top or bottom) of the bounding box, the length of the route passing through the tile horizontally (vertically) is  $\frac{0.5t_l}{2}$ and the length of the route passing through the tile vertically (horizontally) is  $\frac{1.5t_l}{2}$ . If a tile is not on the boundary of the bounding box, the net may pass through the tile in four different ways. They are shown in figure 4.2b. In this case, the length of the route passing through the tile horizontally or vertically is  $\frac{2t_l}{4}$ . Thus, we can calculate  $E_k^h(x, y)$  and  $E_k^v(x, y)$  by the following equations:

$$E_{k}^{h}(x,y) = \begin{cases} \frac{3 \times E_{k}(x,y)}{4} & : y = s_{k}^{y} \text{ or } y = t_{k}^{y}(x \neq s_{k}^{x} \text{ and } x \neq t_{k}^{x}) \\ \frac{E_{k}(x,y)}{4} & : x = s_{k}^{x} \text{ or } x = t_{k}^{x}(y \neq s_{k}^{y} \text{ and } y \neq t_{k}^{y}) \\ \frac{E_{k}(x,y)}{2} & : \text{ others} \end{cases}$$

(4.2a)

$$E_{k}^{v}(x,y) = \begin{cases} \frac{E_{k}(x,y)}{4} & : y = s_{k}^{y} \text{ or } y = t_{k}^{y}(x \neq s_{k}^{x} \text{ and } x \neq t_{k}^{x}) \\ \frac{3 \times E_{k}(x,y)}{4} & : x = s_{k}^{x} \text{ or } x = t_{k}^{x}(y \neq s_{k}^{y} \text{ and } y \neq t_{k}^{y}) \\ \frac{E_{k}(x,y)}{4} & : x = s_{k}^{x} \text{ or } x = t_{k}^{x}(y \neq s_{k}^{y} \text{ and } y \neq t_{k}^{y}) \end{cases}$$

(4.2b)

$$\frac{E_{k}(x,y)}{2} & : \text{ others} \end{cases}$$

Finally, the expected number of wires passing through (x, y) horizontally and vertically,  $E^{h}(x, y)$   $(E^{v}(x, y))$ , can be calculated by following equations:

$$E^{h}(x,y) = \sum_{\text{all net } k} E^{h}_{k}(x,y)$$

(4.3a)

$$E^{v}(x,y) = \sum_{\text{all net } k} E^{v}_{k}(x,y)$$

(4.3b)

## 4.5 Detour Model

The congestion models discussed before assume that all nets are routed in their shortest Manhattan distances. However, the congestion model can be more accurate when we consider net routing without this assumption. This is reasonable as it is nearly impossible to route all the nets in their shortest Manhattan distances for any large circuit. In this section, we will also propose a new congestion model (called Detour model [84]) in which each net is not necessarily routed in its shortest Manhattan distance. Detour model is proposed based on the SMD model. It assumes that a route may have detours.

#### 4.5.1 Estimation of Detoured length

| Test    | Percentage of detoured nets $(\%)$ |        |        |  |  |  |  |  |

|---------|------------------------------------|--------|--------|--|--|--|--|--|

| Cases   | R1                                 | R2     | R3     |  |  |  |  |  |

| hp      | 11.232                             | 8.664  | 6.432  |  |  |  |  |  |

| apte    | 17.75                              | 16.363 | 10.713 |  |  |  |  |  |

| ami33   | 8.794                              | 6.432  | 3.804  |  |  |  |  |  |

| ami49   | 15.747                             | 10.633 | 5.452  |  |  |  |  |  |

| playout | 0.389                              | 0.256  | 0.081  |  |  |  |  |  |

Table 4.2 Percentage of detoured nets

In this section, we show how to estimate the congestion of the tiles when nets may detour. Obviously, the nets may detour only when some locations of the packings are very congested. We perform global routing on the packings to illustrate the percentage of detoured nets under different routing environments. The experimental results are shown in table 4.2. We can see that if the packing is more congested, more nets may detour. Thus, we can first use SMD model to evaluate the congestion of the packing and calculate the congestion factor of each net k by following equation:

$$CF_{k} = \sum_{(x,y)\in T} \frac{2 \times (E^{h}(x,y) - E^{h}_{k}(x,y) + E^{v}(x,y) - E^{v}_{k}(x,y))}{|s_{x}^{k} - t_{x}^{k}| + 1 \times |s_{y}^{k} - t_{y}^{k}| + 1} \times |c_{max}^{k} - c_{max}^{k}| + 1 \times |s_{y}^{k} - t_{y}^{k}| + 1$$

$$(4.4)$$

where  $s_x^k \le x \le t_x^k$  and  $s_y^k \le y \le t_y^k$ .

From the equation, we can see that if  $CF_k$  is larger than one, it means that the bounding box is very congested for net k and the net k may likely detour. Thus, we can estimate the length of detour of net k by the following equation (if  $l_d^k$  is smaller than zero, it is adjusted to zero):

$$l_d^k = \lfloor (CF_k - 1) \times DT_k \rfloor \tag{4.5}$$

Table 4.3 Improvement of wirelength estimation

| Test Cases | Actual wirelength | Estimated wirelength | RMST            |

|------------|-------------------|----------------------|-----------------|

| hp         | 1091.10(0.00%)    | 1079.44(1.56%)       | 1068.80(2.18%)  |

| apte       | 1888.24(0.00%)    | 1873.92(1.01%)       | 1846.60(2.3%)   |

| ami33      | 2065.78(0.00%)    | 2054.18(0.61%)       | 2039.90(1.25%)  |

| ami49      | 3127.44(0.00%)    | 3028.04(3.17%)       | 2940.30(5.38%)  |

| playout    | 12307.02(0.00%)   | 12305.78(0.06%)      | 12304.50(0.06%) |

We have performed global routing on the packings to verify the estimation of detoured length. The experimental results are shown in table 4.3. From the experiments, we can see the error between our estimated wirelength (the multipin nets are decomposed into 2-pins nets by rectilinear minimum spanning tree first) and the actual wirelength by global routing is always smaller than the error between the wirelength of rectilinear minimum spanning tree (RMST) and the actual wirelength. It means that we can always estimate the wirelength more accurately by using congestion factor.

#### 4.5.2 Congestion Estimation

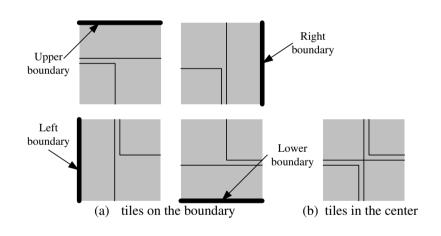

As the detoured nets may pass through outside the bounding box, some extra tiles may be passed through by those nets. These extra tiles are the tiles when the detoured nets pass through outside the bounding box of net k with detoured length less than  $l_d^k$ . First, we define  $T_k^d$  as those extra tiles for a net k. In real cases,  $P_k(x, y)$  for  $(x, y) \in T_k^d$  will depend on the location of the congestion area. Detours happen because of some random over-congested tiles. Because of this random situation, it is reasonable to assume that all tiles

| Elemente 4.9 | Datar  |       | f   |   | A      |     |

|--------------|--------|-------|-----|---|--------|-----|

| Figure 4.3   | Detour | model | IOL | а | two-pm | net |

(x, y) in  $T_k^d$  have the same probability. Hence, we can build the congestion map based on SMD model. An example is shown in figure 4.3.

The detoured net may often pass through outside the bounding box with less bends. If edge shifting [69] is used, the most common case is that either the whole vertical or horizontal path is outside the bounding box. Thus, either all horizontal segments or all vertical segments are passing through outside the bounding box. In this case, we assume that half of the wirelength of the detoured net will be contributed by the tile in  $T_k^d$ .

The detoured net may often pass through outside the bounding box with less bends. The most common case is that either the whole vertical or horizontal path is outside the bounding box. Thus, we assume that half of the wirelength of the detoured net will be contributed by the tile in  $T_k^d$ . Hence, we can calculate  $P_k(x, y)$  where  $(x, y) \in T_k^d$  by following equation:

$$E_k(x,y) = \frac{DT_k + l_d^k}{2 \times |T_k^d|} : (x,y) \in T_k^d$$

(4.6)

where  $|T_k^d|$  is the number of tiles in  $T_k^d$

Hence, we can calculate  $E_k(x, y)$  of other tiles (for any  $(x, y) \notin T_k^d$ ) that inside the bounding box following equation:

$$E_k(x,y) = \frac{1 - c * |T_k^d|_{s_k(x,y)}}{c_k(s_k(x,y))}$$

(4.7)

where  $|T_k^d|_{s_k(x,y)}$  is the number of tiles in same diagonal of the division  $s_k(x,y)$ and c is  $E_k(x,y)$  for any  $(x,y) \in T_k^d$ . In addition, a net may pass through a tile either horizontally or vertically. We will calculate  $E_k^h(x,y)$  and  $E_k^v(x,y)$ by equation 4.2.

# 4.6 3-Step Approach

The estimation process is divided into three steps: preliminary estimation, detailed estimation and congestion redistribution. To avoid over-estimating congestion, we perform a preliminary estimation step first to determine which regions are likely to be over-congested. A region should be more attractive to net routing if it is less congested. Then, we will make use of this information to predict the congestion measures during the detailed estimation step. We use a SMD model described in section 4.4 because of its simplicity and experimental results have shown that this model can give accurate estimations. Finally, congestion redistribution will be performed to simulate the rip-up and reroute operations of the detailed routing step by moving wires from over-congested regions to less congested regions. We use a 3-step approach [83] as follows:

- Preliminary Estimation: We estimate the congestion measure at each tile roughly according to the bounding box of each net so that we can determine which regions are likely to be over-congested.

- Detailed Estimation: Based on the information obtained from the preliminary estimation step, we estimate the congestion measure at each tile by using a diagonal-based congestion model.

• Congestion Redistribution: We will simulate the rip-up and reroute process of the routing stage by moving wires from over-congested tiles to less congested tiles.

#### 4.6.1 Preliminary Estimation

In practice, we will choose to route a net over the tiles that are less congested to prevent overflow. It means that some tiles are more attractive to net routing and some tiles are less. However, this fact is usually ignored in traditional congestion models. In our approach, a preliminary estimation of the congestion map will be performed to obtain this information. If a rough estimation of the congestion measure of a tile, P(x, y), is above the maximum wire capacity, the tile (x, y) will be less attractive to net routing. On the other hand, if P(x, y) is well below the maximum wire capacity, the tile (x, y) will be more attractive to net routing. We will make use of these P(x, y) values to improve the accuracy of the detailed estimation step.

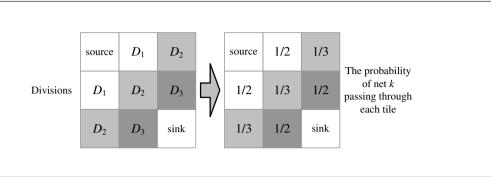

In this preliminary estimation step, we assume that all the tiles inside the bounding box of a net k,  $T_k$ , have the same probability,  $P_k(x, y)$ , of being passed through by net k. In addition, we assume that the nets can be routed in their shortest Manhattan distances. The wirelength and the area of the bounding box can be computed as  $|t_k^x - s_k^x| + |t_k^y - s_k^y| + 1$  and  $(|t_k^x - s_k^x| + 1) \times (|t_k^y - s_k^y| + 1)$  respectively.  $P_k(x, y)$  can thus be calculated by the following equation:

$$P_k(x,y) = \frac{|t_k^x - s_k^x| + |t_k^y - s_k^y| + 1}{(|t_k^x - s_k^x| + 1) \times (|t_k^y - s_k^y| + 1)}$$

(4.8)

We can then obtain a preliminary estimation by adding up the congestion measures due to different nets:

$$P(x,y) = \sum_{\text{all } k} P_k(x,y) \tag{4.9}$$

#### 4.6.2 Detailed Estimation

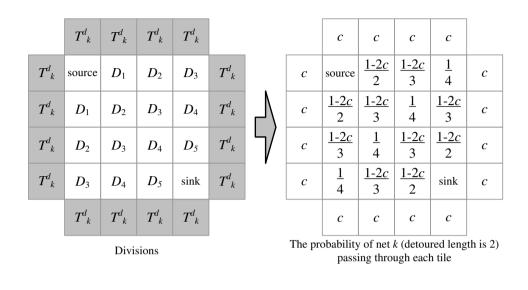

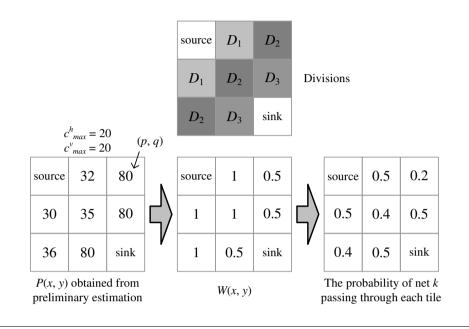

In our approach, we will predict the congestion measures by using a diagonal (orthogonal to the source-sink connection) based model during the detailed estimation step. We first assume that all the nets are routed in their shortest Manhattan distances. The tiles inside the smallest bounding box of net k can be divided into  $DT_k - 1$  divisions where  $DT_k$  is the shortest Manhattan distance between the source and the sink. An example is shown in figure 4.4.

In this example, the tiles are divided into three divisions  $D_1$ ,  $D_2$  and  $D_3$ . Intuitively, if the net is restricted to be routed within the bounding box, the net will pass through exactly one tile in each division. We assume that the net will pass through the tiles in the same division with probabilities weighted according to W(x, y) where W(x, y) is computed by the following equations according to the P(x, y) obtained in the preliminary estimation step. Chapter 4 Congestion Prediction

$$W(x,y) = \begin{cases} 1 & : P(x,y) < (c_{max}^{h} + c_{max}^{v}) \\ \frac{c_{max}^{h} + c_{max}^{v}}{P(x,y)} & : \text{ otherwise} \end{cases}$$

(4.10)

If P(x, y) is smaller than the sum of  $c_{max}^h$  and  $c_{max}^v$ , the tile (x, y) is unlikely to be over-congested and so W(x, y) is 1. If P(x, y) is larger than the sum of  $c_{max}^h$  and  $c_{max}^v$ , that tile should have a smaller W(x, y) when P(x, y) is larger. It reflects the case in the routing stage that the nets will be routed to pass through less congested tiles. Hence, the probability of net k passing through  $(x, y), E_k(x, y)$ , can be calculated according to the weight of each tile, W(x, y), by the following equation:

$$E_k(x,y) = \frac{W(x,y)}{\sum_{(i,j)\in T_k(d_k(x,y))} W(i,j)}$$

(4.11)

In the example of figure 4.4,  $c_{max}^h$  and  $c_{max}^v$  are 20. When we focus on division  $D_2$ , (p,q) the tile at the upper right corner is a congested tile according to the preliminary estimation step because P(p,q) is 80, which is larger than the sum of  $c_{max}^h$  and  $c_{max}^v$ . Thus, W(p,q) should be smaller than 1 and it is computed as 0.5 according to equation 4.10. Hence, the probability of net kpassing through (p,q),  $E_k(p,q)$ , is 0.2. It is smaller than the others in the same division because the tile (p,q) is likely to be over-congested. In addition, a net may pass through a tile either horizontally or vertically. We will calculate  $E_k^h(x,y)$  and  $E_k^v(x,y)$  by equation 4.2.

#### 4.6.3 Congestion Redistribution

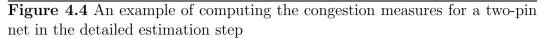

In real routing, if some tiles are over-congested or some nets cannot be routed, rip-up and reroute will be performed. In our approach, we perform congestion redistribution to achieve the same purpose of moving wires from over-congested tiles to less congested tiles. We will only move around those congestion measures within the same diagonal (division). In this case, we may simulate the routing process when less congested path is always selected and the total congestion of one division can be maintained at one. An example is shown in figure 4.5. In  $T_k(1)$  of net k, the tile with congestion estimation 7.2 is the most congested in this division but it is not over-congested (less than the maximum wire capacity of a tile). Thus, no action will be taken. In  $T_k(2)$ , the tile with 12.4 is the most congested in this division and is over-congested. Thus, we will move 0.2 (net k's contribution to the congestion measure of this tile) from this tile to the least congested tile of the same division.

In general, we will find the tile,  $(x_m, y_m)$ , with the maximum vertical (horizontal) congestion and the tile,  $(x_l, y_l)$ , with the minimum vertical (horizontal) congestion from each division of all the nets. If the tile with the maximum vertical (horizontal) congestion is over-congested, we will move  $E_k^v(x_m, y_m)$   $(E_k^h(x_m, y_m))$  from  $(x_m, y_m)$  to  $(x_l, y_l)$ . After redistribution, the summation of  $E_k^v(x, y)$   $(E_k^h(x, y))$  in the same division still equals one. Thus, the assumption that each net will pass through exactly one tile in each division within the bounding box still holds.

# 4.7 Experimental Results

In the experiments, the test cases used are the ISPD-02 suite circuits [36]. The length of a tile,  $t_l$ , is  $40\mu m$ . The detailed information of the testing circuits are shown in table 4.4. Our prediction models are robust approaches with no inclusion of circuit-oriented parameter tuning. Therefore, the performance of our work should be consistently good based on the packing results from various placers. In our experiments, all the circuits are first placed using a wirelength driven placer, Capo [5]. Four placement solutions are obtained for each test case. Global routing is then performed on each placement solution by a maze routing based global router [44]. During global routing, we set wiring capacity value to simulate two environments: more congested and less congested cases. For the data sets shown in table 4.5, there are about 0% - 2% over-congested tiles after global routing. Different congestion models are then used to estimate the congestion of the placed circuits and their estimations are then compared with the actual congestion measures obtained from the global router.

| Test Cases | No. of Cells | No. of Nets | No. of 2-pin Nets | No. of Tiles     |

|------------|--------------|-------------|-------------------|------------------|

| ibm01      | 12506        | 14111       | 36455             | $57 \times 57$   |

| ibm02      | 19342        | 19584       | 61615             | $82 \times 82$   |

| ibm03      | 22853        | 27401       | 66172             | $89 \times 87$   |

| ibm04      | 27220        | 31970       | 73889             | $85 \times 86$   |

| ibm05      | 28146        | 28446       | 97862             | $60 \times 60$   |

| ibm06      | 32332        | 34826       | 93366             | $81 \times 82$   |

| ibm07      | 45639        | 48117       | 127522            | $97 \times 97$   |

| ibm08      | 51023        | 50513       | 154377            | $104 \times 103$ |

| ibm09      | 53110        | 60902       | 161186            | $118 \times 118$ |

| ibm10      | 68685        | 75196       | 222371            | $194 \times 189$ |

| ibm11      | 70152        | 81454       | 199332            | $130 \times 129$ |

| ibm12      | 70439        | 77240       | 240520            | $171 \times 171$ |

| ibm13      | 83709        | 99666       | 257409            | $141 \times 141$ |

| ibm14      | 147088       | 152772      | 394044            | $151 \times 151$ |

| ibm15      | 161187       | 186606      | 529215            | $170 \times 169$ |

| ibm16      | 182980       | 190048      | 588775            | $204 \times 203$ |

| ibm17      | 184752       | 189581      | 670455            | $182 \times 182$ |

| ibm18      | 210341       | 201920      | 617777            | $163 \times 163$ |

| Table 4.4 Information | on of the test cases |